# **SIEMENS**

# ICs for Communications ISDN Subscriber Access Controller for $U_{pn}$ -Interface Terminals

SmartLink-P PSB 2197

User's Manual 02.95

| PEB 2197<br>Revision |              | Original Version: 02.95     |  |

|----------------------|--------------|-----------------------------|--|

| Previous F           | Releases:    |                             |  |

| Page                 | Subjects (cl | nanges since last revision) |  |

|                      |              |                             |  |

#### **Data Classification**

#### Maximum Ratings

Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit.

#### Characteristics

The listed characteristics are ensured over the operating range of the integrated circuit. Typical characteristics specify mean values expected over the production spread. If not otherwise specified, typical characteristics apply at  $T_A = 25$  °C and the given supply voltage.

#### **Operating Range**

In the operating range the functions given in the circuit description are fulfilled.

For detailed technical information about "**Processing Guidelines**" and "**Quality Assurance**" for ICs, see our "**Product Overview**".

| Table of C | Contents                                                         | Page |

|------------|------------------------------------------------------------------|------|

| 1          | Features                                                         | 6    |

| 1.1        | Pin Definitions and Functions                                    | 8    |

| 1.2        | Logic Symbol                                                     | 14   |

| 1.3        | Functional Block Diagram                                         | 17   |

| 1.4        | System Integration                                               | 20   |

| 1.4.1      | Low Cost Digital Telephone Using the SmartLink-P                 | 20   |

| 1.4.2      | Low Cost Digital Feature Phone Using the SmartLink-P             | 21   |

| 1.4.3      | U <sub>pn</sub> -Terminal Repeater                               | 22   |

| 1.4.4      | Network Termination Module                                       | 23   |

| 1.4.5      | S/T-Interface Option                                             |      |

| 1.4.6      | HDLC-Controller on IOM®-2 Extensions                             | 25   |

| 2          | Functional Description                                           | 26   |

| 2.1        | Terminal Equipment (TE) Mode                                     | 26   |

| 2.1.1      | General Functions and Device Architecture (TE-mode)              | 26   |

| 2.1.2      | Clock Generation (TE-Mode)                                       | 28   |

| 2.1.3      | Interfaces (TE-Mode)                                             | 29   |

| 2.1.3.1    | Microcontroller Interface                                        | 29   |

| 2.1.3.2    | IOM®-2 Interface in TE-Mode                                      | 38   |

| 2.1.3.3    | Upn-Interface                                                    |      |

| 2.1.4      | D-Channel-Arbitration in TE-Mode                                 | 50   |

| 2.1.5      | HDLC-Controller                                                  | 52   |

| 2.1.6      | Terminal Specific Functions                                      |      |

| 2.1.6.1    | LCD-Contrast Control                                             |      |

| 2.1.6.2    | Ring Tone Generation                                             |      |

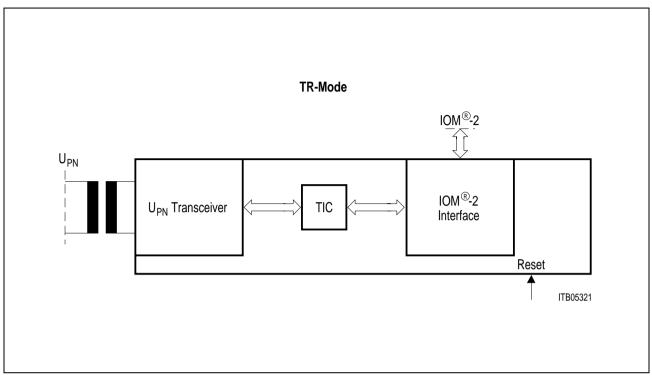

| 2.2        | Terminal Repeater (TR) Mode                                      |      |

| 2.2.1      | General Functions and Device Architecture (TR-Mode)              |      |

| 2.2.2      | Clock Generation (TR-Mode)                                       |      |

| 2.2.3      | Interfaces (TR-Mode)                                             |      |

| 2.2.3.1    | IOM®-2 Interface in TR-Mode                                      |      |

| 2.2.3.2    | Upn-Interface in TR-Mode                                         |      |

| 2.2.4      | D-Channel-Arbitration in TR-Mode                                 |      |

| 2.2.5      | Reset                                                            |      |

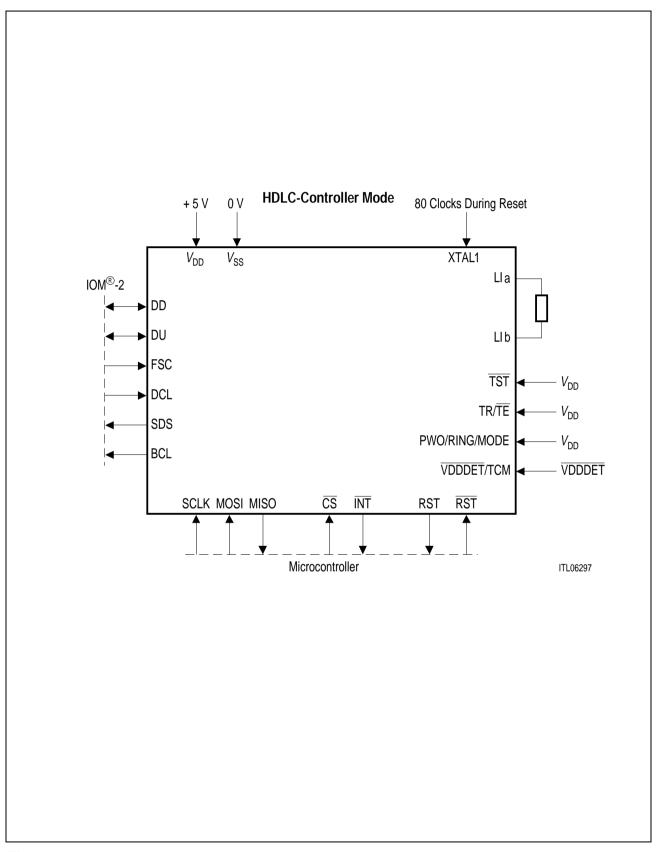

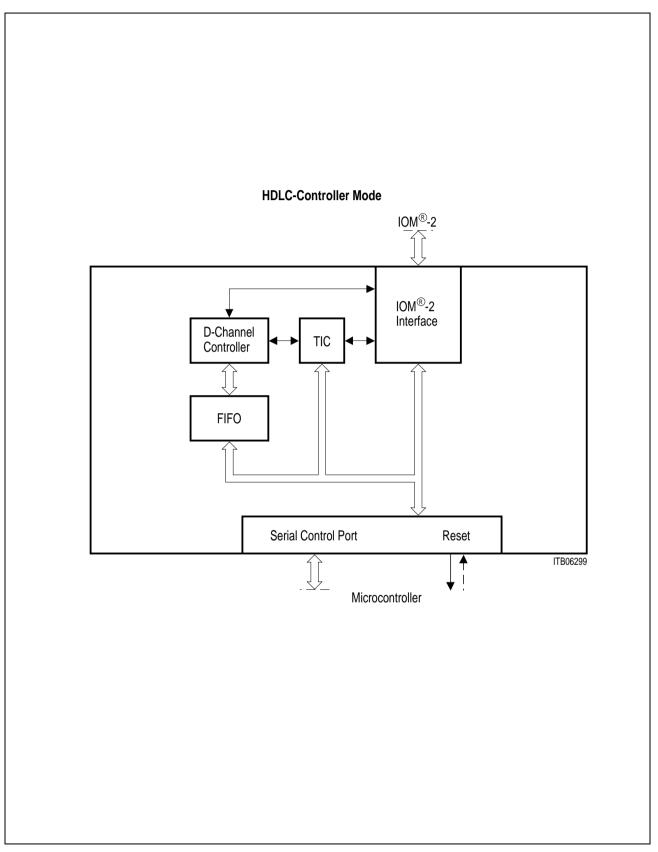

| 2.3        | HDLC-Controller Mode                                             |      |

| 2.3.1      | General Functions and Device Architecture (HDLC-Controller Mode) |      |

| 2.3.2      | Clock Generation (HDLC-Controller Mode)                          | 64   |

| 2.3.3      | Interfaces (HDLC-Controller Mode)                                | 64   |

| 2.3.3.1    | Microcontroller Interface                                        |      |

| 2.3.3.2    | IOM®-2 Interface in HDLC-Controller Mode                         |      |

| 2.3.4      | D-Channel-Arbitration in HDLC-Controller Mode                    | 66   |

| 2.3.5      | HDLC-Controller                                                  | 66   |

| 2.3.6      | Reset                                                            | 66   |

| Table of C | contents                                        | Page |

|------------|-------------------------------------------------|------|

| 3          | Operational Description                         | 67   |

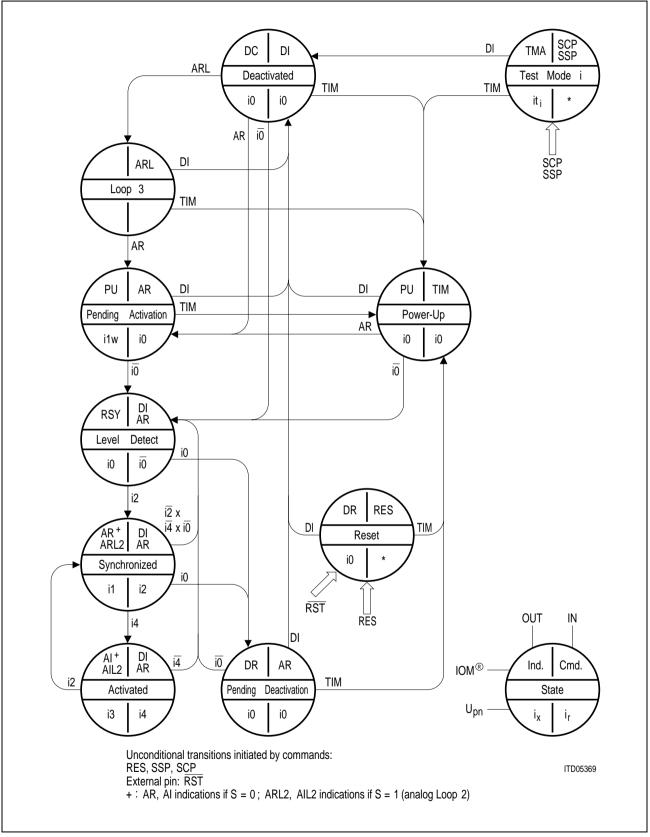

| 3.1        | TE-Mode                                         | 67   |

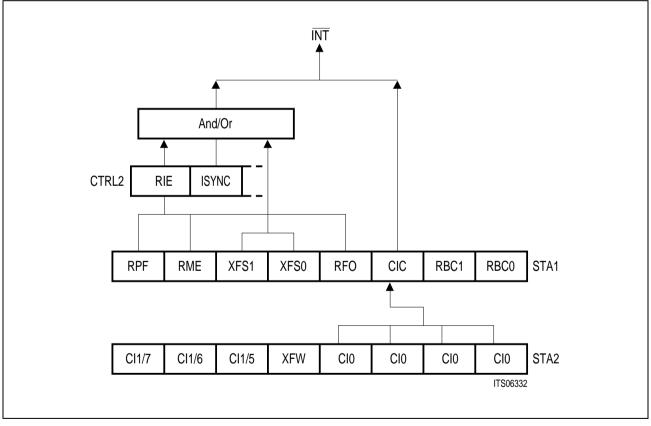

| 3.1.1      | Interrupt Structure and Logic                   | 67   |

| 3.1.2      | Control of the Upn-Transceiver                  | 68   |

| 3.1.2.1    | Power-Down of the IOM®-2 Interface              | 68   |

| 3.1.2.2    | Activation/Deactivation of the Upn-Interface    |      |

| 3.1.2.3    | Layer-1 Command/Indication Codes in TE-Mode     |      |

| 3.1.2.4    | State Diagrams                                  |      |

| 3.1.2.5    | TE-Mode State Description                       |      |

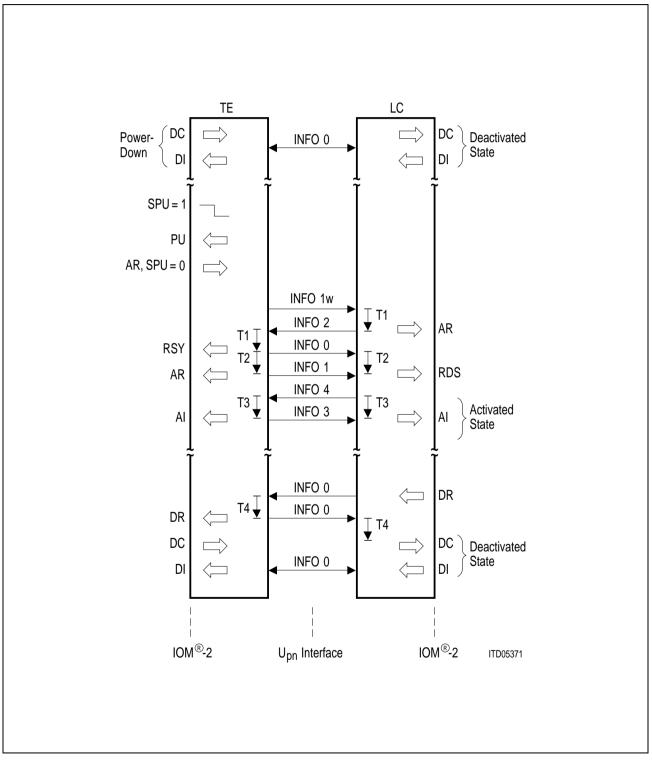

| 3.1.2.6    | Example of the Activation/Deactivation          |      |

| 3.1.3      | Operation of the Serial Control Interface       |      |

| 3.1.4      | Control of the HDLC-Data Transfer               |      |

| 3.1.4.1    | HDLC-Transmitter                                |      |

| 3.1.4.2    | HDLC-Receiver                                   |      |

| 3.1.4.3    | Examples for the HDLC-Controller Operation      |      |

| 3.1.5      | Reset                                           |      |

| 3.1.6      | Initialization                                  |      |

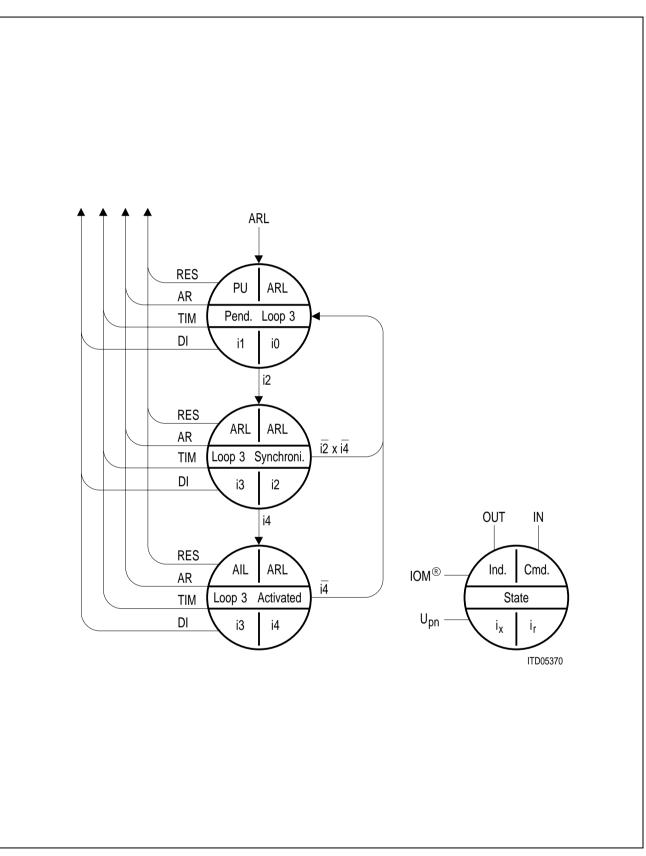

| 3.2        | TR-Mode                                         |      |

| 3.2.1      | Control of the Upn-Transceiver                  |      |

| 3.2.1.1    | Activation/Deactivation of the IOM®-2 Interface |      |

| 3.2.1.2    | Layer-1 Command/Indication Codes in TR-Mode     |      |

| 3.2.1.3    | State Diagrams                                  |      |

| 3.2.1.4    | TR-Mode State Description                       |      |

| 3.2.1.5    | Example of the Activation/Deactivation          |      |

| 3.2.2      | D-Channel Access Procedure                      |      |

| 3.3        | HDLC-Controller Mode                            |      |

| 3.3.1      | Interrupt Structure and Logic                   |      |

| 3.3.2      | Control of the Serial Control Interface         |      |

| 3.3.3      | Control of the HDLC-Data Transfer               |      |

| 3.3.4      | Control of Terminal Specific Functions          |      |

| 3.3.5      | Reset                                           | .104 |

| 4          | Register Description                            | 105  |

| 4.1        | SmartLink-P Register Summary                    |      |

| 5          | Electrical Characteristics                      | 119  |

| 6          | Package Outlines                                | 130  |

IOM<sup>®</sup>, IOM<sup>®</sup>-1, IOM<sup>®</sup>-2, SICOFI<sup>®</sup>, SICOFI<sup>®</sup>-2, SICOFI<sup>®</sup>-4, SICOFI<sup>®</sup>-4µC, SLICOFI<sup>®</sup>, ARCOFI<sup>®</sup>, ARCOFI<sup>®</sup>-BA, ARCOFI<sup>®</sup>-SP, EPIC<sup>®</sup>-1, EPIC<sup>®</sup>-S, ELIC<sup>®</sup>, IPAT<sup>®</sup>-2, ITAC<sup>®</sup>, ISAC<sup>®</sup>-S, ISAC<sup>®</sup>-S, TE, ISAC<sup>®</sup>-P, ISAC<sup>®</sup>-P, TE, IDEC<sup>®</sup>, SICAT<sup>®</sup>, OCTAT<sup>®</sup>-P, QUAT<sup>®</sup>-S are registered trademarks of Siemens AG.

MUSAC<sup>™</sup>-A, FALC<sup>™</sup>54, IWE<sup>™</sup>, SARE<sup>™</sup>, UTPT<sup>™</sup>, ASM<sup>™</sup>, ASP<sup>™</sup> are trademarks of Siemens AG.

Purchase of Siemens I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C-system provided the system conforms to the I<sup>2</sup>C specifications defined by Philips. Copyright Philips 1983.

#### Introduction

The PSB 2197, SmartLink-P, implements the subscriber access functions for a digital terminal to be connected to a two-wire  $U_{pn}$ -interface.

The PSB 2197 SmartLink-P is an optimized device for TE-applications, covering the complete layer-1 and basic layer-2 functions for digital terminals.

The PSB 2197 SmartLink-P combines the functions of the  $U_{pn}$ -transceiver with reduced loop length (one channel of the OCTAT<sup>®</sup>-P PEB 2096) and a simple HDLC-controller for signaling data onto one chip.

A pulse width modulator is included to provide an LCD-contrast control or a ring tone signal.

The serial control port of the SmartLink-P is compatible to most serial interfaces of microcontrollers. In addition it provides the microcontroller clock signal as well as an undervoltage detector and reset generation including a watchdog function.

The Terminal Repeater function of the SmartLink-P allows to cascade two telephones which are controlled by one  $U_{pn}$ -interface from the line card or to extend the loop length by using an IEC-Q transceiver.

The SmartLink-P can also be used as a simple HDLC-controller which provides the TIC-bus access procedure. In this mode, the  $U_{pn}$ -transceiver is inactive.

The PSB 2197 SmartLink-P interfaces to voice/data devices via the IOM<sup>®</sup>-2 interface and provides an additional bit clock and strobe signal for standard codecs. The upstream B-channel information may be muted or loop back the downstream data.

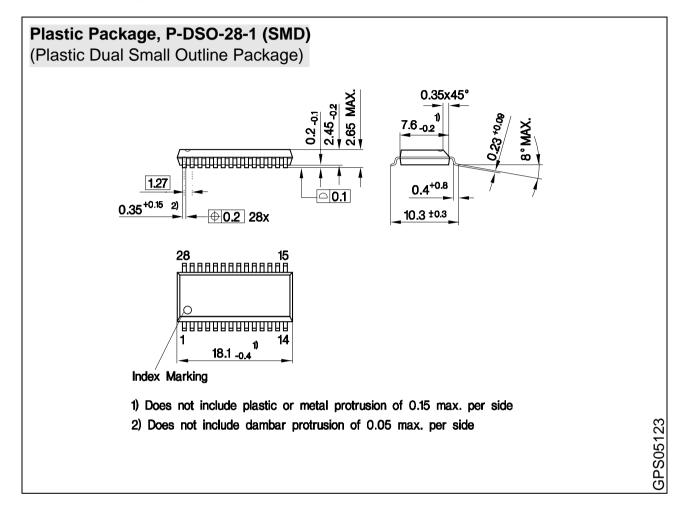

The PSB 2197 SmartLink-P is a 1-micron CMOS device offered in a P-DSO-28 package. It operates from a single 5-V supply.

Note:  $U_{pn}$  in the document refers to a version of the  $U_{p0}$ -standard with a reduced loop length.

# SIEMENS

## ISDN Subscriber Access Controller for U<sub>pn</sub>-Interface Terminals (SmartLink-P)

## **Preliminary Data**

#### 1 Features

- Cost/performance-optimized U<sub>pn</sub>-interface transceiver, compatible to PEB 2096 OCTAT-P and PSB 2195 ISAC<sup>®</sup>-P or PSB 2196 ISAC<sup>®</sup>-P TE

- HDLC-controller with  $2 \times 4$  byte FIFO per direction

- IOM<sup>®</sup>-2 interface for terminal application including bit clock and strobe signal

- Uplink MUTE function

- Selective B-channel loop back

- Serial control port

- Pulse width output LCD-contrast control or ring tone generation

- CPU-clock and reset output

- Watchdog timer

- Test loops

- Advanced CMOS-technology

- Low power consumption: active: 100 mW max.

| Туре      | Ordering Code | Package          |

|-----------|---------------|------------------|

| PSB 2197T | Q67100-H6462  | P-DSO-28-1 (SMD) |

**PSB 2197**

**CMOSIC**

6

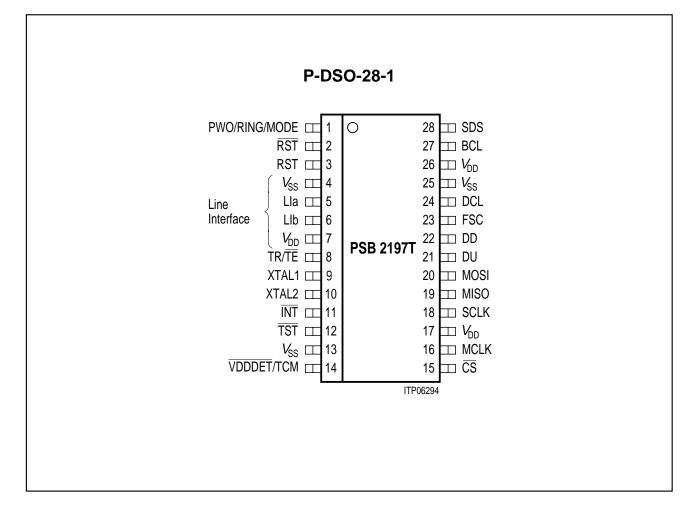

#### **Pin Configurations**

(top view)

#### 1.1 Pin Definitions and Functions

| Pin<br>No. | TE-                         | Mode                                          | TR-Mode                  |                                               | Con                 | )LC-<br>troller<br>ode                        |                                                                                                                                         |

|------------|-----------------------------|-----------------------------------------------|--------------------------|-----------------------------------------------|---------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| P-DSO-28   | Symbol                      | Input (I)<br>Output (O)<br>Open Drain<br>(OD) | Symbol                   | Input (I)<br>Output (O)<br>Open Drain<br>(OD) | Symbol              | Input (I)<br>Output (O)<br>Open Drain<br>(OD) | Function                                                                                                                                |

| 15         | CS                          | 1                                             | टङ                       | I                                             | CS                  | I                                             | Chip Select. A low<br>level indicates a<br>microprocessor<br>access to the<br>SmartLink-P. It masks<br>the INT-output.                  |

| 11         | INT                         | OD                                            | INT                      | OD                                            | INT                 | OD                                            | Interrupt Request.<br>INT becomes active if<br>the SmartLink-P<br>requests an interrupt.<br>INT is masked by CS.                        |

| 16         | MCLK                        | 0                                             | 0, low                   | 0                                             | 0, low              | 0                                             | Microprocessor<br>Clock. Clock output<br>for the microcontroller.                                                                       |

| 3          | RST                         | 0                                             | inv.<br>RST              | 0                                             | inv.<br>RST         | 0                                             | <b>Reset.</b> High active<br>reset output. In TR-<br>mode and HDLC-<br>controller mode, RST<br>outputs the inverse of<br>the RST-input. |

| 2          | RST                         | I/O (OD)                                      | RST                      | 1                                             | RST                 | 1                                             | <b>Reset.</b> Low active<br>reset output and input<br>(TE, open drain), low<br>active reset input in<br>TR-mode.                        |

| 8          | TR/TE<br>(V <sub>SS</sub> ) | 1                                             | $\frac{TR/TE}{(V_{DD})}$ | 1                                             | TR/TE<br>$(V_{DD})$ | 1                                             | Terminal Repeater/<br>TE-Mode Selection.<br>Selects terminal<br>repeater mode $(V_{DD})$ or<br>TE-mode $(V_{SS})$ .                     |

| Pin<br>No. | TE-      | Mode                                          | TR       | -Mode                                         | Con      | DLC-<br>troller<br>ode                        |                                                                                                                                                                                                      |

|------------|----------|-----------------------------------------------|----------|-----------------------------------------------|----------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P-DSO-28   | Symbol   | Input (I)<br>Output (O)<br>Open Drain<br>(OD) | Symbol   | Input (I)<br>Output (O)<br>Open Drain<br>(OD) | Symbol   | Input (I)<br>Output (O)<br>Open Drain<br>(OD) | Function                                                                                                                                                                                             |

| 20         | MOSI     | 1                                             | MOSI     | 1                                             | MOSI     | 1                                             | Master Out Slave In.<br>Receive data line of the<br>serial control interface.<br>Operates only as slave.                                                                                             |

| 19         | MISO     | 0                                             | MISO     | 0                                             | MISO     | 0                                             | Master In Slave Out.<br>Transmit data line of<br>the serial control<br>interface. Operates<br>only as slave. MISO is<br>tristate while CS is<br>high.                                                |

| 18         | SCLK     | I                                             | SCLK     | I                                             | SCLK     | I                                             | Serial Clock. Clock<br>signal of the serial<br>control interface.                                                                                                                                    |

| 22<br>21   | DD<br>DU | I/O (OD)<br>I/O (OD)                          | DD<br>DU | I/O (OD)<br>I/O (OD)                          | DD<br>DU | I/O (OD)<br>I/O (OD)                          | Data Downstream.<br>Data Upstream.<br>Transfer the data of the<br>IOM-2 interface.<br>External pull-up<br>resistors in the range of<br>$4.7  \Omega \text{ to } 820 \Omega \text{ are}$<br>required. |

| Pin<br>No. | TE-I   | Mode                                          | TR     | -Mode                                         | Cont   | DLC-<br>troller<br>ode                        |                                                                                                                                                                                                                                                                                                                                         |

|------------|--------|-----------------------------------------------|--------|-----------------------------------------------|--------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P-DSO-28   | Symbol | Input (I)<br>Output (O)<br>Open Drain<br>(OD) | Symbol | Input (I)<br>Output (O)<br>Open Drain<br>(OD) | Symbol | Input (I)<br>Output (O)<br>Open Drain<br>(OD) | Function                                                                                                                                                                                                                                                                                                                                |

| 9          | XTAL1  | 0                                             | XTAL1  | 0                                             | XTAL1  | 0                                             | <b>Crystal 1.</b> Connection<br>for a crystal or used as<br>external clock input.<br>For HDLC-controller<br>mode XTAL1 requires<br>a clock signal of at<br>least 80 clock periods<br>after reset.<br><b>Crystal 2.</b> Connection<br>for a crystal. Not<br>connected if an<br>external clock is<br>supplied on XTAL1.<br>(TE & TR-mode) |

| 24         | DCL    | 0                                             | DCL    | I                                             | DCL    | 1                                             | Data Clock. IOM-<br>interface clock signal.<br>Clock frequency is<br>twice the IOM-data<br>rate.<br>TE: clock output<br>IOM-2: 1536 kHz<br>TR, HDLC: clock input<br>IOM-2: 1536 kHz                                                                                                                                                     |

| 23         | FSC    | 0                                             | FSC    | 1                                             | FSC    | 1                                             | Frame Sync.<br>TE: Frame synchroni-<br>zation output.<br>High during IOM-<br>channel 0 on the IOM-2<br>interface.<br>TR, HDLC: Input syn-<br>chronization signal<br>IOM-2 mode.                                                                                                                                                         |

| Pin<br>No. | TE-I         | Mode                                          | TR          | Mode                                          | Cont        | DLC-<br>troller<br>ode                        |                                                                                                                                                                                           |

|------------|--------------|-----------------------------------------------|-------------|-----------------------------------------------|-------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P-DSO-28   | Symbol       | Input (I)<br>Output (O)<br>Open Drain<br>(OD) | Symbol      | Input (I)<br>Output (O)<br>Open Drain<br>(OD) | Symbol      | Input (I)<br>Output (O)<br>Open Drain<br>(OD) | Function                                                                                                                                                                                  |

| 5<br>6     | Lla<br>Llb   | I/O<br>I/O                                    | Lla<br>Llb  | I/O<br>I/O                                    | Lla<br>Llb  | I/O<br>I/O                                    | Line Interface a.<br>Line Interface b.<br>$U_{pn}$ -transceiver<br>signals. In<br>HDCL-controller mode<br>both pins must be<br>connected via a 10 k $\Omega$<br>resistor.                 |

| 27         | BCL          | 0                                             | 0, low      | 0                                             | BCL         | 0                                             | <b>Bit Clock.</b><br>IOM-bit clock signal<br>(768 kHz) in TE- and<br>HDLC-controller mode<br>if programmed by<br>SDS-bits. In TR-mode,<br>the default value of<br>CTRL4 fixes BCL to '0'. |

| 28         | SDS          | 0                                             | 0, low      | 0                                             | SDS         | 0                                             | Serial Data Strobe.<br>Strobe signal to<br>indicate 64 kbit/s<br>time-slot in TE- and<br>HDLC-mode. In<br>TR-mode, the default<br>value of CTRL4 fixes<br>SDS to '0'.                     |

| 1          | PWO/<br>RING | 0                                             | HDLC/<br>TR | 1                                             | HDLC/<br>TR | 1                                             | Pulse Width<br>Output/Ring/Mode.<br>Provides the output of<br>the pulse width<br>modulator or ring tone<br>generator.<br>Selects between<br>HDLC-(1) and TR-(0)<br>mode if TR/TE = 1.     |

| Pin<br>No.   | TE-Mode      |                                               | TR-Mode         |                                               | Con             | DLC-<br>troller<br>ode                        |                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|--------------|-----------------------------------------------|-----------------|-----------------------------------------------|-----------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P-DSO-28     | Symbol       | Input (I)<br>Output (O)<br>Open Drain<br>(OD) | Symbol          | Input (I)<br>Output (O)<br>Open Drain<br>(OD) | Symbol          | Input (I)<br>Output (O)<br>Open Drain<br>(OD) | Function                                                                                                                                                                                                                                                                                                                                                         |

| 14           | VDDDET       | 1                                             | тсм             | 1                                             | VDDDET          | 1                                             | <b>VDDDET/T-Channel</b><br><b>Mode.</b><br>In TE- and<br>HDLC-mode, this pin<br>selects if the $V_{DD}$<br>detection is active ('0')<br>and reset pulses are<br>generated or whether<br>it is deactivated ('1')<br>and an external reset<br>has to apply on pin<br><b>RST</b> .<br>In TR-mode, TCM is<br>used to select the<br>T-channel source (S/G<br>or '1'). |

| 12           | TST          | 1                                             | TST             | 1                                             | TST             | 1                                             | <b>Test Pin.</b><br>This input is used to<br>select the test mode<br>register via the serial<br>interface. See test<br>mode description. For<br>normal operation, this<br>pin must be tied to high<br>$(V_{DD})$ .                                                                                                                                               |

| 7, 17,<br>26 | $V_{\rm DD}$ |                                               | V <sub>DD</sub> |                                               | V <sub>DD</sub> |                                               | Power Supply<br>(+ 5 V $\pm$ 5 %<br>(U <sub>pn</sub> -specification),<br>$\pm$ 10 % operational).                                                                                                                                                                                                                                                                |

| 4, 13,<br>25 | $V_{\rm SS}$ |                                               | $V_{\rm SS}$    |                                               | V <sub>SS</sub> |                                               | Ground.                                                                                                                                                                                                                                                                                                                                                          |

Please note that pin 4 and pin 7 are the supply pins for the analog drivers Lla/b. They are disconnected internally from the other supply pins except for the ESD-protection circuitry.

To overcome ESD-problems it is necessary to put series resistors in the low voltage output drivers. The resistor value is in range 40 to 50  $\Omega$ . The following output drivers will have these resistors: INT, MCLK, RST, RST, MISO, BCL, SDS, PWO/Ring/MODE. The resistor doesn't affect the high voltage output driver.

The following output drivers will not have the resistors: DD, DU, XTAL2, Lla, Llb.

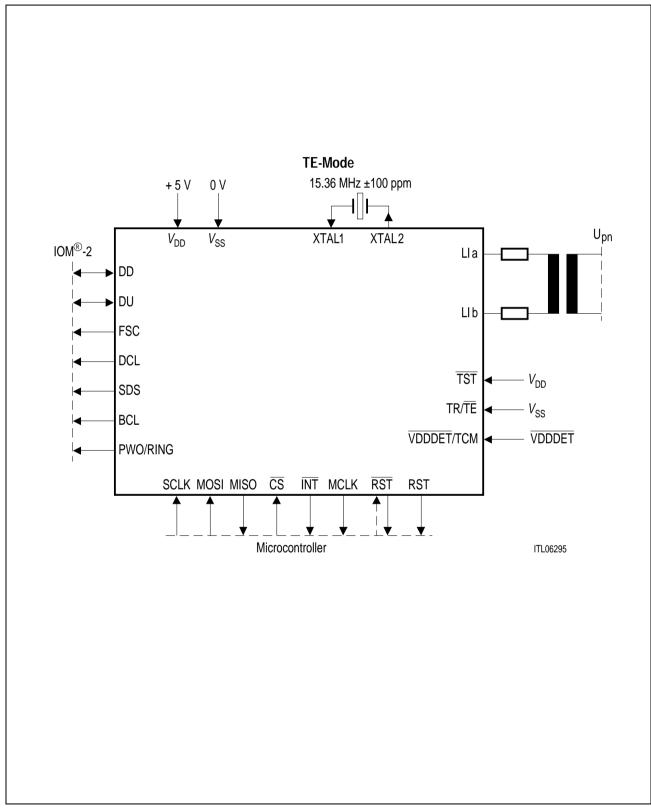

#### 1.2 Logic Symbol

Figure 1 Logic Symbol of the SmartLink-P TE-Mode

# SIEMENS

Features

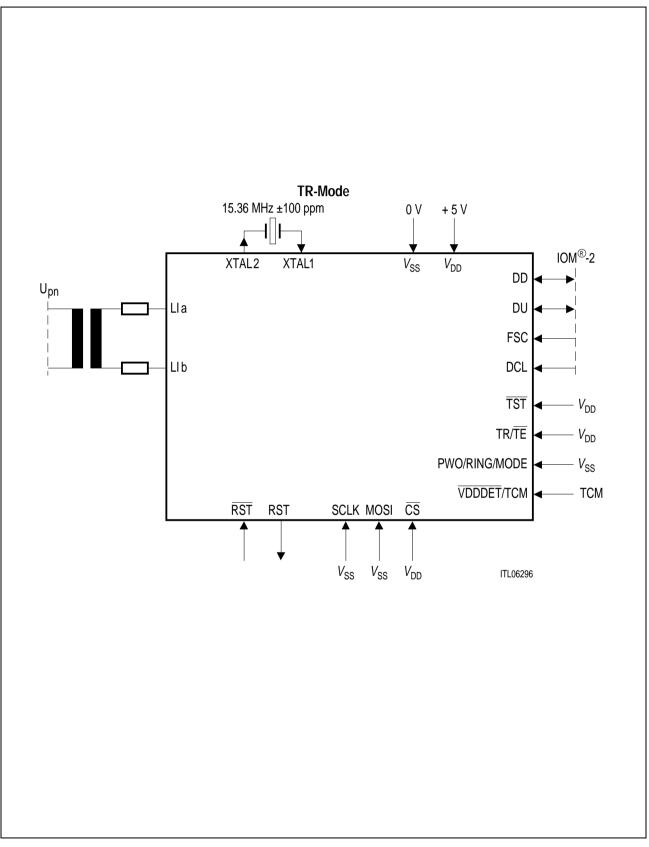

#### Figure 2 Logic Symbol of the SmartLink-P TR-Mode

# SIEMENS

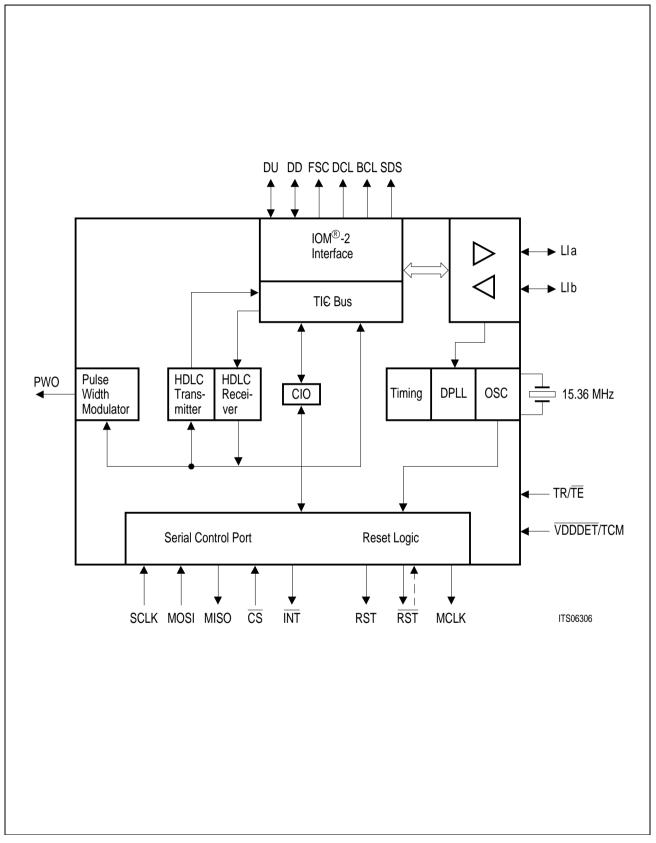

#### 1.3 Functional Block Diagram

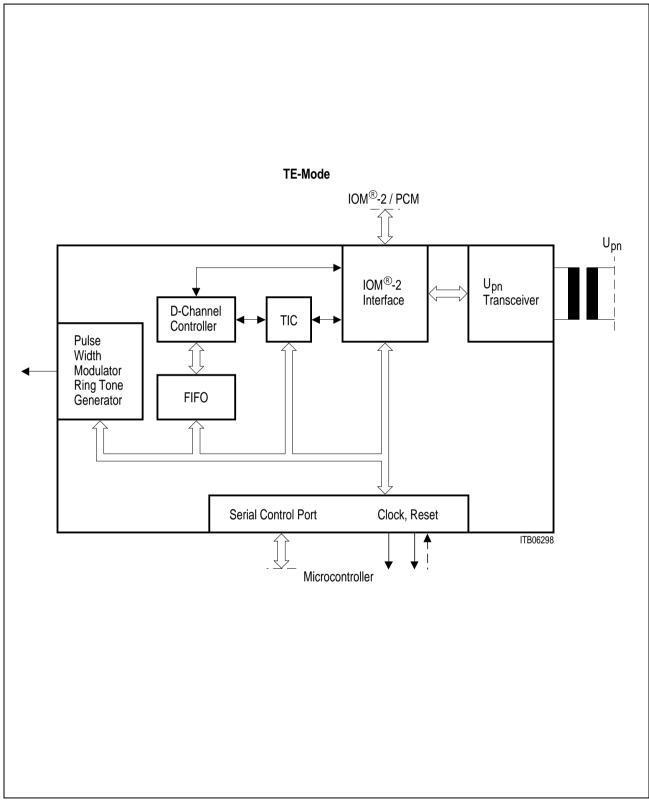

Figure 4 Block Diagram of the SmartLink-P TE-Mode

#### Figure 5 Block Diagram of the SmartLink-P TR-Mode

#### 1.4 System Integration

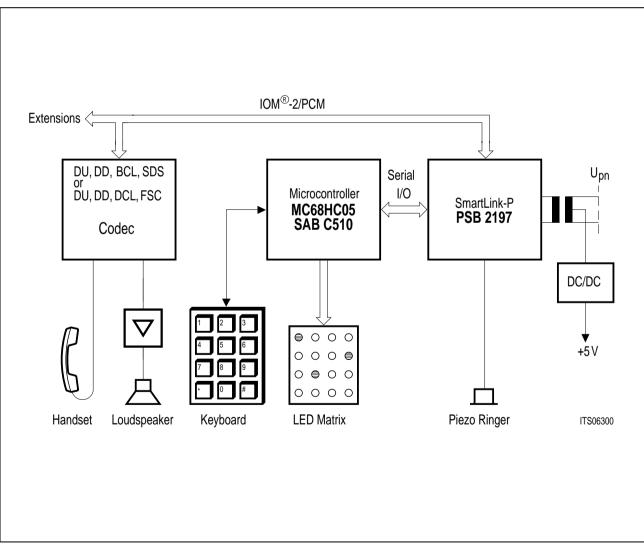

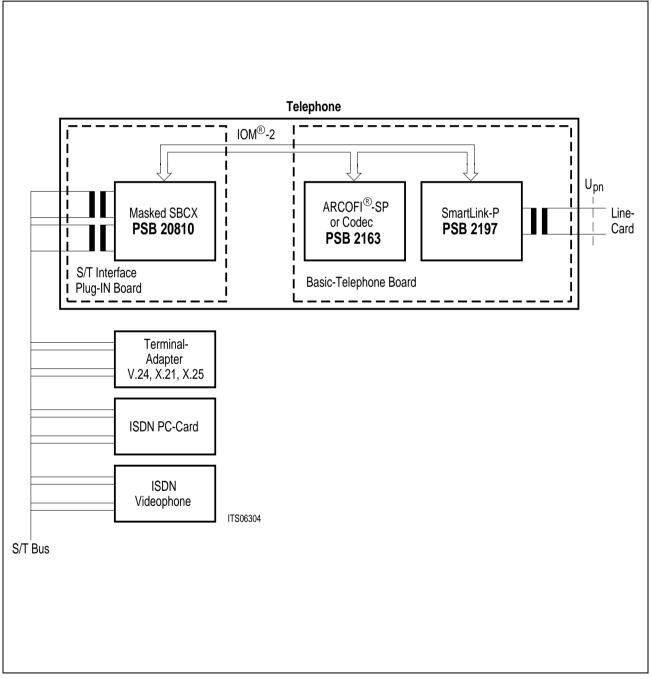

#### 1.4.1 Low Cost Digital Telephone Using the SmartLink-P

A low cost digital telephone behind a PBX consists of the SmartLink-P, a standard codec and a microcontroller with on-chip ROM. This architecture is shown in **figure 7**. The SmartLink-P performs the conversion between the  $U_{pn}$ -interface and the IOM-2 interface of the B-channel and D-channel information. The D-channel signaling information is processed by an HDLC-controller inside the SmartLink-P which provides 2 × 4 byte FIFOs in each direction. The serial strobe signal controls the time-slot which is used by the codec.

A frequency signal generated by the SmartLink-P can be used for ring tone generation. The C510 family of microcontrollers are versions of the standard C501 core enhanced by the synchronous serial interface (SSI).

#### Figure 7 Low Cost Digital Telephone Using the SmartLink-P

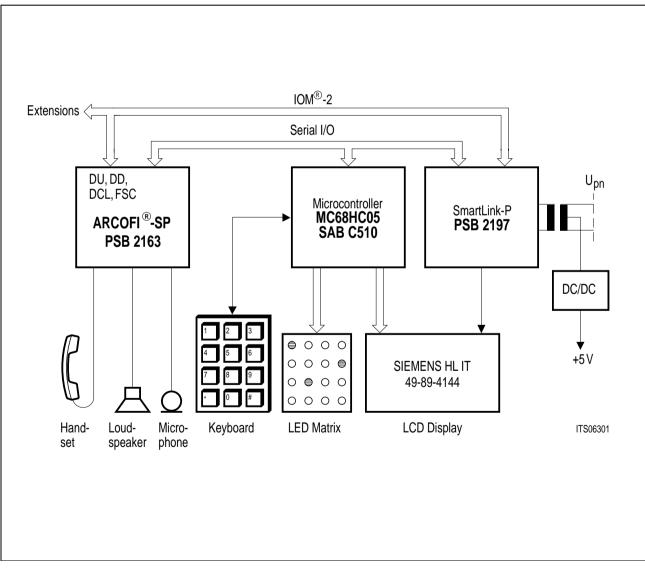

#### 1.4.2 Low Cost Digital Feature Phone Using the SmartLink-P

A low cost digital feature phone behind a PBX consists of the SmartLink-P, a feature codec like the ARCOFI®-SP PSB 2163 and a microcontroller with on-chip ROM. This architecture is shown in **figure 8**. The SmartLink-P performs the conversion between the U<sub>pn</sub>-interface and the IOM-2 interface of the B-channel and D-channel information. The D-channel signaling information is processed by an HDLC-controller inside the SmartLink-P which provides  $2 \times 4$  byte FIFOs in each direction. The parallel microcontroller interface is designed in a way to share the control lines with an LCD-display controller reducing the required number of I/O-lines. A pulse width modulated signal can be used to control the contrast of an LCD-display.

The C510 family of microcontrollers are versions of the standard C501 core enhanced by the synchronous serial interface (SSI).

#### Figure 8 Low Cost Digital Feature Phone Using the SmartLink-P

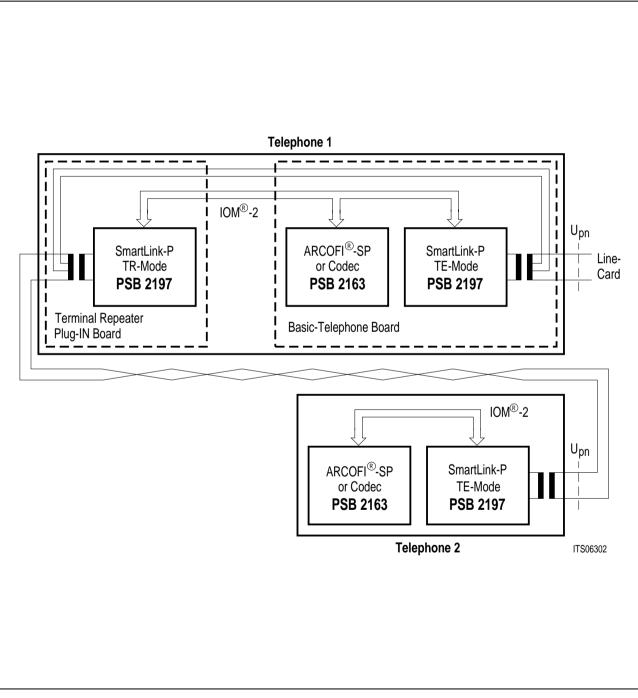

#### 1.4.3 U<sub>pn</sub>-Terminal Repeater

The SmartLink-P is designed to operate as a  $U_{pn}$ -terminal repeater (**figure 9**). It provides a mechanism to control further  $U_{pn}$ -terminals by using the T-channel of the  $U_{pn}$ -interface and the TIC-bus on the IOM-2 interface.

The terminal repeater function allows to cascade two  $U_{pn}$ -telephones up to a loop length of 100 m.

#### Figure 9 U<sub>pn</sub>-Terminal Repeater

Semiconductor Group

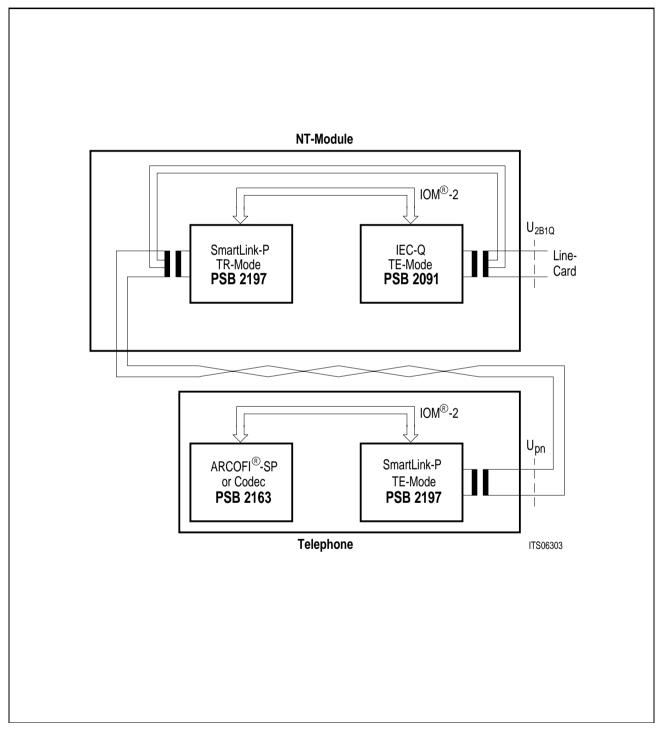

#### 1.4.4 Network Termination Module

The combination of the PEB 2091 (IEC-Q) and PSB 2197 (SmartLink-P) allows the extension of the loop length between the line card and  $U_{pn}$ -terminals up to 8 km. The SmartLink-P provides the regular  $U_{pn}$ -interface to connect standard  $U_{pn}$ -terminals to it.

Figure 10 Network Termination Using the SmartLink-P

#### 1.4.5 S/T-Interface Option

A telephone based on the SmartLink-P may be extended by an S/T-interface option to connect standard S/T-interface terminals like ISDN PC cards or videophones to it (**figure 11**). This option uses a PSB 20810 (mask version of the SBCX, PEB 2081) for the S/T-interface. The D-channel arbitration between the D-channel controller of the SmartLink-P and the upstream D-channel data of the S/T-interface is done by the TIC-bus of the IOM-2 interface.

#### Figure 11 U<sub>pn</sub>-Telephone with S/T-Interface Option

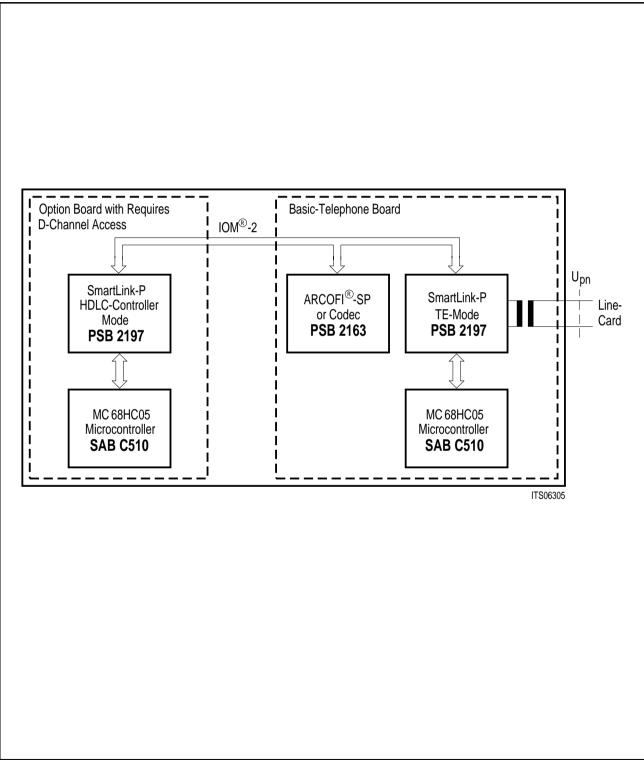

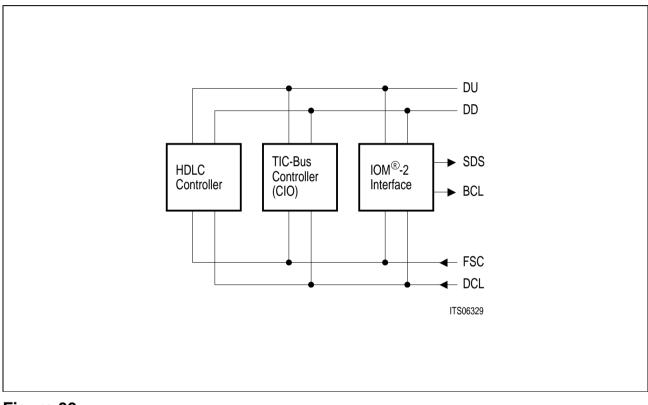

#### 1.4.6 HDLC-Controller on IOM®-2 Extensions

The SmartLink-P can be used as a HDLC-controller to access the D-channel via the TIC-bus procedure. In this mode, the  $U_{pn}$ -interface is not active.

#### Figure 12 HDLC-Controller on IOM<sup>®</sup>-2 Extensions

#### 2 Functional Description

#### Selection between TE-, TR-Mode and HDLC-Controller Mode

The selection between the three operating modes is done via the combination of TR/TE-input and PWO/Ring/Mode input.

If TR/TE is connected to  $V_{ss}$  (GND), the terminal equipment mode is selected. PWO/Ring/Mode operates as output providing the LCD-contrast or ringing signal.

If TR/TE is connected to  $V_{DD}$  (+ 5 V), the PWO/Ring/Mode input selects between TR-mode ('0') and HDLC-controller mode ('1').

The TR-mode remains as a stand-alone function with the requirement that  $\overline{CS}$  must be connected to  $V_{DD}$  and MOSI should be connected to  $V_{SS}$ .

If the HDLC-controller mode is selected, the  $U_{pn}$ -state machine must reach a defined reset state. Therefore it is necessary to provide a clock signal to XTAL1 which is active during reset and remains active at least 80 clock periods after reset. It is recommended to connect the IOM-2 DCL-signal to XTAL1.

#### 2.1 Terminal Equipment (TE) Mode

#### 2.1.1 General Functions and Device Architecture (TE-mode)

Figure 13 depicts the detailed architecture of the PSB 2197 SmartLink-P in TE-mode:

- U<sub>pn</sub>-interface transceiver, functionally fully compatible to both PEB 2095 IBC and PEB 2096 OCTAT-P, also features the terminal repeater mode

- Serial control port

- Reset and microcontroller clock generation

- HDLC-controller with 2 × 4 byte FIFOs per direction

- IOM-2 interface for terminal application

- MUTE function

- B-channel loop on IOM-2

- Pulse width modulator for LCD-contrast control or ring tone generation

- Watchdog timer

# SIEMENS

#### Figure 13 Device Architecture of the SmartLink in TE-Mode

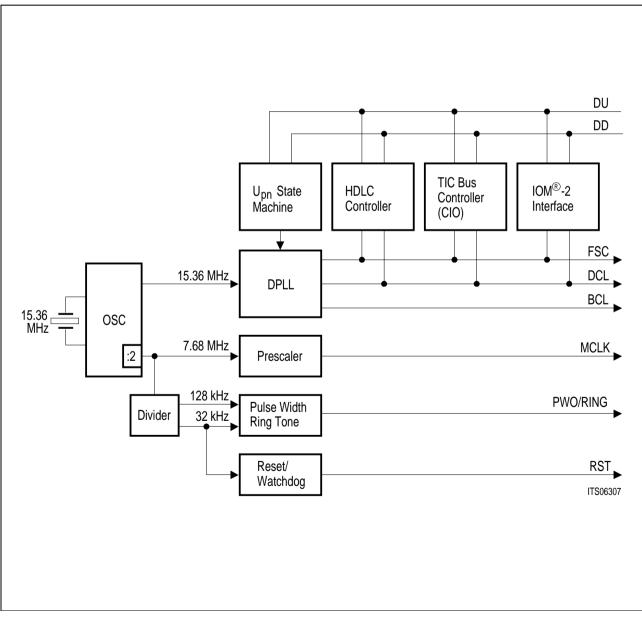

## 2.1.2 Clock Generation (TE-Mode)

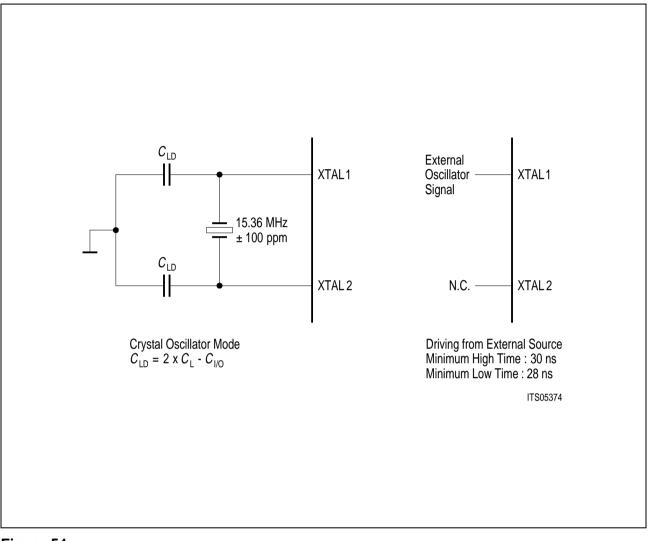

In TE-mode, the oscillator is used to generate a 15.36-MHz clock signal. This signal is used by the DPLL to synchronize the IOM-2 clocks to the received  $U_{pn}$ -frames. The oscillator clock is divided by 2 to generate a 7.68-MHz clock which drives the remaining functions. The prescaler for the microcontroller clock divides the 7.68-MHz clock by 1, 2, 4 or 8. The pulse width modulator and the ring tone generator receive their clock signal from a divider which generates a 128-kHz and 32-kHz signal. The later signal is also used to drive the reset/watchdog counter. Note that only the IOM-2 clock signals (FSC, DCL, BCL) may be stopped during the power-down state. The oscillator and the other modules remain active all the time.

#### Figure 14 Clock Generation in TE-Mode

#### 2.1.3 Interfaces (TE-Mode)

The PSB 2197 SmartLink-P serves four interfaces in TE-mode:

- Serial microcontroller interface for higher layer functions incl. reset and microcontroller clock generation

- IOM-2 interface: between layer-1 and layer-2 and as a universal backplane for terminals

- Upn-interface towards the two-wire subscriber line

- Pulse width modulator/Ringing output

#### 2.1.3.1 Microcontroller Interface

The SmartLink-P provides a serial control interface which is compatible to the SPI-interface of Motorola or Siemens C510 family of microcontrollers.

#### Serial Control Interface

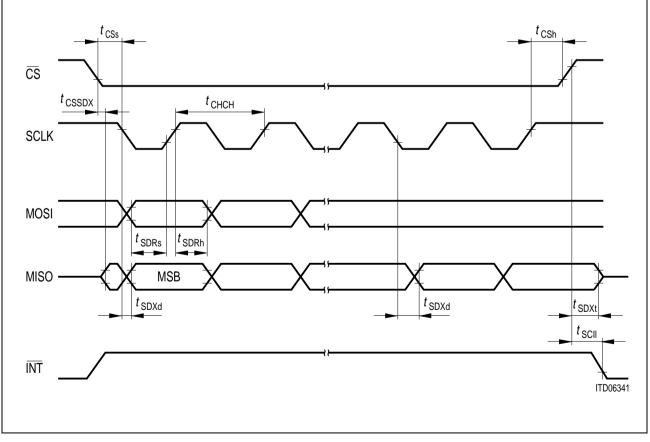

The SmartLink-P is programmable via a serial control interface. It provides access to the D-channel FIFOs as well as global control/status registers. It consists of 5 lines: SCLK, MOSI, MISO, CS, INT.

$\overline{CS}$  is used to start a serial access to the SmartLink-P registers: Following a falling edge on  $\overline{CS}$ , data is transmitted in groups of eight bits until the  $\overline{CS}$ -line becomes inactive.

The data transfer is synchronized by the SCLK-input. MISO changes with the falling edge of SCLK while the contents of MOSI is latched on the rising edge of SCLK. Data is transferred with the MSB first and LSB last.

The structure of the serial control interface is designed to provide a fast full duplex data transfer.

Two control/status bytes are transferred followed by the data of the HDLC FIFOs. Two additional control bytes can be transferred on request.

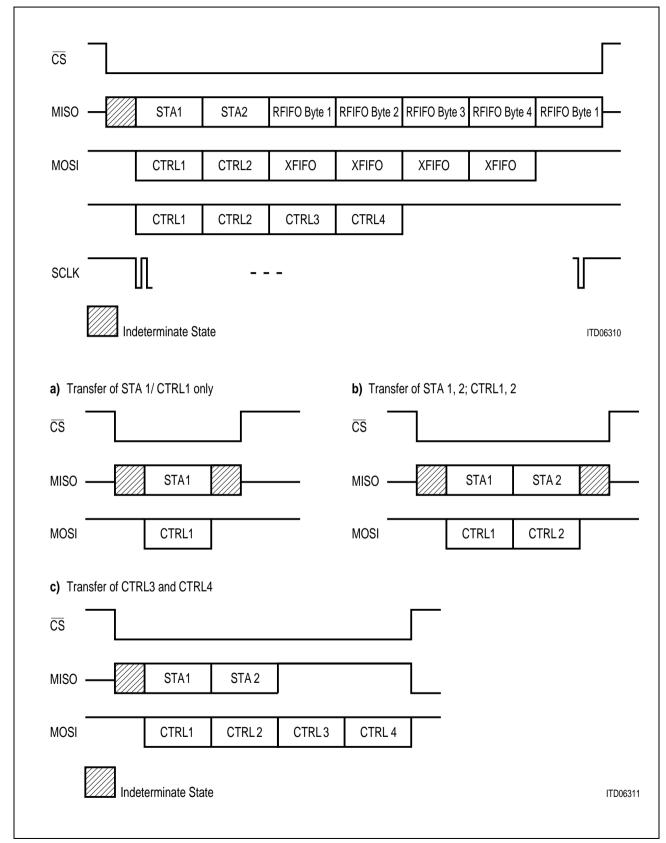

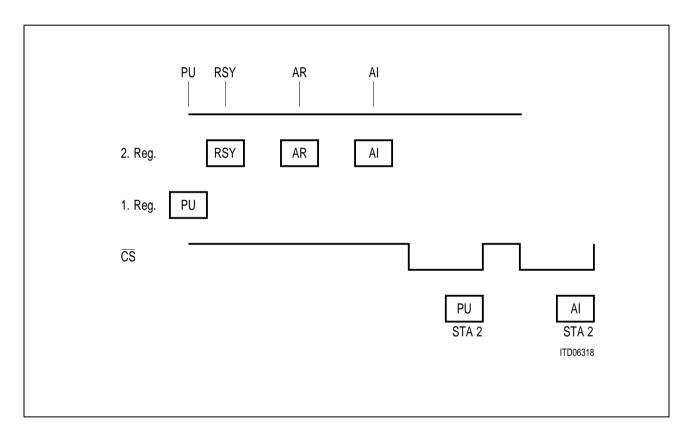

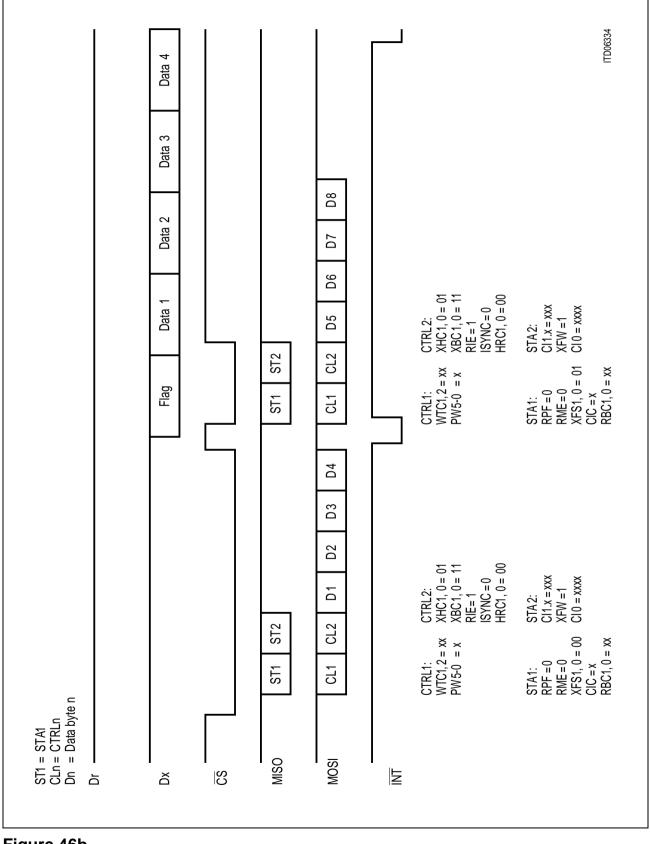

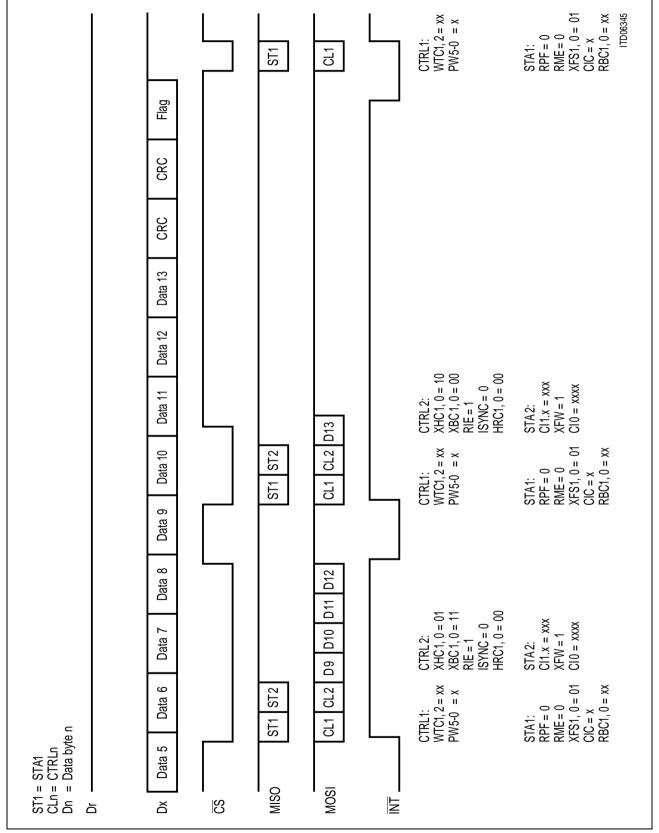

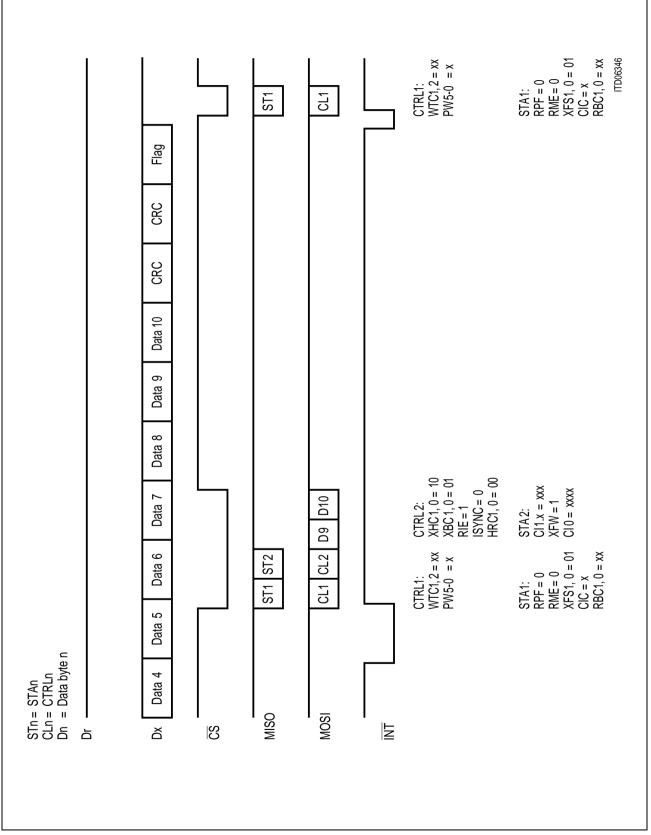

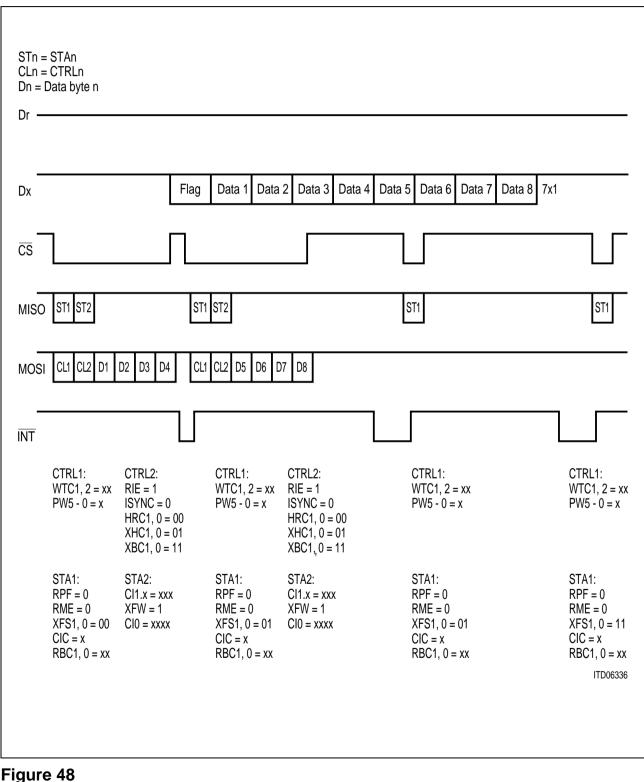

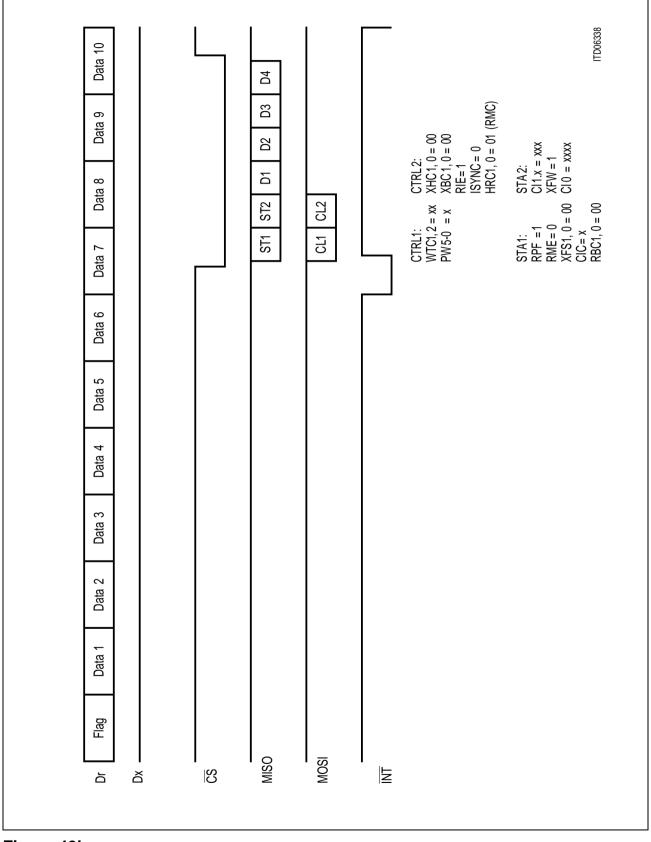

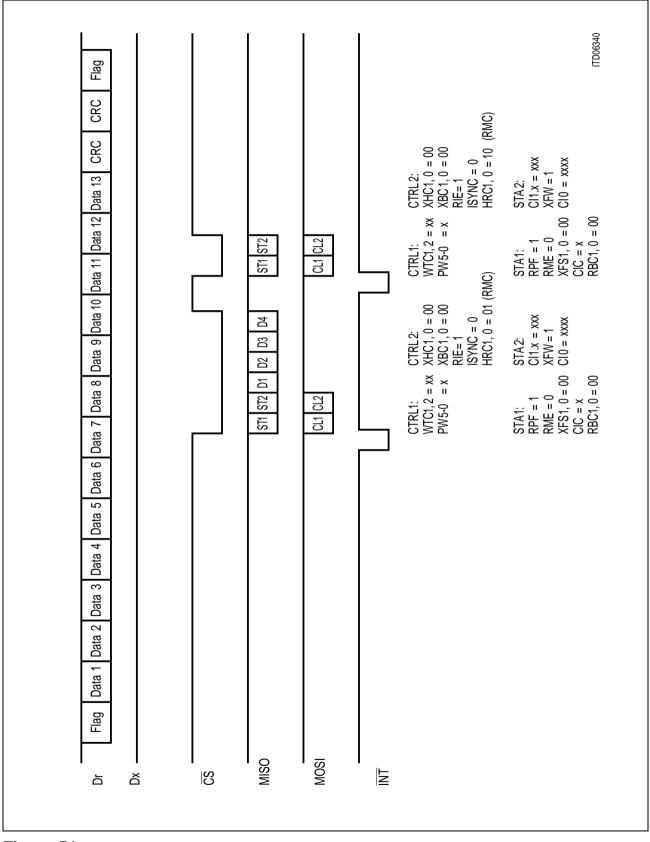

Figure 15 shows the timing of a serial control interface transfer.

#### Figure 15 Serial Control Interface Timing

The serial control port outputs a status byte (STA1) while the first control byte (CTRL1) is received. This status byte informs whether D-channel information follows and about the transmitter status. Following this byte a second status byte (STA2) is transmitted while the second control byte (CTRL2) is received. Following these two bytes, FIFO-data or additional control bytes may be transmitted.

The contents of the RFIFO is transmitted if a receive FIFO-status bit was set (RPF, RME) until a receiver command (RMC, RHR, RMD) has been received. After four bytes have been read, the SmartLink continues to transmit RFIFO data as long as transfers are made (as long as  $\overline{CS}$  is low and clocks are transferred). The contents of the RFIFO will be repeated after 4 bytes. A new FIFO-access continues with the next byte.

The CTRL2 byte specifies the number of bytes which have to be transferred into the XFIFO in receive direction. Additional data bytes will be ignored.

During transfer of CTRL3 and CTRL4, RFIFO data will not be output.

The access to the serial control interface may be stopped at any time by setting the  $\overline{CS}$ -input to '1'. If this happens in the middle of a RFIFO-byte, the information of that byte will be lost. In receive direction, the contents of the shift register will not be written into the XFIFO or the proper register.

If the access is stopped during the transfer of RFIFO-data, the SmartLink will output the remaining number of bytes in the next access, but no RFIFO-status bit will be set. Thus, the microcontroller has to monitor the number of transferred bytes.

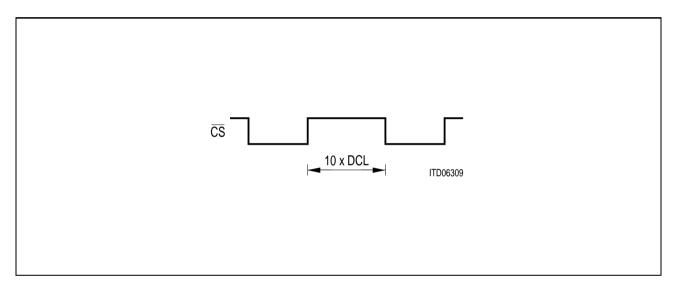

A minimum interval of 10 DCL clock periods ( $6.5 \mu s$ ) is necessary between serial accesses (rising edge of previous access until falling edge of next access). This time is required to perform the commands entered in the CTRL2-register correctly.

An earlier access may result in an incorrect execution of the previous CTRL2-commands.

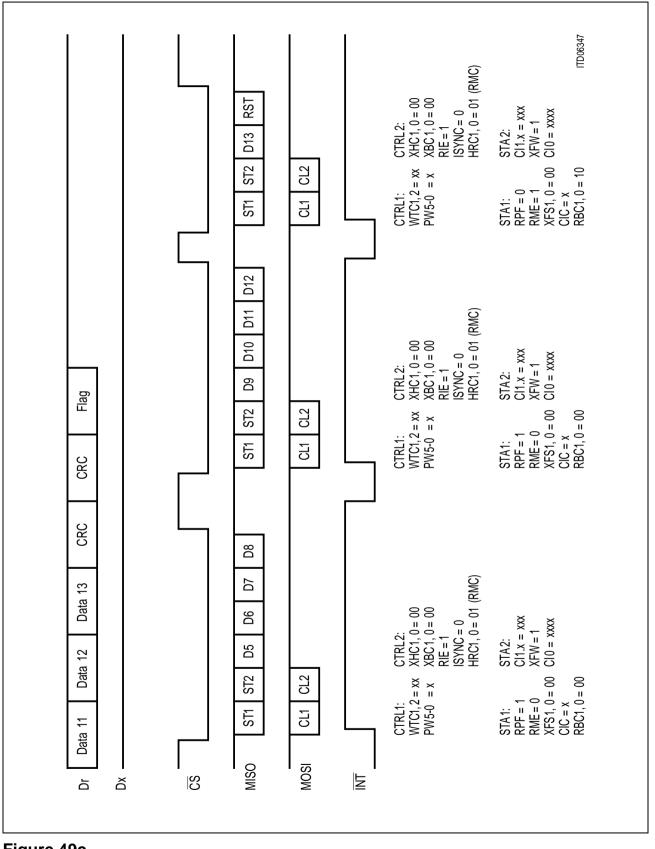

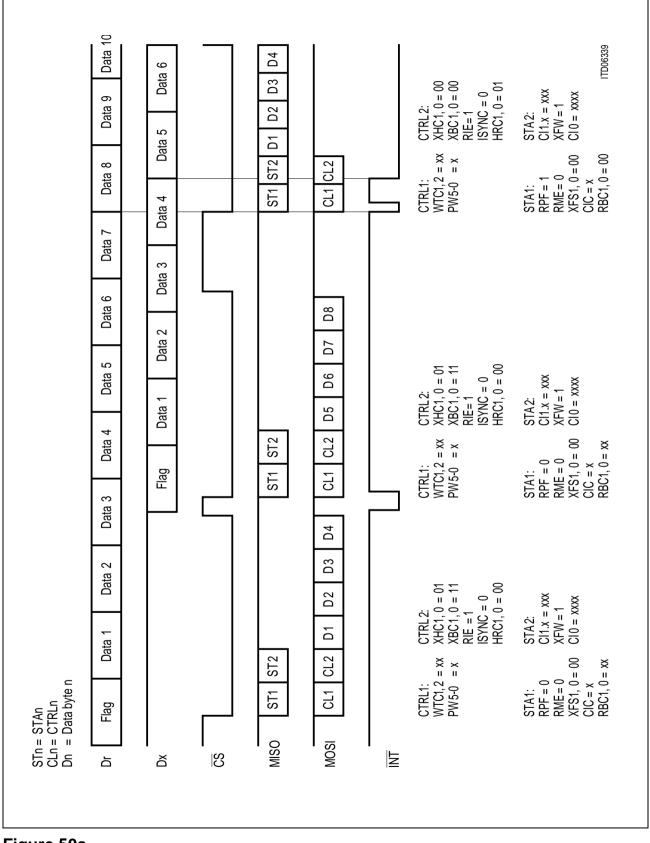

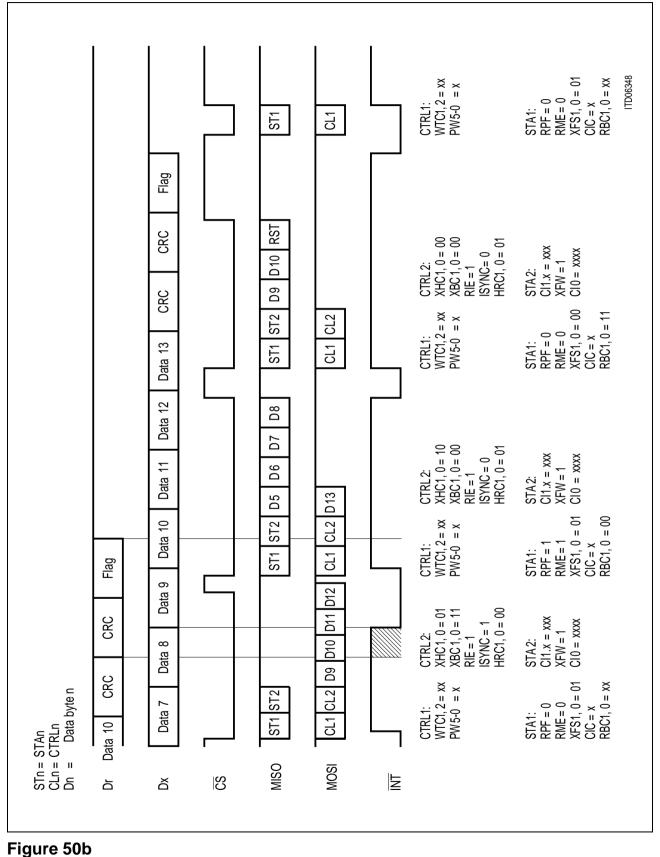

Figure 16 shows some examples of the data transfer over the serial control interface.

#### Figure 16 Examples of SCI-Transfers

# SIEMENS

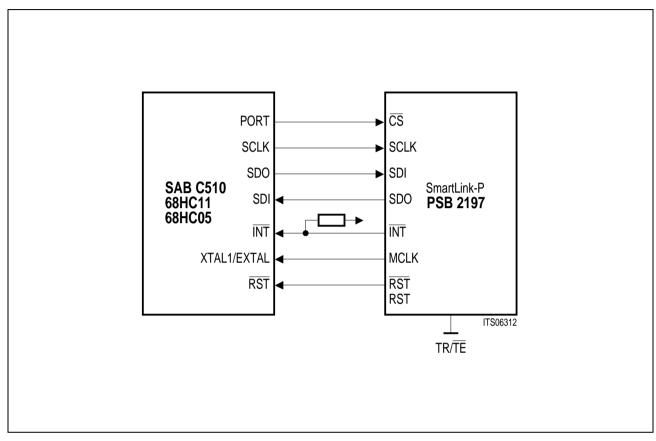

**Figure 17** shows an example how the SmartLink-P is interfaced to a Siemens SAB C510 family of microcontrollers or a Motorola MC68HC05 microcontroller.

## Figure 17

Interfacing the SmartLink-P to a Siemens SAB C510x or Motorola Microprocessor

#### **Microprocessor Clock Output**

The microprocessor clock is provided by the MCLK-output. Four clock rates are provided by a programmable prescaler. These are 7.68 MHz, 3.84 MHz, 1.92 MHz, 0.96 MHz. Switching between the clock rates is based on the lowest frequency and realized without spikes.

The value after reset is 3.84 MHz.

The clock rate is changed after  $\overline{CS}$  becomes inactive.

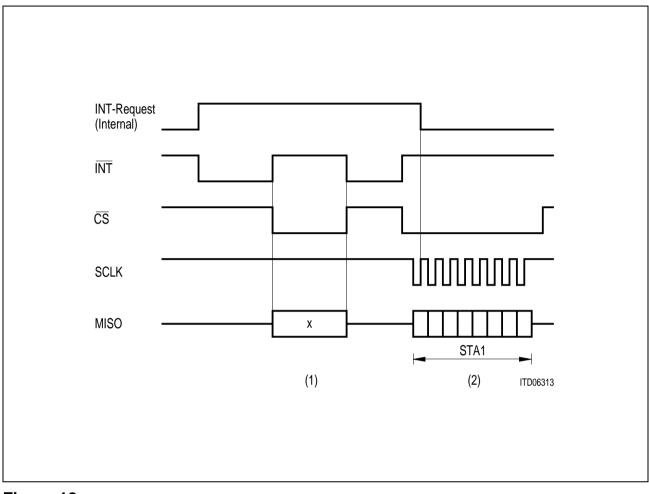

#### Interrupt Output

The interrupt output is an open drain output. The  $\overline{INT}$ -line can be activated at any time. The interrupt output is masked while  $\overline{CS}$  is active. Nevertheless, the interrupt request itself will only be cleared if STA1 or STA2 (in case of C/I-change) is read (2).

If  $\overline{CS}$  becomes active and STA1 is not read during this access,  $\overline{INT}$  becomes active again after  $\overline{CS}$  is turned high (1).

#### Figure 18 Interrupt Output

#### **Reset Logic**

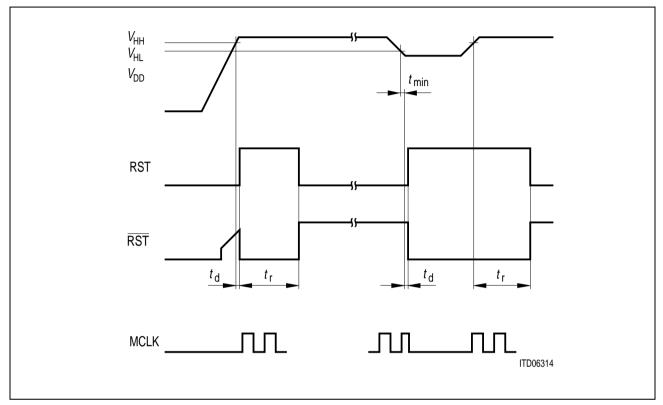

The SmartLink in provides two reset outputs (RST, RST) if the undervoltage detection is active. An alternative mode selects RST as input while RST outputs the inverse of RST. The undervoltage detection is not active in this mode.

Additionally, a watchdog timer is included which is started by a particular sequence. If it underruns, a reset signal is generated and some of the internal registers are reset.

#### **Undervoltage Detection**

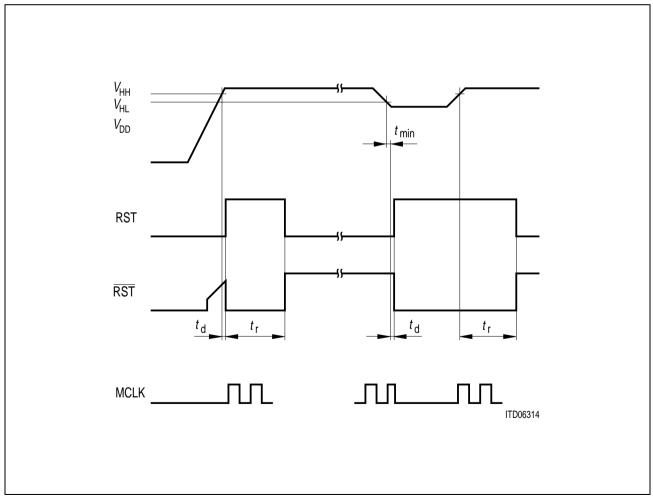

During power-up, the reset output is active until the threshold voltage of  $V_{\rm HH}$  has been reached. After that, a period of  $t_{\rm r}$  is counted until the reset output becomes inactive. It stays inactive until the supply voltage drops below threshold level  $V_{\rm HL}$ .

While the supply voltage is below the thresholds, the microcontroller clock MCLK is stopped and the MCLK-output remains low. If the supply voltage falls below threshold  $V_{\rm HL}$ , the clock is stopped immediately which may result in a shorter high period of the clock signal.

For  $V_{\rm HL}$  and the hysteresis between  $V_{\rm HL}$  and  $V_{\rm HH}$  the following values are specified.

| Parameter                                | Lir  | nit Values | Unit | Unit |

|------------------------------------------|------|------------|------|------|

|                                          | min. | max.       |      |      |

| V <sub>HL</sub>                          | 4.2  | 4.4        | V    |      |

| Hysteresis ( $V_{\rm HH} - V_{\rm HL}$ ) | 50   | 230        | mV   |      |

$t_r$  has a value of 1792 periods of the internal 32-kHz clock which is equal to 56 ms. The minimum period ( $t_{min}$ ) for the undervoltage detection is at maximum 11  $\mu$ s. The delay ( $t_d$ ) after threshold voltages have been passed is maximum 1  $\mu$ s.

During power-up, the reset pulse may be extended due to the oscillator start until a stable 15.36-MHz clock is achieved.

Figure 19 shows the undervoltage control timing.

#### Figure 19 Undervoltage Control Timing

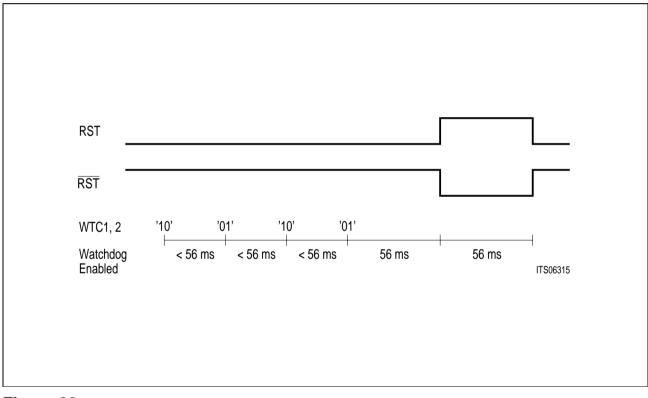

#### Watchdog Timer

The counter which is used for the reset generation can be used as watchdog timer. Once the power detection reset has been elapsed, the counter is disabled.

It can be enabled as watchdog timer with the first '10' sequence of the WTC1- and WTC2-bits. Once enabled, the software has to program '01', '10' sequences into the WTC1-, WTC2-bits each within 56 ms. If the next sequence doesn't occur within this period, a reset pulse is generated at the reset output which has a width of 56 ms.

The watchdog reset will only effect the CTRL3-register to reset the SDS-bits so that SDS and BCL become low. The watchdog timer will also reset the CTRL1-register (PW5-0 bits, PRE1, 0) and the LCRI-bit so that the PWO/Ring output becomes low.

#### Figure 20 Watchdog Operation

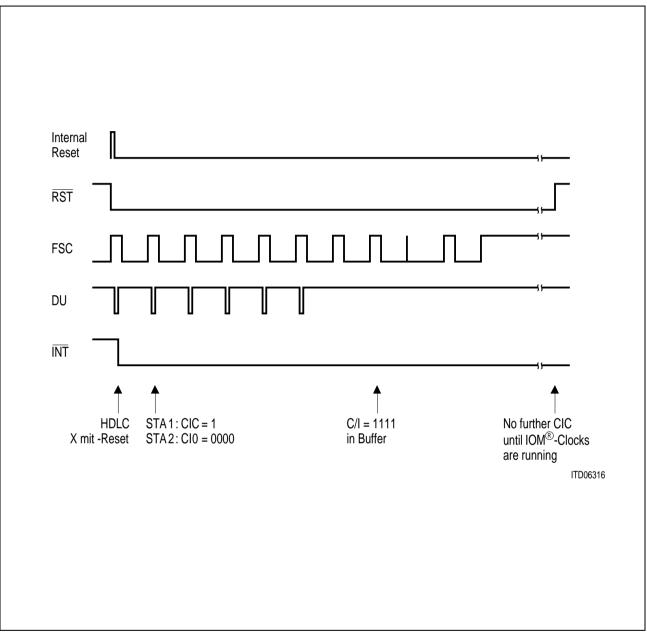

#### IOM®-Clocks Signals during Reset

The undervoltage detection generates internally a short reset pulse which is used to reset the internal registers and to trigger the 56 ms counter. After the short internal pulse is released, the  $U_{pn}$ -transceiver is reset. As a result, IOM-clocks are generated at the begin of the 56 ms external reset pulse and last for 11 IOM-frames (1.375 ms). After that, the IOM-clocks are stopped if the  $U_{pn}$ -interface remains deactivated. Generation of IOM-clocks is started after the SPU-bit is set in CTRL4 or if an external device requests IOM-clocks by pulling the data upstream (DU) line low. They are also started if an activation of the  $U_{pn}$ -interface is triggered by the line card or terminal repeater.

# SIEMENS

#### Figure 21 IOM<sup>®</sup>-Clocks Signals during Reset

The CIC-bit in the STA1-register is set when the microcontroller reads the STA1-register for the first time because the  $U_{pn}$ -transceiver outputs a 'DR' indication when it is reset. The 'DC' C/I-indication is stored in the C/I-buffer register. The software, after reading the STA1- and STA2-register will not get another CIC-status change unless the IOM-clocks are running. The value of the buffer register is transferred into the STA2-register only while IOM-clocks are running.

If the SmartLink is configured for an external reset, the IOM-clocks remain running during the reset input is active. IOM-clocks will be stopped after the  $U_{pn}$ -transceiver is reset following the end of the reset pulse.

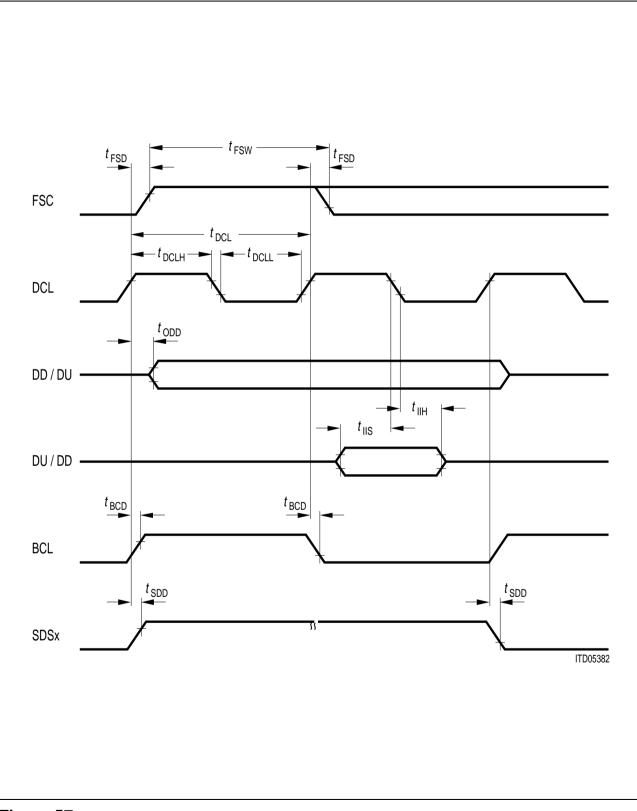

#### 2.1.3.2 IOM®-2 Interface in TE-Mode

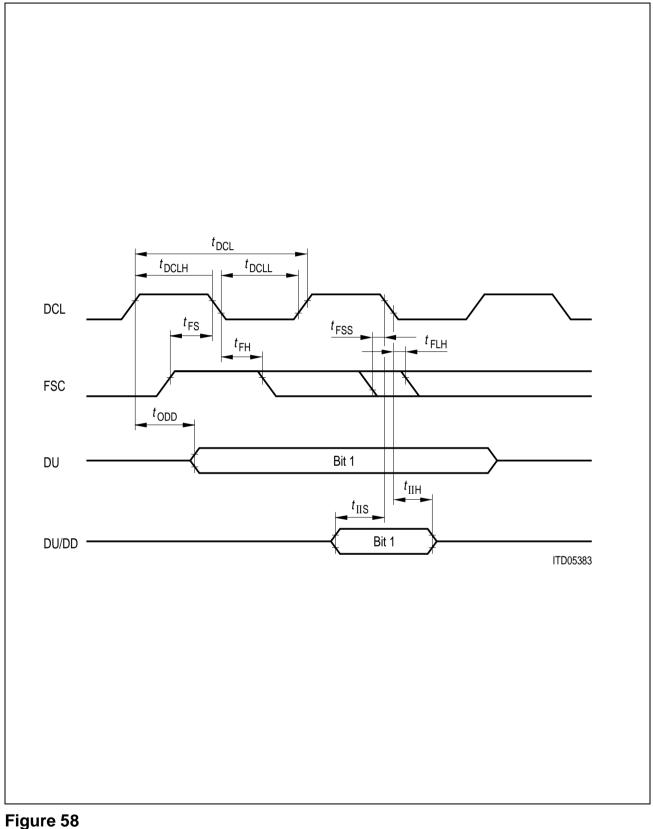

The SmartLink-P supports the IOM-2 terminal mode. The interface consists of four lines: FSC, DCL, DD and DU. FSC transfers a frame start signal of which the rising edge indicates the start of an IOM-2 frame (8 kHz). The FSC-signal is generated by the receive DPLL which synchronizes it to the received  $U_{pn}$ -frame. The DCL-signal is the clock signal to synchronize the data transfer on both data lines (768 kbit/s frequency is twice the transmission rate (1.536 MHz)). The first rising edge indicates the start of a bit while the second falling edge is used to latch the contents of the data lines. Additionally the BCL- and SDS-signals are provided to connect standard codecs to the SmartLink-P. The BCL (bit clock) provides a clock signal synchronous to the IOM-data at the same data rate. SDS provides a strobe signal which is active high during the B1- or B2- or IC1-channel.

The length of the FSC-signal on the IOM-2 interface will be reduced to one DCL-period every eighth IOM-2 frame. A reduced FSC-signal is generated after a code violation has been received from the  $U_{pn}$ -interface.

#### IOM<sup>®</sup>-2 Driver

The output driver of the DD- and DU-pins is open drain. The output drivers are active for the selected time-slot bits and remain tristate during the rest of the frame.

#### IOM<sup>®</sup>-2 Frame Structure

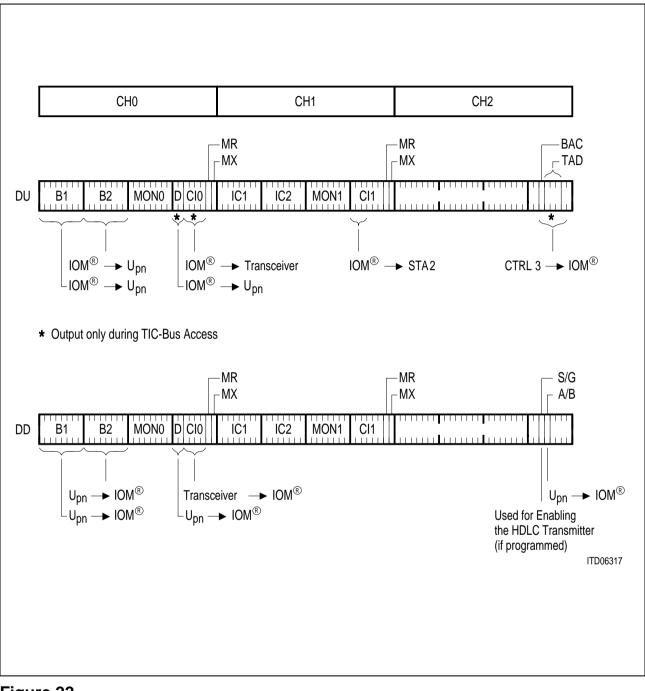

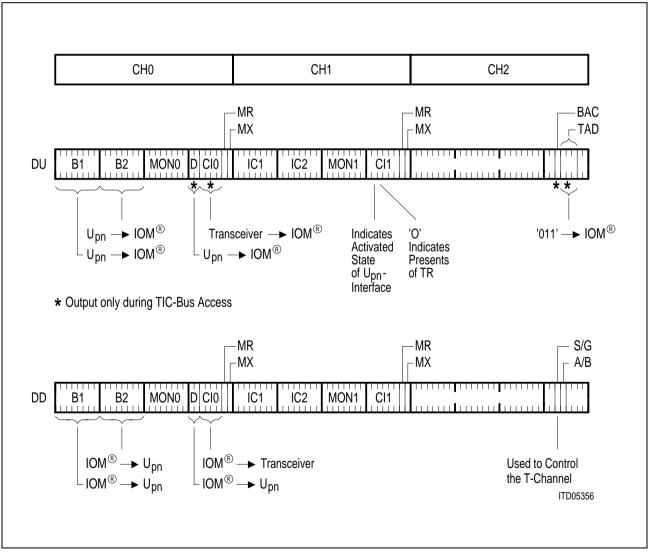

The principle frame structure of the IOM-2 terminal mode is shown in **figure 22.** The frame is composed of three channels.

# SIEMENS

#### Figure 22 IOM<sup>®</sup>-2 Terminal Mode

- Channel 0 contains 144 kbit/s of user and signaling data (2B + D) plus a MONITOR and command/indicate channel for control and programming of the layer-1 transceiver.

- Channel 1 contains two 64-kbit/s intercommunication channels plus a MONITOR and command/indicate channel to program or transfer data to other IOM-2 devices.

- Channel 2 is used for the TIC-bus access. Only the command/indicate bits are specified in this channel.

#### IOM<sup>®</sup>-2 Time-Slots used by the SmartLink-P

The SmartLink-P accesses a subset of all IOM-2 channels. It provides access to the D-channel, the C/I-channel 0 and to the TIC-bus. The information of the B1-, B2- and D-channel time-slots is forwarded transparently between the IOM-2 interface and the transceiver (in the activated state). Other time-slots (like IC1, IC2, MON0, MON1 with control/status bits) are not influenced by the SmartLink-P. They can be controlled by other devices connected to the IOM-2 interface. The most significant three bits of the C/I-channel 1 are received in the STA2-register.

#### Command/Indicate 0

C/l-code changes occur at maximum rate of 250  $\mu s$  (2  $\times$  IOM-frames). During activation the following sequence could occur:

If the software is not able to follow each change, it will at least get the first one and the last one. Thus it knows from where it started and about the current status.

#### Stop/Go Bit

The Stop/Go (S/G) bit can be controlled by the received  $U_{pn}$  T-channel to transmit the state of the line card arbiter to the HDLC-controller of the terminal. If selected by the SGE-bit, the HDLC-transmitter evaluates the state of the S/G-bit before and during transmission of an HDLC-frame.

#### Available/Busy Bit

The AB-bit has been added to the IOM-2 frame for the operation of a S/T-terminal adapter based on the SBCX. Since the SmartLink is not capable of transferring monitor channel data, a masked version of the SBCX was defined which reaches all necessary modes after reset. This part is called PSB 20810.

The terminal needs to know if a PSB 20810 is plugged in to switch the routing of the downstream T-channel correctly.

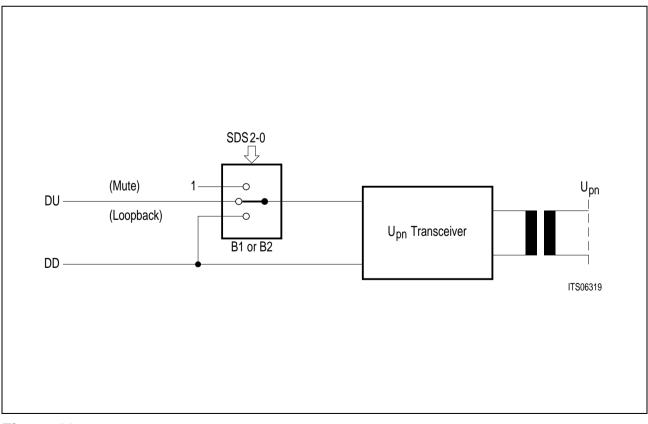

#### **MUTE Function**

The SDS-bits control the data path of the upstream B-channel information. B-channel information may either be transparent (IOM  $\rightarrow$  U<sub>pn</sub>) or disconnected. In the latter state, a constant value of all '1' is transmitted to the U<sub>pn</sub>-interface instead of the IOM-2 B-channel information. This feature can be used to realize a MUTE function together with a simple codec. The downstream B-channel data is not influenced.

#### **B-Channel Loopback**

The information of a B-channel (B1 or B2) received from the  $U_{pn}$ -interface can be looped back to the  $U_{pn}$ -interface. The selection is done via the SDS2-0 bits.

#### Figure 23 B-Channel Manipulation

# 2.1.3.3 U<sub>pn</sub>-Interface

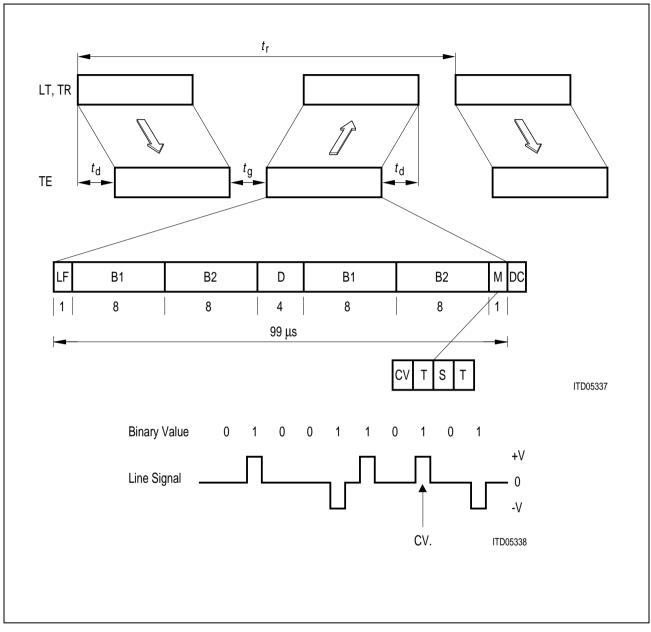

**Figure 24** demonstrates the general principles of the U<sub>pn</sub>-interface communication scheme. A frame transmitted by the exchange (LC) is received by the terminal equipment (TE) after a line propagation delay. The terminal equipment waits the minimum guard time (5.2  $\mu$ s) while the line clears. It then transmits a frame to the exchange. The exchange will begin a transmission every 250  $\mu$ s (known as the burst repetition period). However, the time between the reception of a frame from the TE and the beginning of transmission of the next frame by the LC must be greater than the minimum guard time.

Within a burst, the data rate is 384 kbit/s and the 38-bit frame structure is as shown in **figure 24**. The framing bit (LF) is always logical '1'. The frame also contains the user channels (2B + D). Note that the B-channels are scrambled. It can readily be seen that in the 250- $\mu$ s burst repetition period, 4 D-bits, 16 B1-bits and 16 B2-bits are transferred in each direction. This gives an effective full duplex data rate of 16 kbit/s for the D-channel and 64 kbit/s for each B-channel. The final bit of the frame is called the M-bit.

Four successive M-bits, from four successive  $U_{pn}$ -frames, constitute a superframe (**figure 24**). Three signals are carried in this superframe. The superframe is started by a code violation (CV). From this reference, bit 3 of the superframe is the service channel bit (S). The S-channel bit is transmitted once in each direction in every fourth burst repetition period. Hence the duplex S-channel has a data rate of 1 kbit/s. It conveys test loop control information from the LC to the TE and reports of transmission errors from the TE to the LC. Bit 2 and bit 4 of the superframe are the T-bits. Not allocated to a specific function until now (cf PEB 2095 IBC and PEB 20950 ISAC-P) they can be used for D-channel control in conjunction with PEB 20550 ELIC<sup>®</sup> and PEB 2096 OCTAT-P.

In order to decrease DC-offset voltage on the line after transmission of a CV in the M-bit position, it is allowed to add a DC-balancing bit to the burst. The LC-side transmits this DC-balancing bit, when transmitting INFO 4 and when line characteristics indicate potential decrease in performance.

Note that the guard time in TE is always defined with respect to the M-bit, whereas AMIcoding includes always all bits going in the same direction.

The coding technique used on the  $U_{pn}$ -interface is half-bauded AMI-code (i.e. with a 50 % pulse width). A logical '0' corresponds to a neutral level, a logical '1' is coded as alternate positive and negative pulses.

In the terminal repeater mode, no DC-balancing bit will be generated. The loop length of the TR-mode is limited to 100 m.

#### Figure 24 U<sub>pn</sub>-Interface Structure

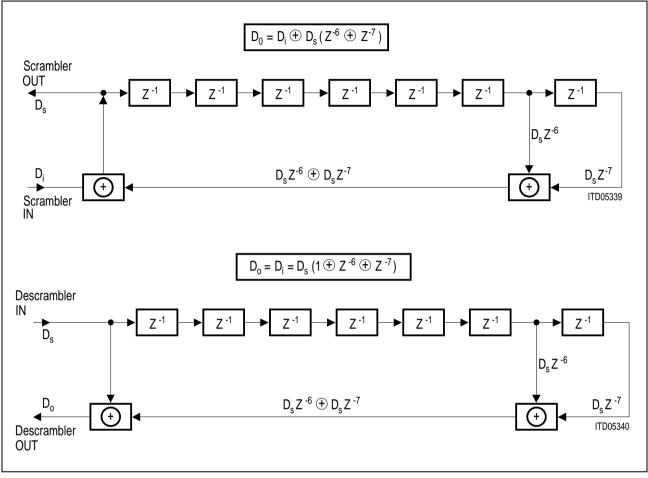

#### Scrambler/Descrambler

B-channel data on the  $U_{pn}$ -interface is scrambled to give a flat continuous power density spectrum and to ensure enough pulses are present on the line for a reliable clock extraction to be performed at the downstream end.

The SmartLink-P therefore contains a scrambler and descrambler, in the transmit and receive directions respectively. The basic form of these are illustrated in **figure 25**.

The form is in accordance with the CCITT V.27 scrambler/descrambler and contains supervisory circuitry which ensures no periodic patterns appear on the line.

Figure 25 Scrambler/Descrambler

# Info Structure on the $U_{pn}$ -Interface

The signals controlling the internal state machine on the  $U_{pn}$ -interface are called infos. In effect these pass information regarding the status of the sending  $U_{pn}$ -transceiver to the other end of the line. They are based upon the same format as the  $U_{pn}$ -interface frames and their precise form is shown in **table 1**.

When the line is deactivated info 0 is exchanged by the  $U_{pn}$ -transceivers at either end of the line. Info 0 effectively means there is no signal sent on the line in either direction.

When the line is activated info 3 upstream and info 4 downstream are continually exchanged. Both info 3 and info 4 are effectively normal  $U_{pn}$ -interface data frames containing user data and exchanged in normal burst mode.

Note that the structure of info 1 and info 2 are the same, they only differ in the direction of transmission. Similarly info 3/info 4 and info 1w/info 2w also constitute info pairs. This will be important when considering looped states.

As we will see, the other infos are exchanged during various states which occur between activation and deactivation of the line.

## Table 1 U<sub>pn</sub>-Interface Info Signals

| Name    | Direction              | Description                                                                                                                                             |  |

|---------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Info 0  | Upstream<br>Downstream | No signal on the line                                                                                                                                   |  |

| Info 1w | Upstream               | Asynchronous wake signal<br>2-kHz burst rate<br>F000100010001000101010100010111111<br>Code violation in the framing bit                                 |  |

| Info 1  | Upstream               | 4-kHz burst signal F00010001000100010101010001011111M <sup>1)</sup> $DC^{2)}$ Code violation in the framing bit                                         |  |

| Info 2  | Downstream             | 4-kHz burst signal<br>F0001000100010001010101010001011111M <sup>1)</sup> DC <sup>2</sup><br>Code violation in the framing bit                           |  |

| Info 3  | Upstream               | 4-kHz burst signal<br>No code violation in the framing bit<br>User data in B-, D- and M-channels<br>B-channels scrambled, DC-bit <sup>2)</sup> optional |  |

| Info 4  | Downstream             | 4-kHz burst signal<br>No code violation in the framing bit<br>User data in B-, D- and M-channels<br>B-channels scrambled, DC-bit <sup>2)</sup> optional |  |

#### Note:

- The M-channel superframe is transparent: S-bits transparent (1-kbit/s channel) T-bits transparent (2-kbit/s channel)

- <sup>2)</sup> DC-balancing bit

The following test patterns are also included:

| Name    | Direction | Description                                                      |

|---------|-----------|------------------------------------------------------------------|

| Info T1 | Upstream  | Test signal single pulse<br>2-kHz burst rate<br>100000000        |

| Info T2 | Upstream  | Test signal continuous pulses<br>192-kHz clock rate<br>111111111 |

#### Upn-Transceiver

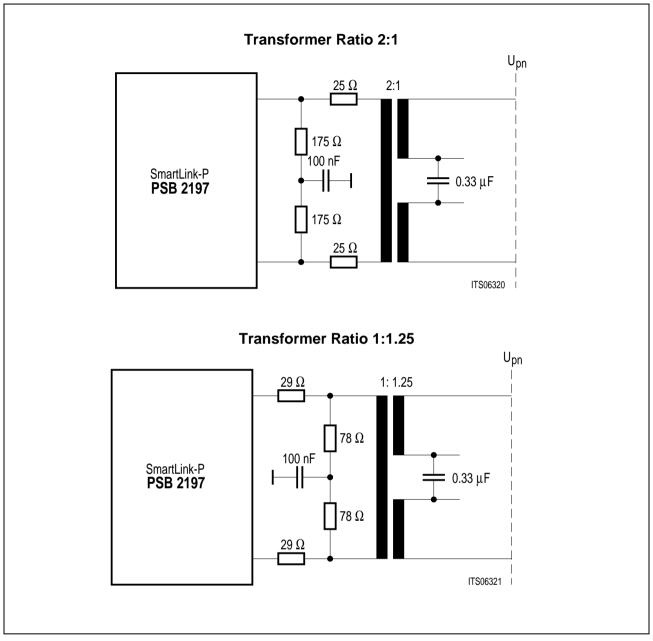

**Figure 26** depicts the transceiver architecture and the analog connections of the SmartLink-P. External to the line interface pins Lla and Llb a transformer and external resistors are connected as shown. Note that the internal resistors of the transformer are calculated as zero. The actual values of the external resistors must take into account the real resistor of the chosen transformer.

The receiver section consists of an amplifier followed by a peak detector controlling the thresholds of the comparators. In conjunction with a digital oversampling technique the PSB 2197 SmartLink-P covers the electrical requirements of the U<sub>pn</sub>-interface for loop lengths of up to 4.5 kft on AWG 24 cable and 1.0 km on J-Y(ST) Y  $2 \times 2 \times 0.6$  cable.

# Figure 26 U<sub>pn</sub>-Transceiver of the SmartLink-P

# Upn-Transceiver Timing

The receive PLL uses the 15.36-MHz clock to generate an internal 384-kHz signal which is used to synchronize the PLL to the received  $U_{pn}$ -frame. The PLL outputs the FSC-signal as well as the 1.536-MHz double bit clock signal and the 768-kHz bit clock.

The length of the FSC-signal is reduced in the next IOM-2 frame which is started while a  $U_{pn}$ -frame is received, after a code violation has been detected. The reduced length of the FSC-signal provides synchronization between the TE- and the TR-transceiver to gain the shortest delays on the  $U_{pn}$  T-channel data forwarding.

#### Figure 27 U<sub>pn</sub>-Transceiver Timing B1-, B2-Channels

The IOM-interface B-channels are used to convey the two 64-kbit/s user channels in both directions. However, the PSB 2197 SmartLink-P only transfers the data transparently in the activated state (incl. analog loop activated) while the data are set to '1' in any non activated state (cf. state descriptions).

#### D-Channel

Similar to the B-channels the layer-1  $(U_{pn})$  part of the PSB 2197 SmartLink-P transfers the D-channel transparently in both directions in the activated state.

# **T-Bit Transfer**

In TE-mode the layer-1 ( $U_{pn}$ ) part of the PSB 2197 SmartLink-P conveys the T-bit position of the  $U_{pn}$ -interface to either the S/G-bit position or the A/B-bit position according to the register programming. The exact bit polarities are as follows:

# **Downstream (U**<sub>pn</sub> $\rightarrow$ **IOM**<sup>®</sup>**)** T-to A/B-mapping (CTRL3: TCM = 1):

T = 0: A/B = 0 S/G = 1 blocked T = 1: A/B = 1 S/G = 1 available T-to S/G-mapping (CTRL3: TCM = 0): T = 0: A/B = 1 S/G = 1 blocked B/B = 1 S/B =

T = 1: A/B = 1 S/G = 0 available

# Upstream (IOM<sup>®</sup> $\rightarrow$ U<sub>pn</sub>)

The T-channel in upstream direction is controlled by the BAC-bit of the IOM-2 interface. The T-channel transmits the inverse of the BAC-bit.

Special care is taken so that the slave terminal will only send one HDLC-frame until the TIC-bus of the master IOM-2 interface is release. This is achieved by a circuitry which latches the BAC-state of '1' until at least one T-bit has been transmitted with the value of '0' which releases the TIC-bus of the master IOM-2 interface.

BAC to T-mapping:

# Control of the Upn-Transceiver

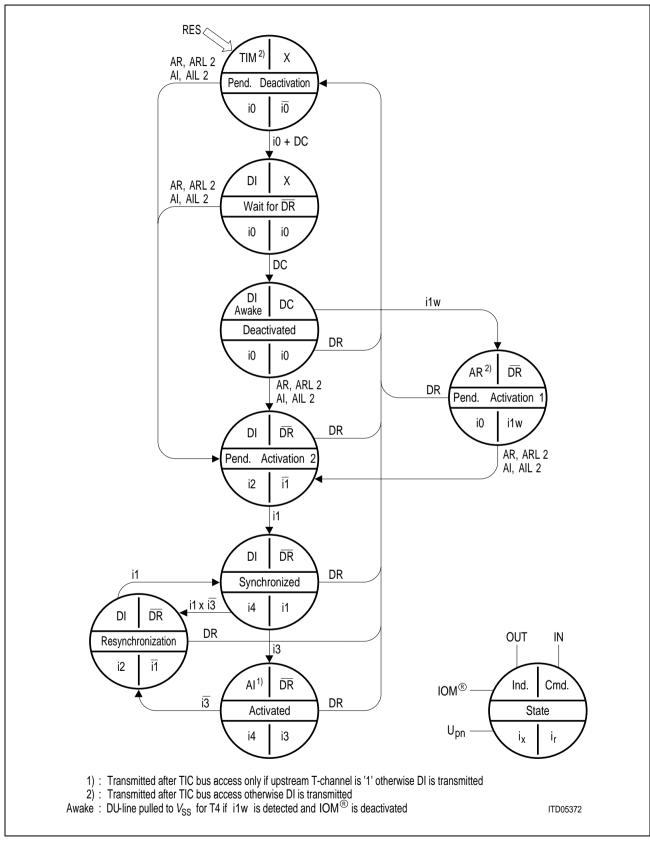

An incorporated finite state machine controls the activation/deactivation procedures and communications with the layer-2 section via the IOM-Command/Indicate (CI) channel 0.

# **Diagnostics Functions**

Two test loops allow the local or the remote test of the transceiver function.

Test loop 3 is a local loop which loops the transmit data of the transmitter to its receiver. The information of the IOM-2 upstream B- and D-channels is looped back to the downstream B- and D-channels. The M-bit is also transparent which means that the state of the BAC-bit is looped back to the S/G- or AB-bit.

Test loop 2 is activated by the  $U_{pn}$ -interface and loops the received data back to the  $U_{pn}$ -interface. The D-channel information received from the line card is transparently forwarded to the downstream IOM-2 D-channel.

The downstream B-channel information on IOM-2 is fixed to 'FF' $_{\rm H}$  while test loop 2 is active.

#### 2.1.4 D-Channel-Arbitration in TE-Mode

The SmartLink-P supports different kinds of D-channel arbitration in order to share the upstream D-channel by several communication controllers and to allocate the D-channel from the  $U_{pn}$ -interface.

The following functions are performed depending on the register settings:

- Allocation of the upstream D-channel bits on the IOM-2 interface via the TIC-bus.

- Control of the HDLC-transmitter by the stop/go bit.

#### **TIC-Bus Access**

The terminal IC-bus provides an access mechanism to share the D-channel in upstream direction by several communication controllers (ICC, ISAC, SmartLink) connected to one layer-1 device. The Bus Accessed bit (BAC) is used to indicate that the TIC-bus is currently occupied and other devices have to wait. The different communication controllers use individual TIC-bus addresses in the range of '0' to '7'. A collision detection mechanism checks each bit of the TIC-bus address for congestion. Since a '0' has higher priority against a '1', a TIC-bus address of '0' has the highest priority and '7' has the lowest one.

#### TIC-Bus Access Mechanism

During idle state, the Bus Accessed bit (BAC) is set to '1' and the TIC Bus Address (TBA) is '7'. If a communication controller needs access to the D-channel bits, it will check the state of the BAC bit. If BAC is '1' (idle) it will place its TIC-bus address on the TAD2-0 bits. After each bit has been outputted, it checks for collision and stops transmitting if a collision is detected ('1' transmitted, '0' detected on the DU-line). If the TIC-bus address has been transmitted successfully, the D-channel and C/I-channel 0 are controlled from the controller in the next frame and the BAC-bit is set to '0'. After the TIC-bus access is completed, the TIC-bus returns to the idle state (BAC = '1', TAD = '111') and other devices can gain access.

A device which has detected a collision during the transmission of the TIC-bus address will restart after the BAC-bit becomes idle '1' again. In order to provide access to all controllers, the device which has gained successful access to the TIC-bus will wait for two idle frames before it starts another access.

**Note:** The SmartLink will also set the BAC-bit if the TIC-bus address of seven ('111') is programmed. This is different to the TIC-bus operation of the ICC (PEB 2070) and ICC-based devices (ISAC-S (TE), ISAC-P (TE)).

#### Stop/Go Bit

The stop/go bit controls the transmitter output of the D-channel HDLC-controller if selected by the SGE-bit. The transmitter is active, as long as the stop/go bit indicates go ('0').

The S/G-bit is checked before a HDLC-frame is started and monitored during the transmission of the HDLC-frame. The HDLC-transmitter aborts the transmission of an HDLC-frame if the S/G-bit becomes 'Stop' after the begin of a frame was transmitted. It will output '11' in the D-bits of the IOM-frame beginning with the following IOM-frame after S/G becomes 'Stop' until 'Go' is indicated. The evaluation of the S/G-bit must be enabled by the CTRL3:SGE-bit.

The stop/go bit can be controlled by the downstream T-bit which indicates the receive capability of the line card or by the PSB 20810 in case a S/T-interface adapter is plugged onto the IOM-2 interface.

#### HDLC-Controller Access Modes

The access mode of the D-channel HDLC-controller is programmable. It can ignore the TIC-bus, use the TIC-bus to gain access and evaluate the S/G-bit.

**Table 2** shows the possible combinations.

# Table 2HDLC-Controller Access Modes

| TBU | SGE | TIC-Bus Access | S/G-<br>Evaluation | Application                                           |

|-----|-----|----------------|--------------------|-------------------------------------------------------|

| 1   | 0   | Yes            | No                 | TIC-bus access without S/G-bit evaluation             |

| 1   | 1   | Yes            | Yes                | TIC-bus access with S/G-bit evaluation                |

| 0   | 0   | No             | No                 | Permanent D-channel access without S/G-bit evaluation |

| 0   | 1   | No             | Yes                | Permanent D-channel access with S/G-bit evaluation    |

If the HDLC-controller is set to a mode where the S/G-bit is evaluated, the transmission is started if the S/G-bit becomes go ('0') and stopped if the S/G-bit becomes stop ('1').

If the D-channel becomes not available before the final bit of the closing flag has been sent, the transmission is aborted. In case the collision occurred during the first XFIFO contents, the frame is automatically retransmitted. If the first XFIFO contents has already been sent, a XMR-status is generated and the microcontroller has to repeat the complete frame again.

## 2.1.5 HDLC-Controller

The HDLC-controller performs the layer-2 functions of the D-channel protocol:

- Flag generation/detection

- Zero bit insertion/deletion

- CRC-generation/check (CCITT polynomial X<sup>16</sup> + X<sup>12</sup> + X<sup>6</sup> + 1)

- Abort generation

- Idle signal generation ('1')

#### **HDLC-Frame Formatting**

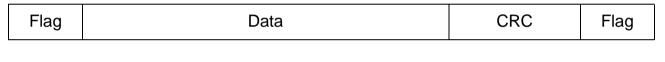

The HDLC-transmitter starts a HDLC-frame with a flag. It continues with the data of the XFIFO. The end of a frame is indicated by a closing flag preceeded by the 16-bit CRC-check sum or by an abort sequence.

XFIFO

#### Figure 28 HDLC-Transmitter Format

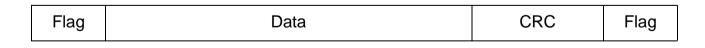

# The HDLC-receiver hunts for flags which are not followed by another flag or an abort sequence. It stores the information in the RFIFO until the end of the frame has been detected. The status of the received frame (CRC-status, end of frame condition etc.) is reported via a status byte which is stored in the RFIFO immediately following the last byte of a message.

The HDLC-receiver of the SmartLink will receive two frames correctly if they are separated by only one common flag (shared flag). It will also receive two frames correctly if they are separated by two flags (back-to-back frames).

| Data  | RSTA |

|-------|------|

|       |      |

| RFIFO |      |

#### 2.1.6 Terminal Specific Functions

#### 2.1.6.1 LCD-Contrast Control

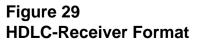

The Pulse Width Output/Ring provides a pulse width modulated signal which can be varied in 14 linear steps between OFF and ON. The repetition frequency is 8.5 kHz. The LCD-contrast control is enabled by setting the LCRI-bit to '0'.

The output of the PWM is filtered by a low pass filter and transformed to the required voltage range by an external transistor as shown in **figure 30**.

#### Figure 30 LCD-Contrast Control

#### 2.1.6.2 Ring Tone Generation

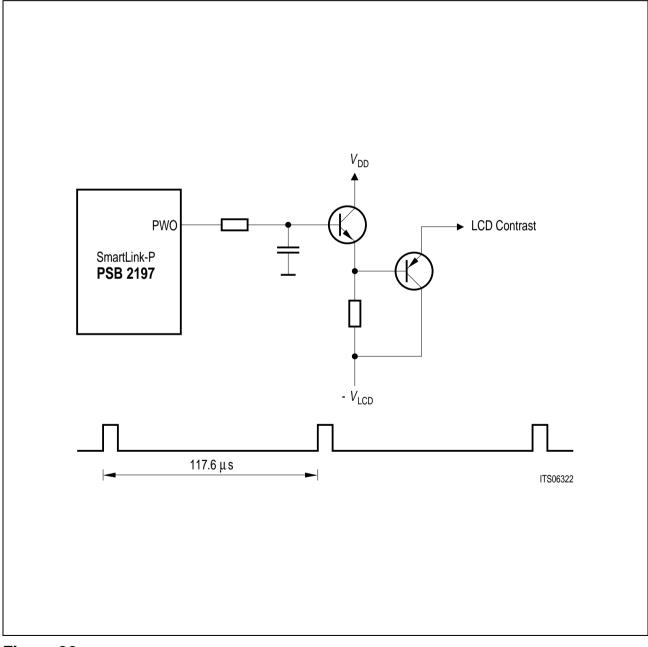

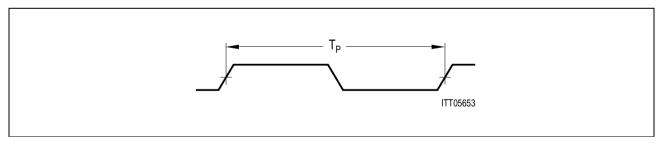

The SmartLink-P can generate frequencies at the Pulse Width Output/Ring. The ring tone generator uses a 16 kHz-clock input and divides it by a programmable value of n = 1 to 63. The PWO/Ring output is tristate while PW5-0 are '000000'. The following list shows examples of frequencies:

| Value | (PW5-0)  | Frequency (Hz) |

|-------|----------|----------------|

| 8     | (001000) | 2000           |

| 10    | (001010) | 1600           |

| 11    | (001011) | 1454           |

| 12    | (001100) | 1333           |

| 14    | (001110) | 1142           |

| 15    | (001111) | 1066           |

| 17    | (010001) | 941            |

| 19    | (010011) | 842            |

| 20    | (010100) | 800            |

| 21    | (010101) | 761            |

| 23    | (010111) | 695            |

| 27    | (011011) | 592            |

| 29    | (011101) | 551            |

| 33    | (010001) | 484            |

| 36    | (100100) | 444            |

| 41    | (101001) | 390            |

| 51    | (110011) | 313            |

Ring tones change or stop at the end of a half or full cycle. This includes switching to tristate.

Ring Tone Generation

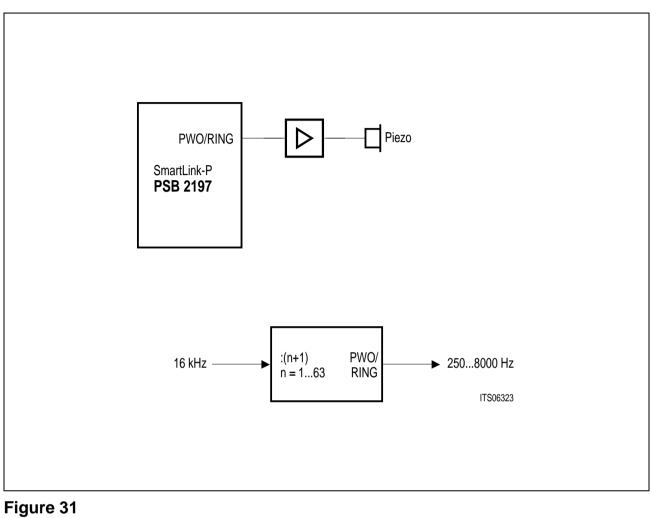

#### 2.2 Terminal Repeater (TR) Mode

#### 2.2.1 General Functions and Device Architecture (TR-Mode)

In TR-mode the following functions are provided:

- U<sub>pn</sub>-interface transceiver, functionally fully compatible to both PEB 2095 IBC and PEB 2096 OCTAT-P, also features the terminal repeater mode

- IOM-2 interface for terminal application

- A microcontroller clock is not generated

#### Figure 32 Device Architecture in TR-Mode

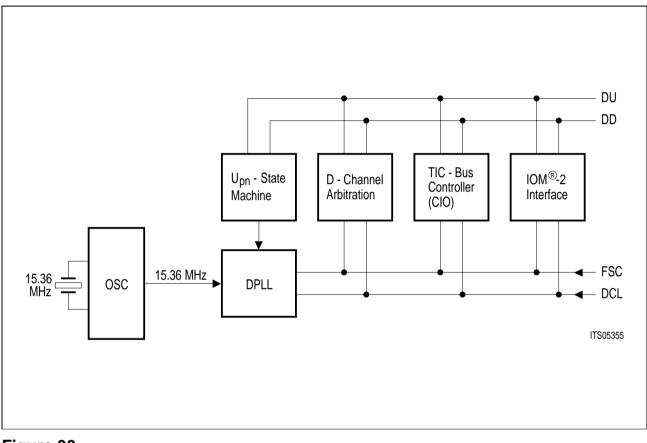

## 2.2.2 Clock Generation (TR-Mode)

In TR-mode, the oscillator is used to generate a 15.36-MHz clock signal. This signal is used by the DPLL to synchronize  $U_{pn}$ -frames to the received IOM-2 clocks (FSC, DCL). No other clocks are generated.

Figure 33 Clock Generation in TR-Mode

#### 2.2.3 Interfaces (TR-Mode)

In TR-mode, two interfaces are active:

- IOM-2 interface: as a universal backplane for terminals

- Upn-interface towards the two-wire slave subscriber line

The microcontroller interface remains active in TR-mode. As a result, the  $\overline{\text{CS}}$ -input has to be connected to  $V_{\text{DD}}$  and MOSI has to be connected to  $V_{\text{SS}}$  avoid accidental programming.

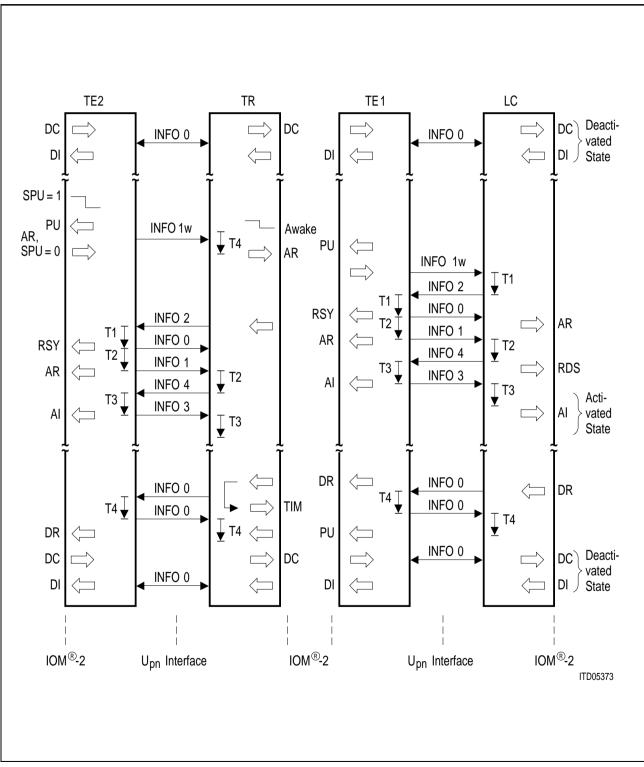

#### 2.2.3.1 IOM®-2 Interface in TR-Mode

The SmartLink-P supports the IOM-2 terminal mode. The interface consists of four lines: FSC, DCL, DD and DU. FSC and DCL provide the clock inputs to synchronize the  $U_{pn}$ -transceiver to the IOM-2 interface. DU and DD are open drain outputs.

#### Figure 34 IOM<sup>®</sup>-2 Frame Structure in TR-Mode

The SmartLink-P transfers the B-channel information between the IOM-2 and the  $U_{pn}$ -interface during the activated state. During all other states, 'FF' is output. The C/I-channel 0 as well as the upstream D-bits are occupied by the TR-SmartLink after a TIC-bus access has been performed. The BAC- and TAD-bits are used for the TIC-bus access.

The SmartLink-P in TR-mode pulls bit 5 of the upstream command/indicate channel 1 to '0' after reset and remains '0' for identification of the TR-module by a terminal SmartLink-P or ISAC-P TE.

Bit 6 of the upstream C/I-channel 1 is also controlled by the SmartLink-P in TR-mode. It is set to '0' if the  $U_{pn}$ -interface is in the activated state. Otherwise, the bit remains '1'.

# 2.2.3.2 Upn-Interface in TR-Mode

# U<sub>pn</sub>-Transceiver

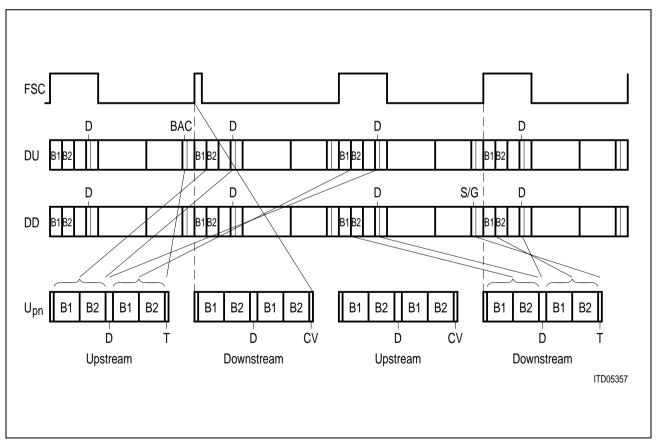

The transmitter uses the received FSC-signal to start the generation of a  $U_{pn}$ -frame. If a short FSC-length (1 × DCL) is detected, the superframe counter is reset and the next  $U_{pn}$ -frame will transmit the CV in the M-bit. During normal length of the FSC-signal (64 DCL-clocks), the superframe counter is not changed.

#### Figure 35 U<sub>pn</sub>-Transceiver Timing

Semiconductor Group

# Control of the Upn-Transceiver

An incorporated finite state machine controls the activation/deactivation procedures and communications with the layer-2 section via the IOM-Command/Indicate (C/I) channel 0.

In TR-mode, activation from the terminal side is started by a power-up sequence in case the FSC- and DCL-clocks are turned off. After that, a TIC-bus access is performed and activation is started by outputting the C/l-code 'AR'. After that, the  $U_{pn}$ -interface is activated and after completion of the procedure, the C/l-code 'Al' is output.

The length of the FSC-signal is monitored. The state-machine of the  $U_{pn}$ -transceiver is reset every time, a FSC-period of less than 96 bits is detected. It will generate a reset signal for the state machine which is active for 6 IOM-frames. As a result, 4 or 5 info 0 frames will be transmitted on  $U_{pn}$  a to force the TE-device in the level detect (resynchronization) state. This number of info 0 frames is still less than is required to detect Info 0 by the TE-device (2 ms, 8 info 0 frames). This procedure is necessary to avoid incorrect switching of internal B-channel buffers which corrupt the sequence of B-channel transfer between IOM and  $U_{pn}$ .

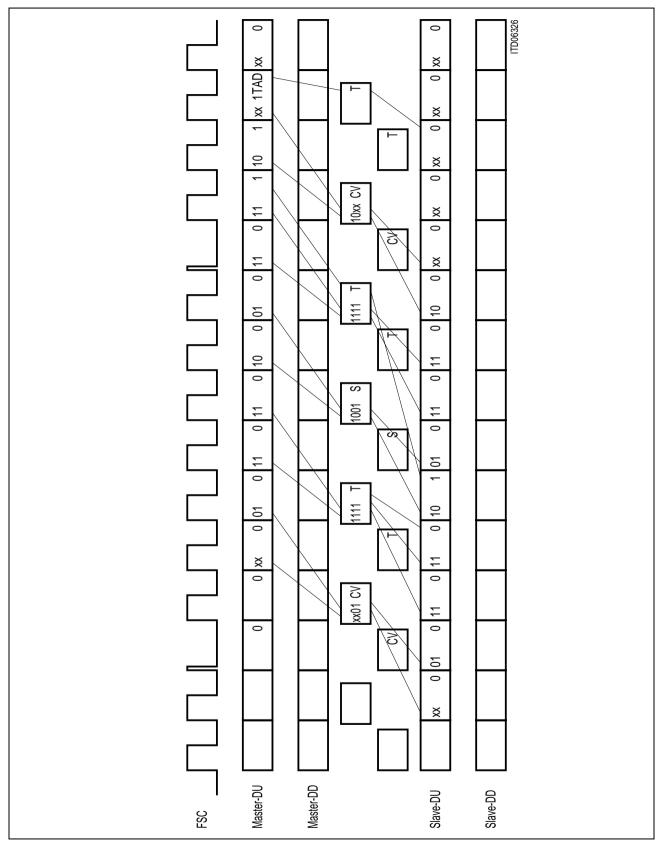

#### 2.2.4 D-Channel-Arbitration in TR-Mode

The D-channel arbitration is done using the TIC-bus features and the T-channel of the  $U_{pn}$ -interface.

#### TIC-Bus Idle

If the TIC-bus is idle (BAC = '1', TAD = '111'), upstream D-channel data is transparently switched to the IOM-2 D-channel. No C/I0-code is transmitted by the TR-SmartLink.

#### **D-Channel Request**

A D-channel request is indicated by the terminal connected to the TR-SmartLink by setting the upstream T-channel to '1' (inverse of its IOM-2 BAC-bit). As a result, the TR-SmartLink tries to access the TIC-bus by outputting the TIC-bus address ('011'). After successful transmission of all three bits, the BAC-bit is set to '1' in the following IOM-2 frame and the TIC-bus is occupied. On the C/I-channel 0, the code 'AI' ('1100') is output.

# **D-Channel Release**

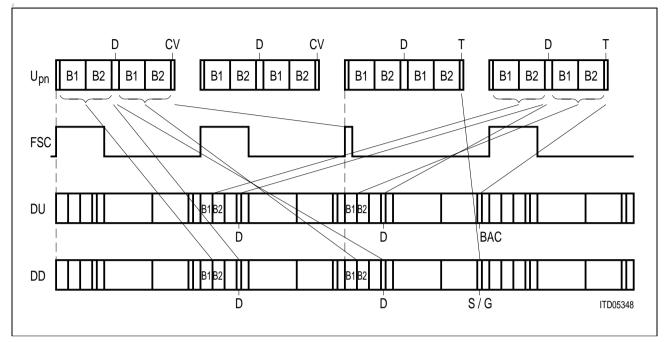

After the terminal connected to the TR-SmartLink has completed its HDLC-frame, the upstream T-channel becomes '0' (inverse of its IOM-2 BAC-bit). This transition from T = '1' to T = '0' is delayed by the TR-SmartLink by two IOM-frames before the TIC-bus is released. This delay is necessary to assure that the D-channel contents of the U<sub>pn</sub>-frame which included the T-channel is output completely.

# SIEMENS

#### Figure 36 D-Channel Arbitration in TR-Mode

#### 2.2.5 Reset

In TR-mode, the undervoltage detection is not active. To reset the SmartLink-P in TR-mode an external reset signal must be applied on the  $\overline{\text{RST}}$  input. The reset will deactivate the U<sub>pn</sub>-transceiver and it will abort any TIC-bus access currently in progress. The TIC-bus returns to idle.

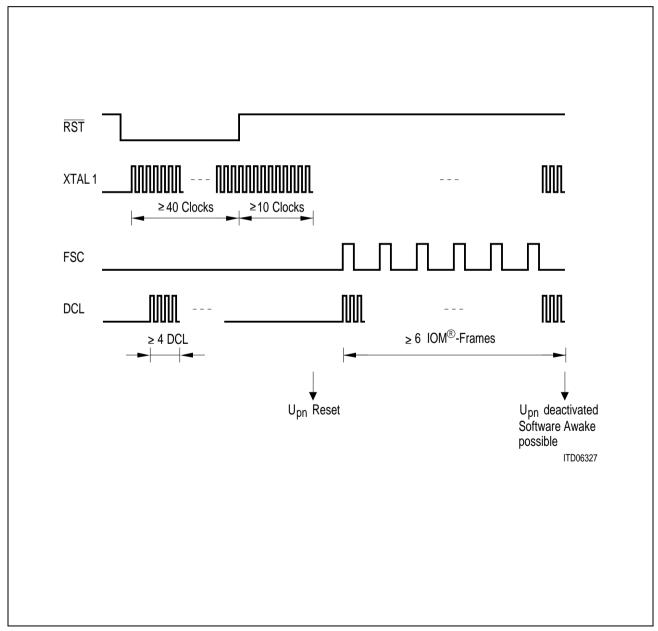

While the reset signal is active, at least 40 clock pulses must be applied to XTAL1 and at least 4 DCL-pulses. More than 10 clock pulses on XTAL1 are required after reset becomes inactive. At least 6 IOM-frames are necessary after reset is released to put the  $U_{pn}$ -transceiver in its deactivated state from which an asynchronous awake is possible if a level is detected on the  $U_{pn}$ -interface pins.

#### Figure 37

Semiconductor Group

#### 2.3 HDLC-Controller Mode

#### 2.3.1 General Functions and Device Architecture (HDLC-Controller Mode)

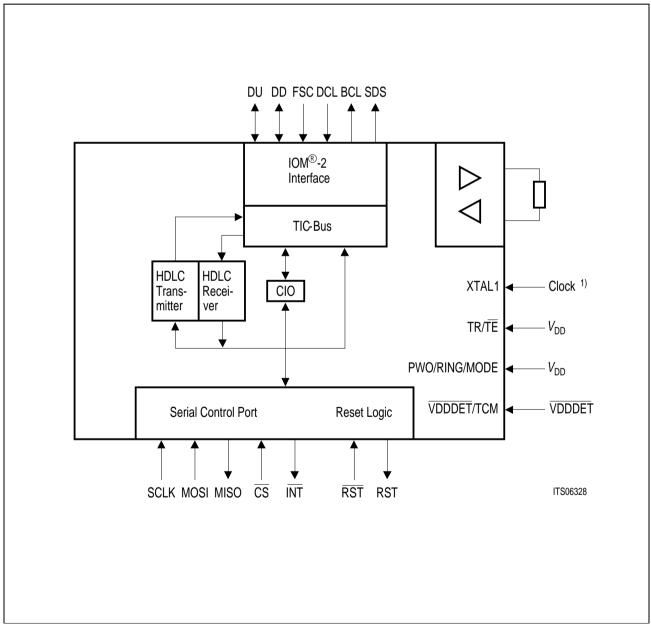

Figure 38 depicts the detailed architecture of the PSB 2197 SmartLink-P in HDLC-controller mode:

- Serial control port

- HDLC-controller with  $2 \times 4$  byte FIFOs per direction

- TIC-bus access control

- IOM-2 interface for terminal application

#### Figure 38 Device Architecture of the SmartLink-P in HDLC-Controller Mode

## 2.3.2 Clock Generation (HDLC-Controller Mode)

In HDLC-controller mode, the oscillator input is used to achieve the reset state of the  $U_{pn}$ -transceiver. All other functions which use the oscillator frequency in TE-mode (undervoltage detection, watchdog, microcontroller clock output, PWO/RING) are disabled. The IOM-2 clock signals (FSC, DCL) are used to synchronize the HDLC-data transfer and the access to the TIC-bus. A bit clock signal as well as a strobe signal for B1, B2 or IC1 may be generated.

#### Figure 39 Clock Generation in HDLC-Controller Mode

#### 2.3.3 Interfaces (HDLC-Controller Mode)

The PSB 2197 SmartLink-P serves two interfaces in HDLC-controller mode:

- · Serial microcontroller interface for higher layer functions

- IOM-2 interface: between layer-1 and layer-2 and as a universal backplane for terminals

- Bit clock and strobe signal generation

#### 2.3.3.1 Microcontroller Interface

The SmartLink-P provides a serial microcontroller interface which is compatible to the SPI-interface of Motorola or Siemens C510x microcontrollers.

Its function is identical to the TE-mode.

## 2.3.3.2 IOM<sup>®</sup>-2 Interface in HDLC-Controller Mode

The SmartLink-P supports the IOM-2 terminal mode. The interface consists of four lines: FSC, DCL, DD and DU. FSC and DCL provide the clock inputs to synchronize the data transfer over the IOM-2 interface. DU and DD are open drain outputs.

CH0 CH1 CH2 BAC MR MR МΧ -MX TAD MON0 DU B1 B2 D CI0 IC1 MON1 IC2 CI1 \* ^ \* IOM<sup>®</sup> → Transceiver CTRL1:2-0  $\rightarrow$  IOM<sup>®</sup>  $\rightarrow$  STA2 CTRL3  $\rightarrow$  IOM<sup>®</sup> └IOM<sup>®</sup> → Upn Output only during TIC-Bus Access MR MR S/G МΧ MX A/B MON0 D CIO IC1 IC2 MON1 CI1 DD B1 B2 Transceiver → IOM<sup>®</sup> Used for Enabling the HDLC Transmitter └U<sub>pn</sub> → IOM® (if programmed) ITD06330

A bit clock and strobe signal may be generated locally.

#### Figure 40 IOM<sup>®</sup>-2 Frame Structure in HDLC-Controller Mode

The C/I-channel 0 as well as the upstream D-bits are occupied by the HDLC-controller mode SmartLink after a TIC-bus access has been performed. The BAC- and TAD-bits are used for the TIC-bus access.

The SmartLink-P in HDLC-controller mode outputs the value of CTRL1:2-0 as CI1 bits 7 to 5. After reset, they remain '1'.

All other time-slots are not influenced by the SmartLink-P in HDLC-controller mode.

# 2.3.4 D-Channel-Arbitration in HDLC-Controller Mode

The D-channel arbitration is identical to the one in TE-mode.

# 2.3.5 HDLC-Controller

The HDLC-controller functions are identical to the ones in TE-mode.

# 2.3.6 Reset

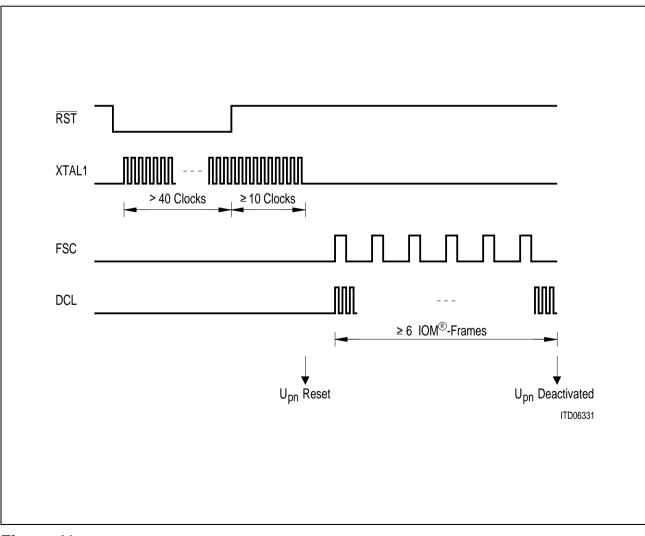

The HDLC-controller mode is reset by applying a reset pulse to the RST-input.

To bring the  $U_{pn}$ -transceiver to a low power state, the following requirements must be fulfilled: While reset is active, at least 40 clock pulses must be applied to XTAL1. After reset is released, another 10 clock pulses are required. The  $U_{pn}$ -transceiver enters its low power deactivated state after 6 IOM-frames which are generated after the 50 clock pulses on XTAL1 have elapsed.

#### Figure 41 Reset

Semiconductor Group

#### **3 Operational Description**

#### 3.1 TE-Mode

#### 3.1.1 Interrupt Structure and Logic

The SmartLink-P provides one interrupt output which is used to indicate a change in the receiver or transmitter status or a change in the CI0-code. The microcontroller has to read the first status byte (STA1). The first status byte indicates changes of the receiver/transmitter section. CI0-code changes are indicated by the CIC-bit. In case of a CI0-change, the microcontroller has to evaluate the second status byte (STA2). It contains the new CI0-code value. Reading the STA1-status byte clears the interrupt request and the RPF-, RME-, XFS-, RFO-bits. The CIC-status bit and the interrupt generation by that bit is cleared by reading STA2.

#### Figure 42 SmartLink-P Interrupt Structure