# **SIEMENS**

# **General Purpose Power Controller (GPPC)**

**PSB 2121**

#### **Preminimary Data**

CMOS IC

| Туре       | Ordering Code | Package        |

|------------|---------------|----------------|

| PSB 2121-P | Q67100-H8646  | P-DIP-16       |

| PSB 2121-T | Q67100-H6032  | P-DSO-20 (SMD) |

The PSB 2121 is a pulse width modulator circuit designed for fixed-frequency switching regulators with very low power consumption.

In telefony and ISDN systems a high conversion yield is crucial to maintain functionality in all supply conditions via "S" or "U" interfaces. The PSB 2121 design and technology realize high conversion efficiency and low power dissipation.

It should be recognized that the PSB 2121 can also be used in numerous DC/DC conversion systems other than ISDN power supplies.

### The PSB 2121 Contains the Following Functional Blocks

- Undervoltage lockout

- Temperature compensated voltage reference

- Sawtooth oscillator

- Error amplifier

- Pulse width modulator

- Digital current limiting

- Soft start

- Double pulse inhibit

- Power driver

Together with few external components it provides a stable 5 V DC supply for subscriber terminals (TEs) or network terminations (NTs). It can also be programmed for higher output voltages, e.g. to supply S-lines with 40 V.

- Switched mode DC/DC-converter

- CCITT ISDN compatible

- Low power dissipation

- Supply voltage range 8 V to 70 V

- Programmable input undervoltage protection

- Programmable overcurrent protection

- Soft start

- Power housekeeping input

- Oscillator synchronization input/output

- High voltage CMOS technology 70 V

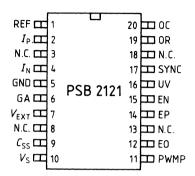

## **Pin Configurations**

(top view)

P-DIP-16

P-DSO-20

# **Pin Definitions and Functions**

| Pin No.<br>P-DIP | Symbol           | Input (I)<br>Output (O) | Definition                         | Function                                                                                                                                                               |

|------------------|------------------|-------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | REF              | 0                       | Reference voltage                  | Output of the 4.0 V reference voltage.                                                                                                                                 |

| 2                | $I_{P}$          | 1 .                     | Positive current sense             | When the voltage difference be-<br>tween these two pins exceeds                                                                                                        |

| 3                | $I_{N}$          | 1                       | Negative current sense             | 100 mV, the digital current limiting becomes active.                                                                                                                   |

| 4                | GND              | 1                       | Ground                             | All analog and digital signals are referred to this pin.                                                                                                               |

| 5                | GA               | 0                       | Gate                               | Totem-pole output driver, has to be connected with the gate of an external power switch.                                                                               |

| 6                | V <sub>EXT</sub> | I/O                     | External supply                    | Output of the internal CMOS supply. Via $V_{\rm EXT}$ the internal CMOS circuits can be supplied from an external DC-supply in order to reduce chip power dissipation. |

| 7                | C <sub>ss</sub>  | 1                       | Soft start capacitor               | The capacitor at this pin determines the soft start characteristic.                                                                                                    |

| 8                | V <sub>s</sub>   | 1                       | Supply voltage                     | $V_{\rm S}$ is the positive input voltage.                                                                                                                             |

| 9                | PWMP             | I                       | Pulse width modulator              | Non inverting input of the pulse width modulator.                                                                                                                      |

| 10               | EO               | 0                       |                                    | Error amplifier output.                                                                                                                                                |

| 11               | EP               | 1                       | Positive voltage                   | Non inverting input of the error                                                                                                                                       |

| 12               | EN               | 1                       | sense<br>Negative voltage<br>sense | amplifier. Inverting input of the error amplifier.                                                                                                                     |

| 13               | UV               | I                       | Undervoltage detection             | The undervoltage lockout can be programmed via UV.                                                                                                                     |

| 14               | SYNC             | I/O                     | Synchronization                    | This pin can be used as an input for synchronization of the oscillator to an external frequency, or as an output to synchronize multiple devices.                      |

| 15<br>16         | OR<br>OC         | 1                       | R-Oscillator<br>C-Oscillator       | The external timing components of the ramp generator are attached to OR and OC.                                                                                        |

REF PWMP

SYNC OR OC

PSB 2121

GΑ

$c_{ss}$

# **Absolute Maximum Ratings**

| Parameter                                                                                          | Symbol              | Limit Values | Unit |

|----------------------------------------------------------------------------------------------------|---------------------|--------------|------|

| Supply voltage (pin $V_{\rm S}$ ) referred to GND                                                  | V <sub>S</sub>      | 80           | ٧    |

| Analog input voltage (pins $I_{\rm P}$ , $I_{\rm N}$ , PWMP, EP, EN, SYNC, OR, OC) referred to GND | V <sub>I A</sub>    | 6            | V    |

| Reference output current (pin REF)                                                                 | I <sub>O REF</sub>  | -5           | mA   |

| SYNC output current (pin SYNC)                                                                     | I <sub>O SYNC</sub> | <b>-</b> 5   | mA   |

| Error amplifier output current (pin EO)                                                            | $I_{OAmp}$          | -5           | mA   |

| Z-current (pin V <sub>EXT</sub> )                                                                  | I <sub>Z EXT</sub>  | 2            | mA   |

| Output current (pin V <sub>EXT</sub> )                                                             | $I_{OEXT}$          | -5           | mA   |

| Driver output current (pin GA)                                                                     | $I_{DR}$            | -5           | mA   |

| Ambient temperature under bias                                                                     | T <sub>A</sub>      | -25 to 85    | °C   |

| Storage temperature                                                                                | T <sub>stg</sub>    | -40 to 125   | °C   |

## **DC Characteristics**

$T_{\rm A} = 0$  to 70 °C,  $V_{\rm S} = 8$  to 70 V

|                |                  | L    | imit Value | es   |      |                                   |

|----------------|------------------|------|------------|------|------|-----------------------------------|

| Parameter      | Symbol           | min. | typ.       | max. | Unit | Test Conditions                   |

| Supply current | $I_{\mathbb{S}}$ |      | 30         |      | μΑ   | <i>V</i> <sub>S EXT</sub> ≥ 6.3 V |

# Reference V<sub>REF</sub>

| Output voltage        | V <sub>REF O</sub>    | 3.92 | 4.0 | 4.08 | V  | $T_{\rm j} = 25^{\circ}{\rm C},$<br>$I_{\rm L} = 0$ mA,<br>$V_{\rm S} = 40$ V                                 |

|-----------------------|-----------------------|------|-----|------|----|---------------------------------------------------------------------------------------------------------------|

| Line regulation       | V <sub>REF Line</sub> |      |     | 60   | mV | $V_{\rm S} = 20 \text{ to } 60 \text{ V}$<br>$T_{\rm j} = 25 ^{\circ}\text{C},$<br>$I_{\rm L} = 0 \text{ mA}$ |

| Load regulation       | V <sub>REF Load</sub> |      | 20  | 40   | mV | $I_{L} = 0.1 \text{ to } 0.3 \text{ mA}$<br>$V_{S} = 40 \text{ V},$<br>$T_{j} = 25 ^{\circ}\text{C}$          |

| Temperature stability | V <sub>REF TS</sub>   |      | 25  |      | mV | 070°C                                                                                                         |

| Load current          | I <sub>REF Load</sub> |      |     | 0.5  | mA |                                                                                                               |

## DC Characteristics (cont'd)

|           |        | L    | imit Value | es   |      |                 |

|-----------|--------|------|------------|------|------|-----------------|

| Parameter | Symbol | min. | typ.       | max. | Unit | Test Conditions |

## Oscillator/SYNC/OC

$f_{\rm OSC}$  = 20 kHz,  $R_{\rm C}$  = 39 k $\Omega$   $\pm$  1%,  $R_{\rm D}$  = 0  $\Omega$ ,  $C_{\rm r}$  = 1 nF  $\pm$  1%

| Initial accuracy $T_i = 25$ °C |                     |     | ±10 |      | %   |                                                                 |

|--------------------------------|---------------------|-----|-----|------|-----|-----------------------------------------------------------------|

| Voltage stability              |                     |     | 1   | 3    | %   |                                                                 |

| Temperature stability          |                     |     | 5   |      | %   |                                                                 |

| Max. frequency                 | f <sub>max</sub>    | 200 |     |      | kHz | $R_{\rm C} = 27 \text{ k}\Omega$<br>$C_{\rm r} = 39 \text{ pF}$ |

| Sawtooth peak voltage          | V <sub>S</sub>      |     | 3.2 |      | V   | V <sub>S</sub> = 40 V                                           |

| Sawtooth valley voltage        | V <sub>s</sub>      |     | 1.8 |      | V   | $V_{\rm S} = 40 \text{ V}$                                      |

| H-sync output level            | V <sub>SYNC H</sub> | 2.4 |     | 5.25 | V   | $I_{L} = 0.5 \text{ mA}$<br>$V_{EXT} \le 6.3 \text{ V}$         |

| L-sync output level            | V <sub>SYNC L</sub> |     | 0.4 | 0.8  | V   | $I_{L} = 20 \mu\text{A}$                                        |

## Error Amplifier/EO/EP/EN

| Input offset voltage     | V <sub>IO</sub>  |     | 3   | 10  | mV  |                                                        |

|--------------------------|------------------|-----|-----|-----|-----|--------------------------------------------------------|

| Input current            | $I_{I}$          |     |     | 10  | nA  |                                                        |

| Common mode range        | CMR              | 1.8 |     | 4.5 | V   |                                                        |

| DC open loop gain        | G <sub>VO</sub>  | 60  | 70  |     | dB  |                                                        |

| Common mode rejection    | k <sub>CMR</sub> | 60  | 70  |     | dB  |                                                        |

| Unity gain bandwidth     | f                |     | 0.5 |     | MHz | C <sub>L</sub> (pin) ≤ 10 pF                           |

| Supply voltage rejection | k <sub>SVR</sub> |     | 70  |     | dB  |                                                        |

| H-output voltage         | V <sub>OH</sub>  | 4   |     |     | V   | $I_{L} = -100  \mu A$                                  |

| L-output voltage         | V <sub>OL</sub>  |     |     | 1   | V   | $I_{L} = -100 \mu\text{A}$<br>$I_{L} = 10 \mu\text{A}$ |

# Current Limit Comparator $I_{\rm P}/I_{\rm N}$ ,

$T_i = 25$  °C

| Sense voltage                   | V <sub>Sense</sub> | 85 | 100 | 115 | mV | V <sub>S</sub> = 40 V |

|---------------------------------|--------------------|----|-----|-----|----|-----------------------|

| Input bias current              | $I_{I}$            |    |     | 10  | nA |                       |

| Input voltage range             | V <sub>i</sub>     | 0  |     | 1   | V  |                       |

| Response time<br>(signal at GA) | t <sub>Res</sub>   |    | 1   | 2   | μs |                       |

| DO CHARACTERISTICS (CONT. a) | DC | Chara | cteristic | s (cont'd) |

|------------------------------|----|-------|-----------|------------|

|------------------------------|----|-------|-----------|------------|

|                                                                                                                                                |                                                                                                      | L    | Limit Values |                 |            |                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------|--------------|-----------------|------------|-----------------------------------------------------------------------|

| Parameter                                                                                                                                      | Symbol                                                                                               | min. | typ.         | max.            | Unit       | Test Conditions                                                       |

| Pulse Width Modulator                                                                                                                          |                                                                                                      |      |              |                 |            |                                                                       |

| Duty cycle                                                                                                                                     | t <sub>d</sub>                                                                                       | 0    |              | 50              | %          |                                                                       |

| Under Voltage Detection                                                                                                                        | UV                                                                                                   |      |              |                 |            |                                                                       |

| Start up threshold                                                                                                                             | V                                                                                                    | 7    | 8            | 9               | V          | pin UV = $V_{\rm S}$                                                  |

| Threshold hysteresis                                                                                                                           | H <sub>y</sub>                                                                                       |      | 0.3          |                 | ٧          | pin UV = $V_{S}$                                                      |

| Soft Start C <sub>ss</sub>                                                                                                                     |                                                                                                      |      |              |                 |            |                                                                       |

| Charging current                                                                                                                               | C <sub>T</sub>                                                                                       | 2    | 4            | 8               | μΑ         |                                                                       |

| $T_{\rm j} = 25^{\circ}\text{C}$                                                                                                               |                                                                                                      |      |              |                 |            |                                                                       |

|                                                                                                                                                | V <sub>OH</sub>                                                                                      | 4.5  |              |                 | V          | $I_{\text{Source}} = 5 \text{ mA}$                                    |

| High output voltage Low output voltage                                                                                                         | V <sub>OH</sub>                                                                                      | 4.5  |              | 0.4             | V          | $I_{Sink} = 5 \; mA$                                                  |

| High output voltage Low output voltage                                                                                                         |                                                                                                      | 4.5  | 130          | 200             |            | $I_{\rm Sink}$ = 5 mA<br>$C_{\rm L}$ = 220 pF                         |

| I <sub>j</sub> = 25 °C  High output voltage  Low output voltage  Rise time  Fall time                                                          | V <sub>OL</sub> t <sub>r</sub> t <sub>f</sub>                                                        | 4.5  | 130<br>130   |                 | V          | $I_{Sink} = 5 \; mA$                                                  |

| High output voltage  Low output voltage  Rise time                                                                                             | V <sub>OL</sub>                                                                                      | 4.5  |              | 200             | V          | $I_{\rm Sink}$ = 5 mA<br>$C_{\rm L}$ = 220 pF                         |

| High output voltage Low output voltage Rise time Fall time                                                                                     | V <sub>OL</sub> t <sub>r</sub> t <sub>f</sub>                                                        | 4.5  |              | 200             | V ns       | $I_{\rm Sink}$ = 5 mA<br>$C_{\rm L}$ = 220 pF                         |

| High output voltage  Low output voltage  Rise time  Fall time  Output current  External Supply V <sub>EXT</sub>                                | V <sub>OL</sub> t <sub>r</sub> t <sub>f</sub>                                                        | 4.5  |              | 200             | V ns       | $I_{\rm Sink}$ = 5 mA<br>$C_{\rm L}$ = 220 pF                         |

| High output voltage  Low output voltage  Rise time  Fall time  Output current  External Supply V <sub>EXT</sub> Output voltage                 | V <sub>OL</sub> t <sub>r</sub> t <sub>f</sub> I <sub>O</sub>                                         | 4.5  | 130          | 200             | V ns ns mA | $I_{\rm Sink}$ = 5 mA<br>$C_{\rm L}$ = 220 pF<br>$C_{\rm L}$ = 220 pF |

| High output voltage  Low output voltage  Rise time  Fall time  Output current  External Supply V <sub>EXT</sub> Output voltage  Output current | V <sub>OL</sub>   t <sub>r</sub>   t <sub>t</sub>   I <sub>O</sub>   V <sub>O</sub>                  | 6.0  | 130          | 200<br>200<br>5 | V ns ns mA | $I_{\rm Sink}$ = 5 mA<br>$C_{\rm L}$ = 220 pF<br>$C_{\rm L}$ = 220 pF |

| High output voltage  Low output voltage  Rise time  Fall time  Output current                                                                  | V <sub>OL</sub>   t <sub>r</sub>   t <sub>f</sub>   I <sub>O</sub>   V <sub>O</sub>   I <sub>O</sub> |      | 130          | 200 200 5       | V ns ns mA | $I_{\rm Sink}=5$ mA<br>$C_{\rm L}=220$ pF<br>$C_{\rm L}=220$ pF       |

#### **Application Information**

#### **Undervoltage Lockout**

The undervoltage lockout circuit protects the PSB 2121 and the power devices from inadequate supply voltage. If  $V_{\rm S}$  is too low, the circuit disables this output driver. This ensures that all control functions have been stabilized in the proper state when the turn on voltage (8 V) is reached, and it prevents from the possibility of start up glitches. The undervoltage lockout is programmable by connecting a Z-diode between  $V_{\rm S}$  and UV from 8 V up to 70 V. If UV is connected to  $V_{\rm S}$  the default undervoltage lockout is 8 V.

#### Voltage Reference

The reference regulator of the PSB 2121 is based on a temperature compensated bandgap. This circuitry is fully active at supply voltages above +6.0 V and provides up to 0.5 mA of load current to external circuitry at +4.0 V. This reference has to be buffered by an external capacitor > 0.5  $\mu F$ .

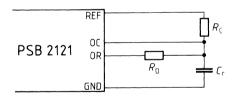

#### Oscillator

The oscillator frequency is programmed by three components:  $R_{\text{C}}$ ,  $C_{\text{r}}$  and  $R_{\text{D}}$  as shown in **figure 2**. The oscillator timing capacitor  $C_{\text{T}}$  is charged by  $V_{\text{REF}}$  through  $R_{\text{C}}$  and discharged by  $R_{\text{D}}$ . ( $R_{\text{D}}$  is series-connected with an internal 9 k $\Omega$  discharge-resistor). So the rise-time and the fall-time of the sawtooth oscillator can be programmed individually.

Figure 2

The PSB 2121 could be synchronized by the rising edge of the SYNC signal, whose frequency must be 10% higher than the free run frequency, determined by the RC-components. The SYNC pin can also be used as a trigger-output. As long as the capacitor of the sawtooth oscillator is discharged, SYNC is high. So multiple devices can be synchronized together by programming one master unit for the desired frequency.

Notice that the frequency of the output driver is half the oscillator frequency.

#### **Soft Start Circuit**

The soft start circuit protects the power transistors and rectifier diodes from high current surges during power supply turn-on. When the supply voltage is connected to the PSB 2121 the undervoltage lockout circuit holds the soft start capacitor voltage at zero. When the supply voltage reaches normal operating range an internal 4  $\mu$ A current source will charge the external soft start capacitor. As the soft start voltage ramps up to +5 V, the duty cycle of the PWM linearly increases to whatever value regulation loop requires.

#### **Pulse Width Modulator**

The pulse width modulator compares the sawtooth-voltage of the oscillator output with the input signal at PWMP and with the voltage of the external soft start capacitor at  $C_{\rm SS}$  (see figure 1).

#### **Error Amplifier**

Conventional operational amplifier for closed-loop gain and phase compensation. Low output impedance: unity-gain stable.

#### **Control Logic**

The control logic inhibits double pulses during one duty cycle and limits the maximum duty cycle to 50%.

#### **Current Limiting**

A differential input comparator terminates individual output pulses each time when the sense voltage rises above threshold.

When sense voltage rises to 100 mA above threshold a shutdown signal is sent to the control logic.

#### **CMOS Supply**

An integrated 6 V linear voltage regulator supplies the internal low-voltage CMOS circuits from the input voltage. This supply voltage is connected to pin  $V_{\rm EXT}$  and has to be buffered by an external capacitor ( $C_{\rm min}=1~\mu{\rm F}$ ). Power dissipation of the linear voltage regulator can be reduced, if an external supply is used for that purpose by connecting it to pin  $V_{\rm EXT}$ . If the input voltage at  $V_{\rm EXT}$  reaches 6.3 V the internal linear voltage regulator turns off and the internal CMOS circuits are fed from the external voltage. In this case the input current at  $V_{\rm EXT}$  is approx. 0.5 mA.

**Note:** An internal 7.5 V Z-diode protects the  $V_{\text{EXT}}$  input against overvoltage. The maximum Z-current is 2 mA! So if the external CMOS supply isn't stabilized the input current must be limited (e.g. by a resistor).

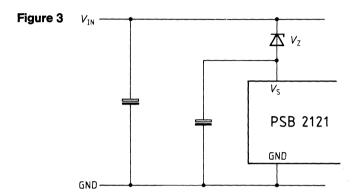

#### **Extended Input Voltage Range**

Some DC/DC-converter applications require a higher input voltage than the maximum supply voltage of the PSB 2121 which is limited to 70 V. **Figure 3** shows a method to extend the input voltage range by connecting a Z-diode between the input voltage and  $V_S$  of the PSB 2121.

If the PSB 2121 is fed via  $V_{\rm EXT}$ , the input current at pin  $V_{\rm S}$  is approx. 30  $\mu$ A. The additional power losses are accordingly 30  $\mu$ A ·  $V_{\rm Z}$ ; the minimum input voltage is  $V_{\rm Z}$  + 8 V.