# SIEMENS

## ISDN Subscriber Access Controller (ISAC-P)

#### **Preliminary Data**

CMOS IC

**PEB 20950**

| Туре        | Ordering Code | Package        |

|-------------|---------------|----------------|

| PEB 20950-C | Q67100-H8613  | C-DIP-40       |

| PEB 20950-N | Q67100-H8614  | PL-CC-44 (SMD) |

| PEB 20950-P | Q67100-H8550  | P-DIP-40       |

The PEB 20950 ISAC<sup>TM</sup>-P is a combination transceiver/HDLC controller for ISDN terminals in a two-wire PBX environment. Transceiver functions are performed according to the two-wire PBX industry standard  $U_{p0}$  interface. This corresponds to all of the functions available on the PEB 2095 IBC. Similarly, the HDLC protocol is processed as described for the PEB 2070 ICC. The ISAC-P represents both the IBC and ICC on a single IC.

#### Features

- Half duplex burst mode two-wire transceiver

- AMI line code

- Adaptive line equalization

- High-level support of LAPD protocol

- FIFO buffer (2x64 bytes) for efficient transfer of D-channel packets

- IOM<sup>®</sup> interface to other ICs

- Switching of test loops

- 8-bit μP interface

- Advanced CMOS technology

- Low power consumption

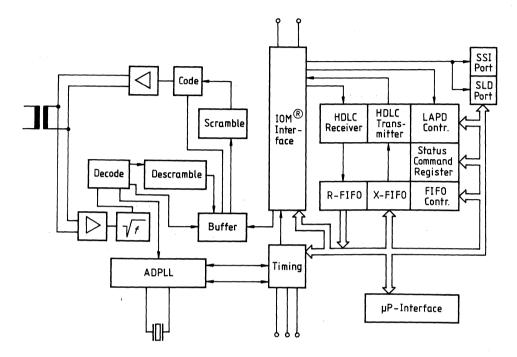

#### **ISAC-P Block Diagram**

## PEB 20950

#### **Pin Definitions and Functions**

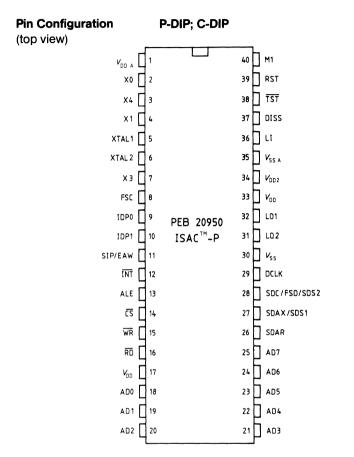

| Pin No.<br>P-DIP | Symbol          | Input (I)<br>Output (O) | Function                                                                                                                                     |

|------------------|-----------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | V <sub>DD</sub> | 1                       | Analog power supply (+5 V)                                                                                                                   |

| 2                | XO              | 0                       | Multifunctional Pin<br>M1 = 1: Software programmable output<br>M1 = 0: 3.84-MHz clock output                                                 |

| 3                | X4              | 1/0                     | Multifunctional Pin<br>M1 = 1: PFOFF<br>M1 = 0: 2.56-MHz clock output                                                                        |

| 4                | X1              | 0                       | Multifunctional Pin<br>M1 = 1: 15.36-MHz clock output<br>M1 = 0: 1.536-MHz clock output in IOM-1 mode;<br>768-kHz clock output in IOM-2 mode |

Siemens Components, Inc.

| Pin No.<br>P-DIP | Symbol  | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|---------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5                | XTAL1   | 1                       | External Crystal or external clock input                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6                | XTAL2   | 0                       | External Crystal output                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7                | Х3      | I                       | Multifunctional Pin<br>M1 = 1: MPF input<br>M1 = 0: ENCK input                                                                                                                                                                                                                                                                                                                                                                                           |

| 8                | FSC     | I/O                     | IOM Interface Frame Synchronization<br>M1 = 1: 8-kHz input clock<br>M1 = 0: 8-kHz output clock                                                                                                                                                                                                                                                                                                                                                           |

| 9                | IDP0    | 1/0                     | IOM Interface Data Port 0<br>LT application: Data upstream line<br>TE application: Data downstream line                                                                                                                                                                                                                                                                                                                                                  |

| 10               | IDP1    | I/O                     | IOM Interface Data Port 1<br>LT application: Data downstream line<br>TE application: Data upstream line                                                                                                                                                                                                                                                                                                                                                  |

| 11               | SIP/EAW | 1/0                     | <b>SLD Interface Port,</b> IOM-1 mode<br>This line transmits and receives serial data at standard<br>TTL or CMOS level.<br>External Awake, terminal specific functions<br>If a falling edge on this input is detected, the ISAC-P<br>generates an interrupt and/or a reset pulse                                                                                                                                                                         |

| 12               | INT     | OD                      | Interrupt Request<br>The signal is activated, when the ISAC-P requests<br>an interrupt.<br>The CPU may determine the particular source and<br>cause of interrupt by reading the ISAC-P interrupt<br>status register (ISTA, EXIR).<br>INT is an open drain output, thus the interrupt request<br>outputs of several ISAC-P's can be connected to<br>one interrupt input in a "wired-or" combination. This<br>pin must be connected to a pull up resistor. |

| 13               | ALE     | I                       | Address Latch Enable<br>A high on this line indicates an address on the external<br>address/data bus, which will select one of the<br>ISAC-P's internal registers. The address is latched<br>with the falling edge of ALE.                                                                                                                                                                                                                               |

## Pin Definitions and Functions (cont'd)

| Pin No.<br>P-DIP                             | Symbol                                               | Input (I)<br>Output (O)                       | Function                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------|------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14                                           | CS                                                   | I                                             | Chip Select<br>A low signal selects the ISAC-P for a read/write<br>operation.                                                                                                                                                                                                                                                                                                  |

| 15                                           | WR                                                   | 1                                             | <b>Write</b><br>This signal indicates a write operation. When $\overline{CS}$ is active, the ISAC-P loads an internal register with data provided via the address/data bus.                                                                                                                                                                                                    |

| 16                                           | RD                                                   | I                                             | <b>Read</b><br>This signal indicates a read operation. When the ISAC-P is selected via $\overline{CS}$ the read signal enables the bus drivers to put data from an internal register on the address/data bus.                                                                                                                                                                  |

| 17                                           | V <sub>DD</sub>                                      | 1                                             | Power supply (+5 V)                                                                                                                                                                                                                                                                                                                                                            |

| 18<br>19<br>20<br>21<br>22<br>23<br>24<br>25 | AD0<br>AD1<br>AD2<br>AD3<br>AD4<br>AD5<br>AD6<br>AD7 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | Address Data Bus<br>The multiplexed address data bus transfers data and command/status information between the ISAC-P and the $\mu$ P system.                                                                                                                                                                                                                                  |

| 26                                           | SDAR                                                 | 1                                             | Serial Data Port A Receive<br>Serial data is received on this pin at standard TTL<br>or CMOS level. An integrated pull-up circuit enables<br>connection of an open drain/open collector driver<br>without an external pull-up resistor.<br>SDAR is used only if IOM-1 mode is selected.                                                                                        |

| 27                                           | SDAX/<br>SDS1                                        | 0                                             | Serial Data Port A Transmit, IOM-1 mode<br>Transmit data is shifted out via this pin at standard<br>TTL or CMOS level.<br>Serial Data Strobe 1, IOM-2 mode<br>A programmable strobe signal, selecting either one<br>of two B/IC channels on IOM-2 interface, is supplied<br>via this line. After reset SDAX/SDS1 remains at logical 0<br>until a write access to SPCR is made. |

### Pin Definitions and Functions (cont'd)

## Pin Definitions and Functions (cont'd)

| Pin No.<br>P-DIP | Symbol           | input (i) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28               | SCA/FSD<br>SDS2  | 0         | <ul> <li>Serial Clock Port A, IOM-1 timing mode 0</li> <li>A 128-kHz data clock signal for serial port A is supplied.</li> <li>Frame Sync Delayed, IOM-1 timing mode 1</li> <li>A 8-kHz synchronization signal, delayed by 1/8 of a frame, for serial port B (IOM-1 interface) is supplied.</li> <li>In this mode a minimal delay for B1 and B2 channels is guaranteed.</li> <li>Serial Data Strobe 2, IOM-2 mode</li> <li>A programmable strobe signal, selecting either one or two B/IC channels on IOM-2 interface, is supplied via this line. After reset, SCA/FSD/SDS2 remains at logical 0 until a write access to SPCR is made.</li> </ul> |

| 29               | DCLK             | 1/0       | IOM Interface Data Clock<br>M1 = 1: input 512-kHz IOM-1 mode<br>input 4.096-kHz IOM-2 mode<br>M1 = 0: output 512-kHz IOM-1 mode<br>output 1.536-MHz IOM-2 mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 30               | V <sub>ss</sub>  | 1         | Ground (0 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 31               | LO2              | 0         | Line Transmitter Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 32               | LO1              | 0         | Line Transmitter Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 33               | V <sub>DD</sub>  | 1         | Power supply (+5 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 34               | V <sub>DD2</sub> | 0         | 2.5 V output; connected to both $V_{\rm DD}$ and $V_{\rm SS}$ via 10 nF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 35               | V <sub>SSA</sub> | l         | Analog ground (0 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 36               | LI               | 1         | Line Receiver Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 37               | DISS             | 0         | Disable Supply Indication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 38               | TST              | I         | Device Test Pin: tie always high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 39               | RES              | 1/0       | <b>RESET</b><br>A high signal on this input forces the ISAC-P into<br>reset state. The minimum pulse length is four clock<br>periods of DCLK.<br>If the terminal specific functions are enabled, the<br>ISAC-P may also supply a reset signal.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 40               | M1               | I         | <b>Operating Mode for IBC-Part.</b><br>M1 = 1: IBC in LT mode<br>M1 = 0: IBC in TE mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Siemens Components, Inc.