## ISDN Layer-2 Protocol Controllers

ISDN Communications Controller (ICC)

## **General Description**

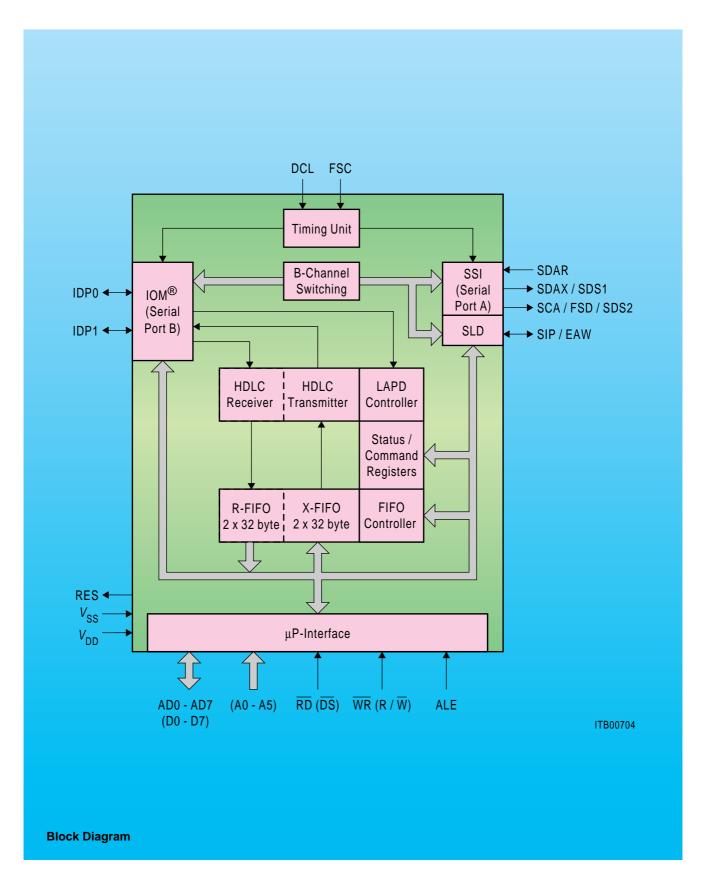

While the IOM structure supports high flexibility with respect to layer-1 of data transmission, the ISDN communications controller can be used in all applications for link access protocol control. This is of great importance regarding production volume, software continuity and engineering effort necessary for the use of the complex circuit. For further reduction of software, high-level layer-2 support has been a main target of circuit definition.

D-channel protocol handling is the main task of the ICC. Its characteristic features are determined by an on-chip LAPD controller and a sophisticated FIFO-structure. The LAPD controller performs multiframe operation largely autonomously with a window size of 1. All S- and I-frames, including the address and control fields, are evaluated in the ICC. Depending on the status of the controller, positive or negative acknowledgements are generated without interrupting the CPU. When the procedure is terminated, an interrupt status is generated to inform the CPU of the status of the procedure. To enable the ICC device to be used in complex protocol applications with window size of up to 7, a transparent mode is implemented. In this mode the layer-2 headers are transferred transparently to the CPU.

The synchronization of the 16-kbit/s D-channel with the CPUbus is performed by buffers with a capacity of 64 bytes per direction. Sophisticated buffer controllers allow overlapping input/output operation, which ensures that the maximum packet length is not limited by the buffer size.

This feature greatly reduces the dynamic load of the microprocessor system.

| Туре       | Package                          |

|------------|----------------------------------|

| PEB 2070-N | P-LCC-28-1 (SMD)                 |

| PEB 2070-P | P-DIP-24-1 (not for new designs) |

| PEF 2070-N | P-LCC-28-1 (SMD)                 |

## Features

- · High-level support of LAPD-protocol

- FIFO-buffer (64 bytes per direction) for efficient transfer of D-channel messages

- IOM interface compatible (IOM-1 or IOM-2)

- Standard parallel microprocessor interface

- · Support of activation/deactivation procedure

- Variety of operating modes

- $\mu$ P access to B-channels and IOM-intercommunication channels

- Control of peripheral devices via IOM Monitor and C/lchannel protocols

- 2- $\mu$ m CMOS technology and low power consumption: Standby: 2 mW

- Active: 4 mW at 512 kHz