# **ICs for Communications**

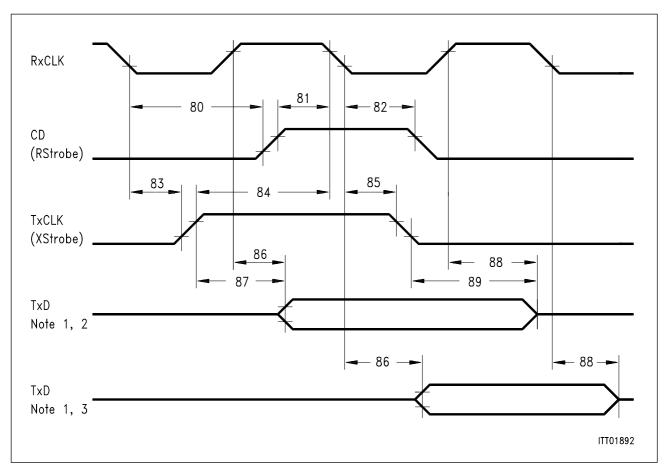

Enhanced Serial Communication Controller with 8 Channels ESCC8

SAB 82538

SAF 82538

Version 2.2

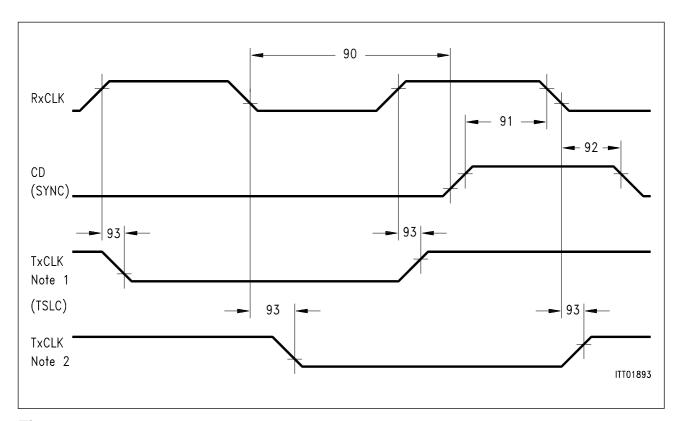

User's Manual 03.95

#### Edition 03.95

This edition was realized using the software system FrameMaker.

Published by Siemens AG, Bereich Halbleiter, Marketing-Kommunikation, Balanstraße 73, 81541 München

© Siemens AG 1995. All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### **Packing**

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

| SAB 8253<br>SAF 8253<br>Revision I                                                                       | 8                                                                                                            | Current Version: 03.95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Previous Version: U                                                                                      |                                                                                                              | User's Manual 01.94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Page (in<br>Version<br>01.94)                                                                            | Page<br>(in new<br>version                                                                                   | Subjects (changes since last revision)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

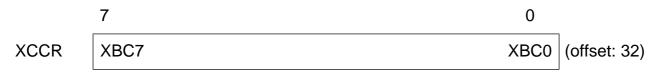

| 11<br>13<br>14<br>19<br>22<br>54<br>58<br>61<br>65<br>86<br>86<br>110<br>113<br>126<br>127<br>145<br>157 | 11<br>13<br>14<br>19<br>22<br>54<br>58<br>61<br>65<br>86<br>86<br>111<br>114<br>127<br>129<br>147/148<br>159 | $\begin{array}{c} V_{\rm DD} \ {\rm and} \ V_{\rm SS} \ {\rm pin} \ {\rm configuration} \\ \hline {\rm RD/DS} \ {\rm Description} \\ \hline {\rm RES} \ {\rm pin} \ {\rm number} \\ \hline \hline {\rm DACKx} \ {\rm Description} \\ \hline V_{\rm DD} \ {\rm and} \ V_{\rm SS} \ {\rm numbers} \\ \hline {\rm Transparent} \ {\rm Mode} \ 1, \ {\rm Address} \ {\rm Recognition} \\ \hline {\rm Transmitter} \ {\rm Interrupts}, \ {\rm Figure} \ 21 \\ \hline {\rm Transmitter} \ {\rm Interrupts}, \ {\rm Figures} \ 23/24 \\ \hline {\rm Transmitter} \ {\rm Interrupts}, \ {\rm Figures} \ 28/29 \\ \hline {\rm Note} \ {\rm in} \ {\rm description} \ {\rm of} \ {\rm Clock} \ {\rm Mode} \ 5 \\ \hline {\rm CD-signal}, \ {\rm Figure} \ 35 \\ \hline {\rm Interrupt} \ {\rm Driven} \ {\rm Reception} \ {\rm Sequence}, \ {\rm Figure} \ 47 \\ \hline {\rm CCR4} \ {\rm Register} \ {\rm Addresses} \\ \hline {\rm RHCR} \ {\rm Register} \ {\rm Description} \\ \hline {\rm XBC} \ {\rm Register} \ {\rm Description} \\ \hline {\rm XMR} \ {\rm Interrupt} \ {\rm Description} \\ \hline {\rm RFRD} \ {\rm Command} \ {\rm Description} \\ \hline {\rm RFRD} \ {\rm Command} \ {\rm Description} \\ \hline \end{array}$ |  |

| 164<br>178<br>190<br>198<br>211<br>228<br>236<br>238<br>241                                              | 166<br>181<br>194<br>201<br>214<br>231<br>239<br>241<br>244                                                  | RFRD Command Description RBC Register Description TCD Interrupt Description RFRD Command Description RBC Register Description TCD Interrupt Description TCD Interrupt Description Timings $t_{\text{p (DRT)}}$ , $t_{\text{SU (IE)}}$ Timing $t_{\text{SU (IE)}}$ Timing $t_{\text{p (PV-INT)}}$ Number of Timing $t_{\text{C (XC)}}$ Minor Misprints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

#### **Data Classification**

#### **Maximum Ratings**

Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit.

#### **Characteristics**

The listed characteristics are ensured over the operating range of the integrated circuit. Typical characteristics specify mean values expected over the production spread. If not otherwise specified, typical characteristics apply at  $T_A = 25$  °C and the given supply voltage.

### **Operating Range**

In the operating range the functions given in the circuit description are fulfilled.

For detailed technical information about "Processing Guidelines" and "Quality Assurance" for ICs, see our "Product Overview".

| Table o | Table of Contents Page                          |     |  |  |  |

|---------|-------------------------------------------------|-----|--|--|--|

| Introdu | ction                                           | 7   |  |  |  |

| 1       | General Features                                | 8   |  |  |  |

| 1.1     | Pin Definitions and Function                    |     |  |  |  |

| 1.2     | Logic Symbol                                    |     |  |  |  |

| 1.3     | Functional Block Diagram                        |     |  |  |  |

| 1.4     | System Integration                              |     |  |  |  |

| 1.4.1   | General Aspects                                 |     |  |  |  |

| 1.4.2   | Environment                                     | .26 |  |  |  |

| 1.4.2.1 | ESCC8 with SAB 80188 Microprocessor             | .26 |  |  |  |

| 1.4.2.2 | ESCC8 with 80386                                |     |  |  |  |

| 1.4.2.3 | ESCC8 with MC 68020, 68030                      | .28 |  |  |  |

| 1.4.2.4 |                                                 |     |  |  |  |

| 2       | Functional Description                          | 22  |  |  |  |

| 2.1     | General                                         |     |  |  |  |

| 2.1     | Microprocessor Interface                        |     |  |  |  |

| 2.2.1   | Register Set                                    |     |  |  |  |

| 2.2.1   | Data Transfer Modes                             |     |  |  |  |

| 2.2.2   | Interrupt Interface                             |     |  |  |  |

| 2.2.3.1 | Priority Structure                              |     |  |  |  |

| 2.2.3.1 | Interrupt Polling                               |     |  |  |  |

| _       | Vectored Interrupt Structure                    |     |  |  |  |

| 2.2.4   | DMA Interface                                   |     |  |  |  |

| 2.2.5   | FIFO Structure                                  |     |  |  |  |

| 2.3     | HDLC/SDLC Serial Mode                           |     |  |  |  |

| 2.3.1   | Operating Modes                                 |     |  |  |  |

| 2.3.2   | Procedural Support (Layer-2 Functions)          |     |  |  |  |

| 2.3.2.1 | · · · · · · · · · · · · · · · · · · ·           |     |  |  |  |

|         | Half-Duplex SDLC-NRM Operation                  |     |  |  |  |

| 2.3.2.3 |                                                 |     |  |  |  |

| 2.3.3   | SDLC Loop                                       |     |  |  |  |

| 2.3.4   | Special Functions                               |     |  |  |  |

| 2.3.4.1 | Shared Flags                                    | .68 |  |  |  |

| 2.3.4.2 | Preamble Transmission                           | .68 |  |  |  |

|         | CRC-32                                          |     |  |  |  |

| 2.3.4.4 | Extended Transparent Transmission and Reception | .69 |  |  |  |

| 2.3.4.5 | Cyclic Transmission (Fully Transparent)         | .69 |  |  |  |

| 2.3.4.6 | Continuous Transmission (DMA Mode only)         | .70 |  |  |  |

|         | Receive Length Check Feature                    |     |  |  |  |

|         | One Bit Insertion                               |     |  |  |  |

| 2.3.4.9 | CRC ON/OFF Feature (version 2 upward)           | .71 |  |  |  |

| Table o  | f Contents (cont'd)                              | Page |

|----------|--------------------------------------------------|------|

| 2.3.4.10 | Receive Address Handling (version 2 upward)      | 72   |

| 2.4      | Asynchronous Serial Mode                         |      |

| 2.4.1    | Character Frame                                  | 73   |

| 2.4.2    | Data Reception                                   | 73   |

| 2.4.2.1  | Operating Modes                                  | 73   |

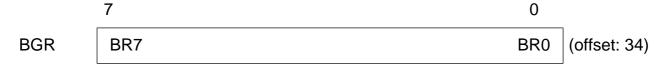

| 2.4.2.2  | Storage of Data                                  | 74   |

| 2.4.3    | Data Transmission                                | 75   |

| 2.4.4    | Special Features                                 | 75   |

| 2.4.4.1  | Break Detection/Generation                       | 75   |

| 2.4.4.2  | Flow Control by XON/XOFF (version 2 upward)      | 75   |

| 2.4.4.3  | Continuous Transmission (DMA Mode only)          | 77   |

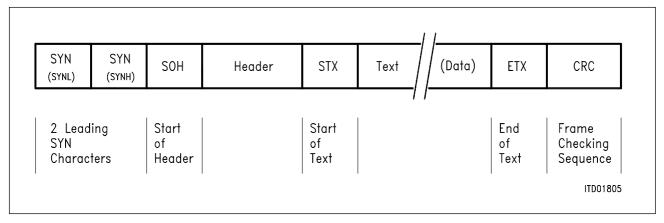

| 2.5      | Character Oriented Serial Mode (MONOSYNC/BISYNC) | 78   |

| 2.5.1    | Data Frame                                       | 78   |

| 2.5.2    | Data Reception                                   | 79   |

| 2.5.3    | Data Transmission                                | 80   |

| 2.5.4    | Special Functions                                | 81   |

| 2.5.4.1  | Preamble Transmission                            | 81   |

| 2.5.4.2  | Continuous Transmission (DMA Mode only)          | 81   |

| 2.5.4.3  | CRC Parity Inhibit                               | 81   |

| 2.6      | Serial Interface (Layer-1 functions)             | 82   |

| 2.6.1    | Clock Modes                                      |      |

| 2.6.2    | Clock Recovery (DPLL)                            | 87   |

| 2.6.3    | Bus Configuration                                |      |

| 2.6.3.1  | Bus Access Procedure                             | 91   |

| 2.6.3.2  | Collisions                                       | 92   |

| 2.6.3.3  | Priority (HDLC/SDLC Mode Only)                   | 93   |

| 2.6.3.4  | Timing Modes                                     | 93   |

| 2.6.3.5  | Timing Modes                                     | 94   |

| 2.6.4    | Data Encoding                                    | 95   |

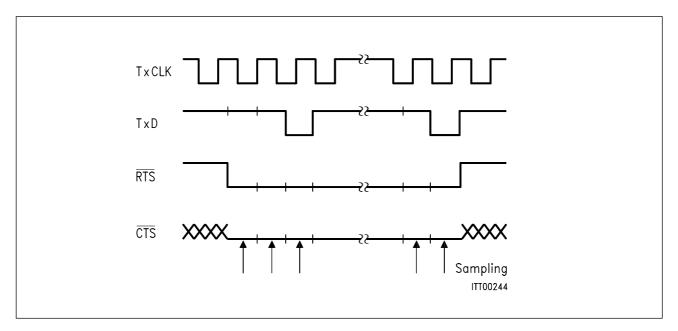

| 2.6.5    | Modem Control Functions (RTS/CTS, CD)            | 97   |

| 2.6.5.1  | RTS/CTS Handshaking                              |      |

| 2.6.5.2  | Carrier Detect (CD) Receiver Control             | 98   |

| 2.6.6    | Test Mode                                        | 99   |

| 2.7      | Universal Port                                   | 99   |

| 3        | Operational Description                          | 100  |

| 3.1      | Reset                                            |      |

| 3.2      | Initialization                                   | 102  |

| 3.3      | Operational Phase                                | 105  |

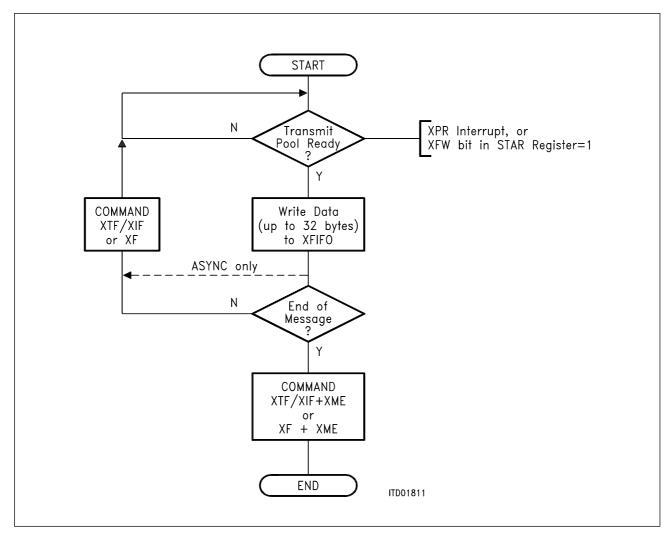

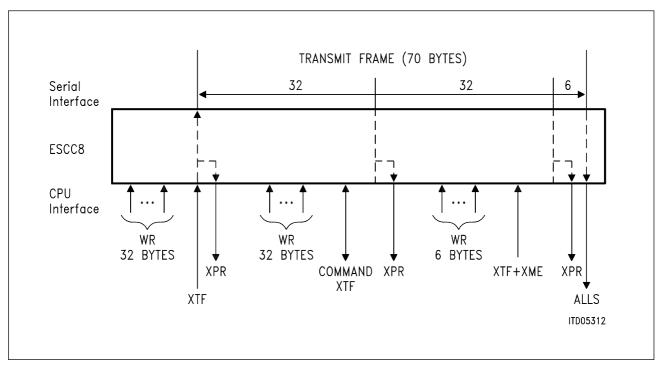

| 3.3.1    | Data Transmission                                | 105  |

| 3.3.1.1  | Interrupt Mode                                   | 105  |

| 3312     | DMA Mode                                         | 107  |

| Table o                                                                                                                           | of Contents (cont'd)                                                                                                                                                                                                                                                                          | Page                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 3.3.2<br>3.3.2.1<br>3.3.2.2                                                                                                       | Data Reception                                                                                                                                                                                                                                                                                | 108                                                         |

| 4<br>4.1<br>4.1.1<br>4.1.2<br>4.2<br>4.2.1<br>4.2.2<br>4.3<br>4.3.1<br>4.3.2                                                      | Detailed Register Description Status/Control Registers in HDLC Mode Register Addresses Register Definitions Status/Control Registers in ASYNC Mode Register Addresses Register Definitions Status/Control Registers in BISYNC Mode Register Addresses Register Addresses Register Definitions | 112<br>113<br>153<br>153<br>154<br>188                      |

| 5<br>5.1<br>5.2<br>5.3<br>5.4<br>5.4.1<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.3.1<br>5.4.3.2<br>5.4.3.3<br>5.4.3.4<br>5.4.3.5<br>5.4.4 | Transmit Cycle Timing                                                                                                                                                                                                                                                                         | 220<br>221<br>222<br>223<br>239<br>240<br>242<br>244<br>247 |

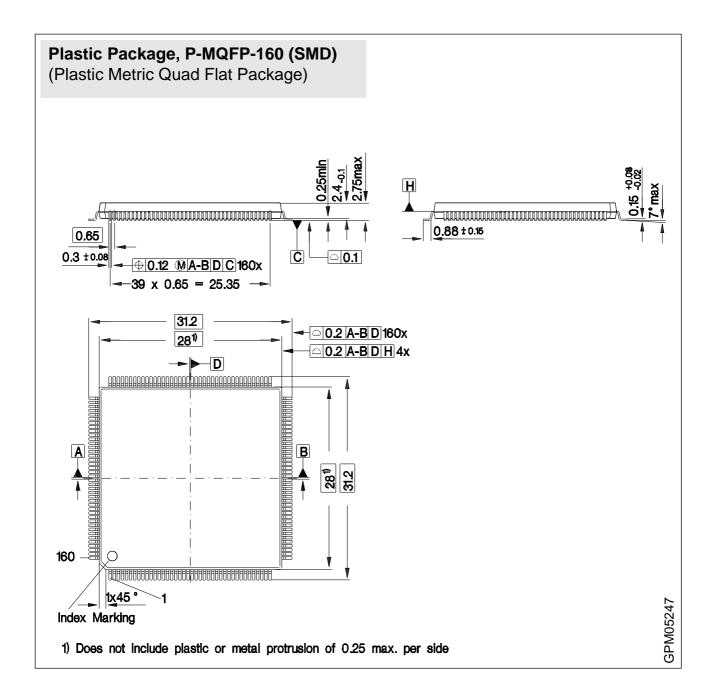

| 6                                                                                                                                 | Package Outlines                                                                                                                                                                                                                                                                              | 251                                                         |

| 7                                                                                                                                 | Appendix                                                                                                                                                                                                                                                                                      | 252                                                         |

#### Introduction

The Enhanced Serial Communication Controller ESCC8 (SAB 82538) is a data communication device with eight serial channels. It has been designed to implement high-speed communication links and to reduce hardware and software overhead needed for serial synchronous/asynchronous communications.

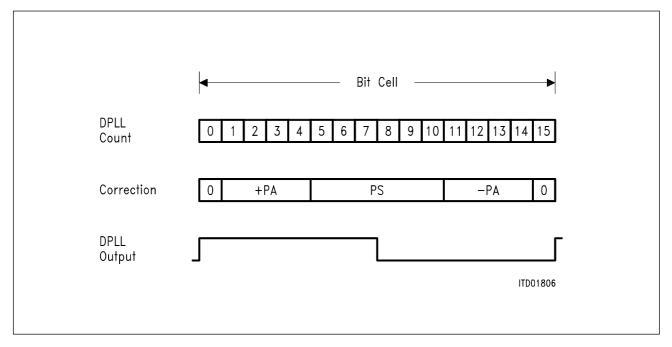

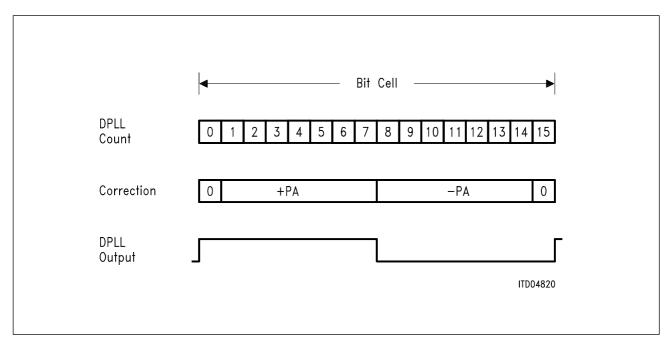

Each channel contains an independent clock generator, DPLL, encoder/decoder and a programmable protocol part. Data communication with asynchronous, synchronous character oriented, and HDLC based protocols with extended support of X.25 "0", the ISDN "0", and SDLC protocols is implemented. Like the dual channel ESCC2 (SAB 82532) the ESCC8 is capable of handling a large set of layer-2 protocol functions independently of the host processor.

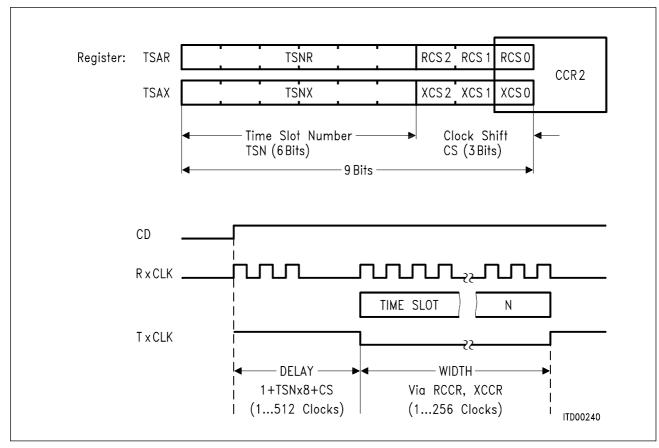

The version 82538H-10 of the Enhanced Serial Communication Controller (ESCC8) opens a wide area for applications which use time division multiplex methods (e.g. time-slot oriented PCM systems, systems designed for packet switching, ISDN applications) by its programmable telecom-specific features. Specifically in one of its timing modes (clock mode 5), which is applicable to all serial modes (HDLC/SDLC, ASYNC, BISYNC), the ESCC8 can transmit or receive data packets in one of up to 64 time-slots of programmable width.

The device is controlled via a parallel 16-bit wide interface which is directly compatible with the most popular 8/16 bit microprocessors (Siemens/Intel or Motorola type). The internal FIFOs (64 bytes per direction and channel) with additional DMA capability provide a powerful interface to the higher layers implemented in a microcontroller. For interrupt controlled systems, the ESCC8 supports daisy chaining and interrupt vector generation.

The ESCC8 is fabricated using Siemens advanced CMOS technology and is available in a P-MQFP-160 package.

### **Applications**

- Universal, multiprotocol communication boards

- Asynchronous and synchronous terminal cluster controllers

- LAN gateways and bridges

- Multiplexers, cross-connect points, DMI boards

- Time slotted packet networks

- Packet switches, packet assemblers/disassemblers

# **Enhanced Serial Communication Controller** (ESCC8)

SAB 82538 SAF 82538

Preliminary Data CMOS IC

#### 1 General Features

### **Serial Interface**

- Eight independent full duplex serial channels

- On chip clock generation or external clock source

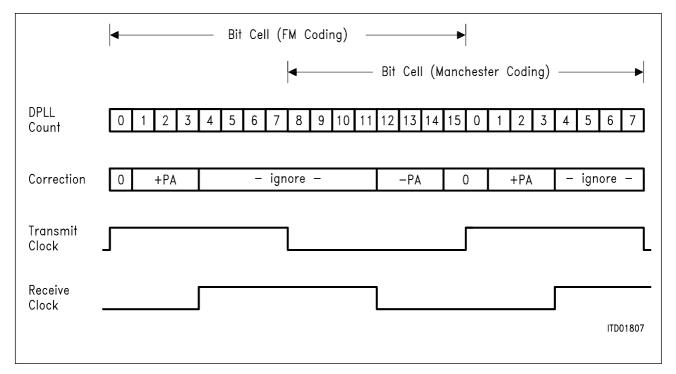

- On chip DPLL for clock recovery of each channel

- Eight independent baud rate generators

- Independent time-slot assignment for each channel with programmable time-slot length (1-256 bits)

- Async., sync. character oriented (MONOSYNC / BISYNC) or HDLC/SDLC modes (including SDLC LOOP)

- Transparent receive/transmit of data bytes without framing

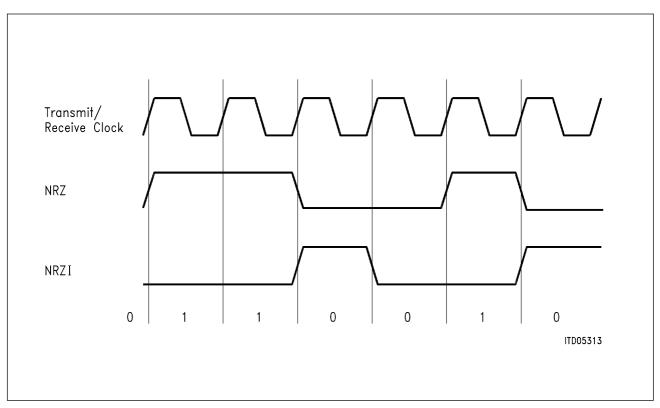

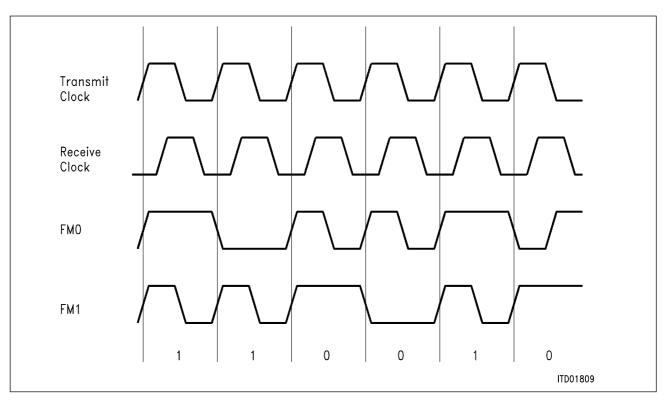

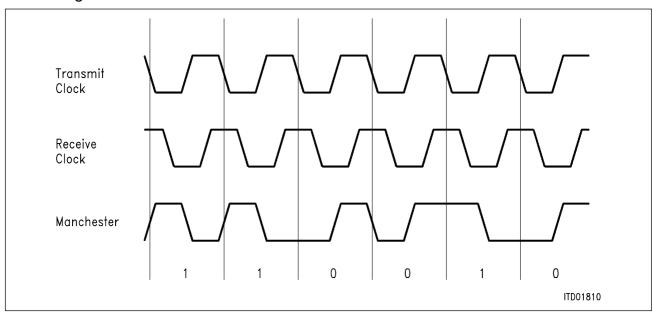

- NRZ, NRZI, FM and Manchester encoding

- Modem control lines (RTS, CTS, CD)

- CRC support:

- HDLC/SDLC: CRC-CCITT or CRC-32 (automatic handling for transmit/receive direction)

- BISYNC: CRC-16 or CRC-CCITT (support for transmit direction)

- Support of bus configuration by collision detection and resolution

| Туре           | Ordering Code | Package    | Max. Data Rate<br>clocked |             | Time-<br>Slot |

|----------------|---------------|------------|---------------------------|-------------|---------------|

|                |               |            | ext.                      | int. (DPLL) | Mode          |

| SAB 82538 H    | Q67100-H6440  | P-MQFP-160 | 2 Mbit/s                  | 2 Mbit/s    | no            |

| SAB 82538 H-10 | Q67100-H6441  | P-MQFP-160 | 10 Mbit/s                 | 2 Mbit/s    | yes           |

| SAF 82538 H-10 | Q67100-H6442  | P-MQFP-160 | 10 Mbit/s                 | 2 Mbit/s    | yes           |

- Statistical multiplexing

- Continuous transmission of 1 to 32 bytes possible

- Programmable Preamble (8 bit) with selectable repetition rate (HDLC/SDLC and BISYNC)

- Data rate up to 10 Mbit/s

- Master clock mode with data rate up to 4 Mbit/s

### **Protocol Support (HDLC / SDLC)**

- Various types of protocol support depending on operating mode

- Auto mode (automatic handling of S and I frames)

- Non-auto mode

- Transparent mode

- Handling of bit oriented functions

- Support of LAPB / LAPD / SDLC / HDLC protocol in auto mode (I- and S-frame handling)

- Modulo 8 or modulo 128 operation

- Programmable time-out and retry conditions

- Programmable maximum packet size checking

#### **MP Interface and Ports**

- 64 byte FIFOs per channel and direction (byte or word access)

- 8/16 bit microprocessor bus interface (Intel or Motorola type)

- All registers directly accessible (byte and word access)

- Efficient transfer of data blocks from/to system memory via DMA or interrupt request

- Support of Daisy Chaining and Slave Operation with Interrupt Vector generation

- 28-bit programmable universal I/Os

### **General**

- Advanced CMOS technology

- Low power consumption: active 200 mW at 2 MHz/standby 20 mW (typical values)

- P-MQFP-160 Package

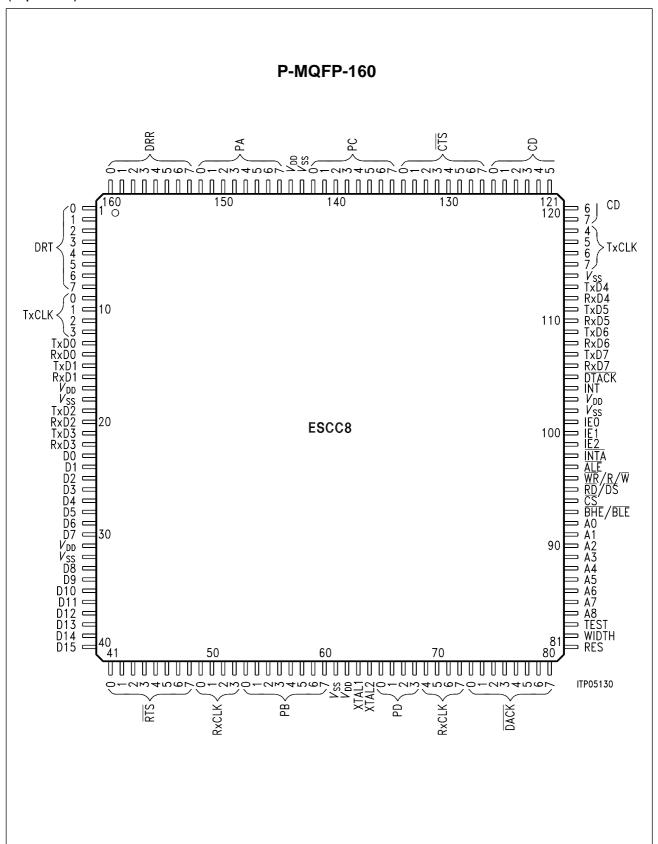

### **Pin Configuration of ESCC8**

(top view)

### 1.1 Pin Definitions and Function

| Pin No.         | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------|--------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 92 84           | A0 A8  | I                       | Address Bus These inputs interface with nine bits of the system's address bus to select one of the internal registers for read or write.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 23 30,<br>33 40 | D0 D15 | I/O                     | Data Bus Bi-directional three-state data lines which interface with the system's data bus. Their configuration is controlled by the level of pin WIDTH:  - 8-bit mode (WIDTH = 0): D0 D7 are active.  D8 D15 are in high impedance and have to be connected to $V_{\rm DD}$ or $V_{\rm SS}$ .  - 16-bit mode (WIDTH = 1): D8D15 are active. In case of byte transfers, the active half of the bus is determined by A0 and BHE/BLE and the selected bus interface mode (via ALE). The unused half is in high impedance. For detailed information, refer to chapter 2.2.1. |

| 97              | ALE    |                         | Address Latch Enable The level at this pin defines the bus interface mode: Fixed to "0": Demultiplexed Siemens/Intel bus interface Fixed to "1": Demultiplexed Motorola bus interface Switching: Multiplexed Siemens/Intel bus interface The address information provided on lines A0 A8 is internally latched with the falling edge of ALE. This function allows the ESCC8 to be directly connected to a multiplexed address/data bus. In this case, pins A0 A8 must be externally connected to the Data Bus pins.                                                      |

**Note:** All unused input pins have to be connected to a defined level

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|--------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

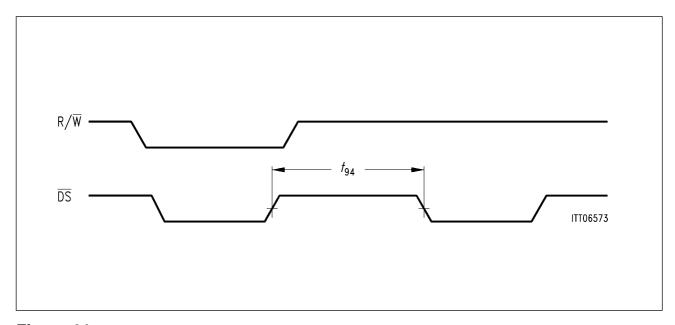

| 95      | RD/DS  |                         | Read Enable (Siemens/Intel bus mode) This signal indicates a read operation. When the ESCC8 is selected via CS the RD signal enables the bus drivers to output data from an internal register addressed via A0 A8 on to Data Bus. For more information about control/status register and FIFO access in the different bus interface modes refer to chapter 2.  If DMA transfer is selected via DACKx, the RD signal enables the bus drivers to put data from the corresponding Receive FIFO on the Data Bus. Inputs A1 A8 are ignored. A0 and BHE/BLE are used to select byte or word access.  Data Strobe (Motorola bus mode) This pin serves as input to control read/write operations. |

| 96      | WR/R/W |                         | Write Enable (Siemens/Intel bus mode) This signal indicates a write operation. When CS is active the ESCC8 loads an internal register with data provided via the Data Bus. For more information about control/status register and FIFO access in the different bus interface modes refer to chapter 2.  If DMA transfer is selected via DACKx the WR signal enables latching data from the Data Bus on the top of the corresponding Transmit FIFO. Inputs A0 A8 are ignored.  Read/Write Enable (Motorola bus mode) This signal distinguishes between read and write operation.                                                                                                           |

| 94      | CS     | I                       | Chip Select A low signal selects the ESCC8 for read/write operations. CS has no function in interrupt acknowledge or DMA cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Pin No. | Symbol  | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|---------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 81      | RES     |                         | Reset A high signal on this pin forces the ESCC8 into reset state. During Reset the ESCC8 is in power up mode, after Reset in power down mode. Reactivation of each channel is done via bit CCR0.PU (refer to chapter 3.2).  During Reset  - all uni-directional output stages are in high-impedance state,  - all bi-directional output stages (data bus) are in high-impedance state if signals RD and INTA are "high",  - "output" XTAL2 is in high-impedance if input XTAL1 is "high" (the internal oscillator is disabled during reset)                                                                                 |

| 93      | BHE/BLE |                         | Bus High Enable (Siemens/Intel bus mode) If 16-bit bus interface mode is enabled, this signal indicates a data transfer on the upper byte of the data bus (D8 D15). In 8-bit bus interface mode this signal has no function and should be tied to $V_{\rm DD}$ . Refer to chapter 2.2.1 for detailed information. Bus Low Enable (Motorola bus mode) If 16-bit bus interface mode is enabled, this signal indicates a data transfer on the lower byte of the data bus (D0 D7). In 8-bit bus interface mode this signal has no function and should be tied to $V_{\rm DD}$ . Refer to chapter 2.2.1 for detailed information. |

| 82      | WIDTH   | I                       | Width Of Bus Interface (Bus Interface Mode) A low signal on this input selects the 8-bit bus interface mode. A high signal on this input selects the 16-bit bus interface mode. In this case word transfer to/from the internal registers is enabled. Byte transfers are implemented by using A0 and BHE/BLE.                                                                                                                                                                                                                                                                                                                |

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|--------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 105     | DTACK  | oD                      | Data Transfer Acknowledge  During a bus cycle (read/write, asynchronous bus), this signal indicates that ESCC8 is ready for data transfer. The signal remains active until the data strobe (DS, RD or WR) and/or the Chip Select signal (CS) or the Interrupt Acknowledge (INTA) go inactive. An external resistor has to be tied to VDD if this function is used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

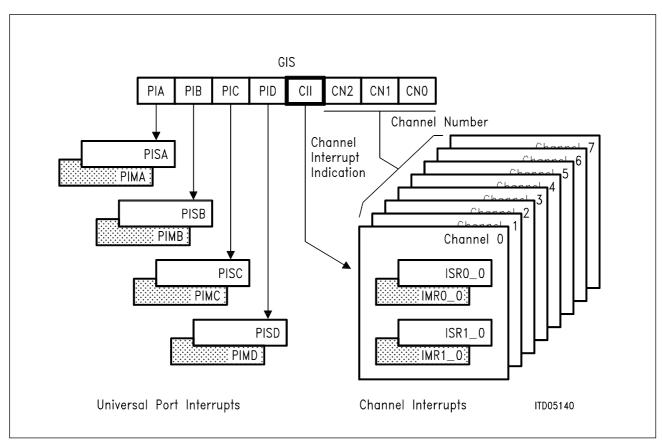

| 104     | INT    | O/oD                    | Interrupt Request INT serves as general interrupt request which may include all serial mode specific interrupt sources and the requests of the four universal ports if programmed. These interrupt sources can be masked via registers IMR0/1 (for each channel) and PIMA,B,C,D (universal ports).  Interrupt status is reported via registers GIS (Global Interrupt Status), ISR0/1 (for each channel) and PISA,B,C,D (universal ports).  Output characteristics (push-pull active low/high, open drain) are determined by programming the IPC register.  In Daisy Chain cascading mode INT signal generation is only enabled if the Interrupt Enable input IE1 is active "high".  INT is reset if  -interrupts are disabled in Daisy Chain cascading mode (pin IE1 = low),  -no further interrupt is pending,  i.e. all interrupt status bits are reset. |

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|--------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

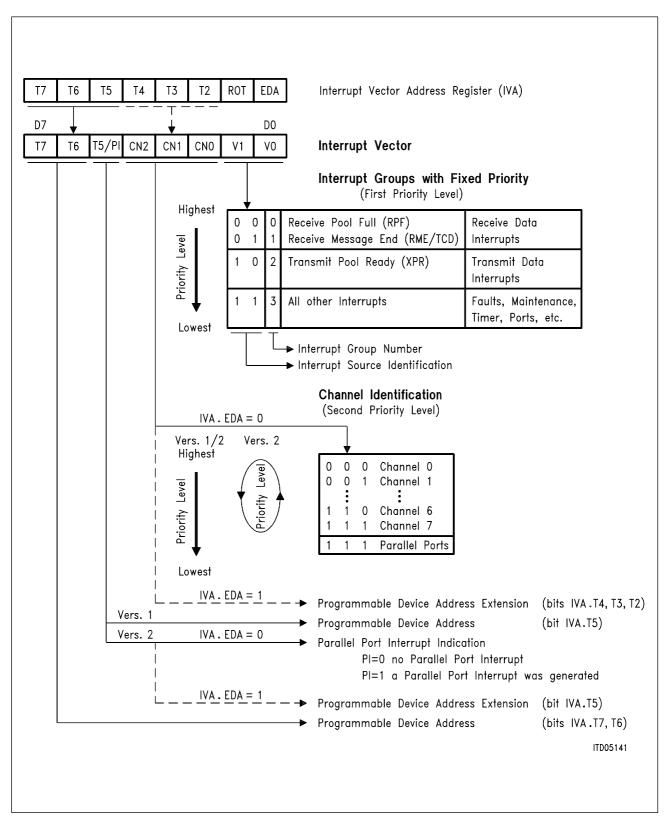

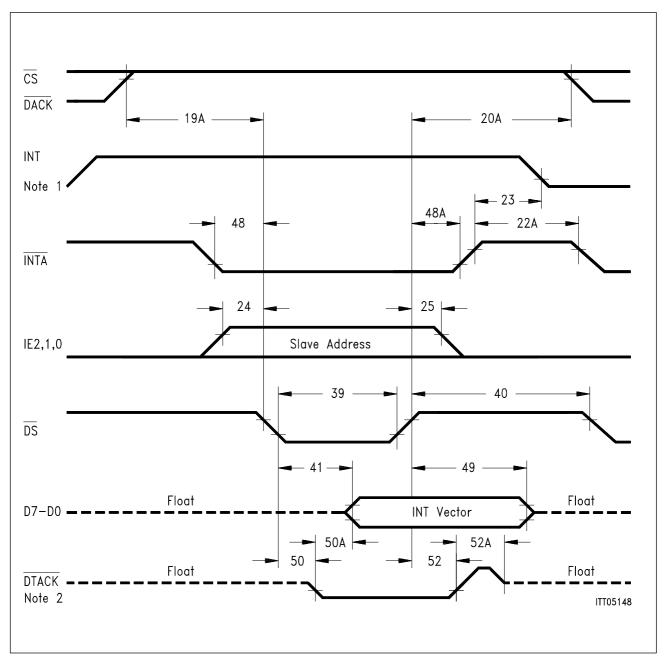

| 98      | INTA   |                         | Interrupt Acknowledge  If the interrupt is acknowledged via pin INTA, an interrupt vector is output on D0D7. All interrupt sources are organized in groups with fixed priority. The priority of the channels within a group is fixed or adjusted dynamically (rotating priority scheme, version 2 upward) (refer to chapter 2). The generated interrupt vector refers to the interrupt group and the requesting channel with currently highest priority (although more than one interrupt source/group may be active). Reaction on INTA signal depends on the bus interface mode and the cascading mode in conjunction with the Interrupt Enable pins IE0-2 (ref. to IPC register):  Motorola bus mode:  INT is reset with the rising edge of the following valid INTA cycle if no further interrupt is pending. The interrupt vector is output with signal DS.  Siemens/Intel bus mode:  INT is reset with the rising edge of the second valid INTA cycle (2-cycle '86 mode) if no further interrupt is pending.  Slave mode:  Interrupt acknowledge is accepted if an interrupt signal has been generated and the slave address provided via IE0-2 corresponds to the programmed value (IPC register).  Daisy Chaining mode:  Interrupt acknowledge is accepted if an interrupt signal has been generated and Interrupt Enable input IE1 is active during the following INTA cycle.  Note: Pins CS, DACKx have to be inactive during an INTA cycle. If pin INTA is not used, it has to be tied to VDD. |

| Pin No.    | Symbol      | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|-------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

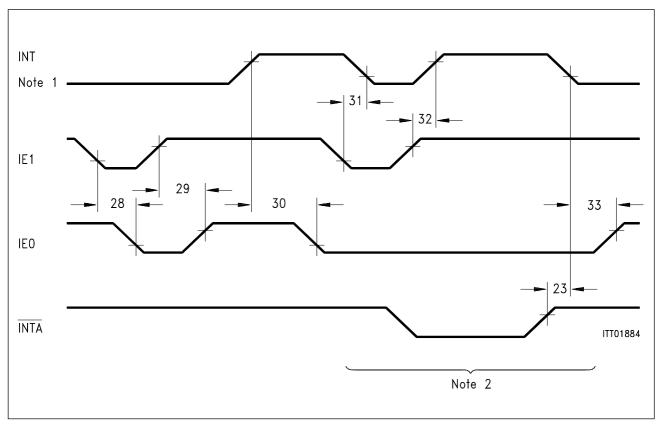

| 101 100 99 | IE0 IE1 IE2 |                         | Interrupt Enable 0, 1, 2  The function depends on the selected cascading mode:  Slave mode: IE0-2 are inputs. Interrupt acknowledge is accepted if an interrupt signal has been generated and the slave address provided via IE0, IE1, IE2 corresponds to the programmed value (IPC register). If not used, IE0-2 should be tied to GND and the slave address should be set to "0" (e.g. single device application).  Daisy Chaining mode: IE0 is output, IE1 is input. IE2 is unused and has to be fixed to "0" or "1". Normally, IE1 is connected to the IE0 pin of devices with higher priority. If not used, IE1 has to be fixed to "1".  If IE1 is reset ("0")  - the IE0 output is reset immediately, - an active INT signal will be prohibited or aborted.  - INT is hold inactive unconditionally as long as IE1 is "0".  As long as INTA input is inactive, IE1 = "1" enables INT signal generation. If INT goes active, pin IE0 immediately is set to "0". Interrupt acknowledge is accepted if the Interrupt Enable input IE1 is active during the following INTA cycle. During this cycle, and additionally till the end of the second INTA cycle in Siemens/Intel bus mode, triggering of INT signal generation is prohibited, i.e. no interrupt will be generated while (another) device is under service. This is valid even for devices with higher priority.  Pin IE0 returns to active state (logical "1") when INT is deactivated and IE1 input is high. |

| Pin No.                                              | Symbol                                                       | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------|--------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

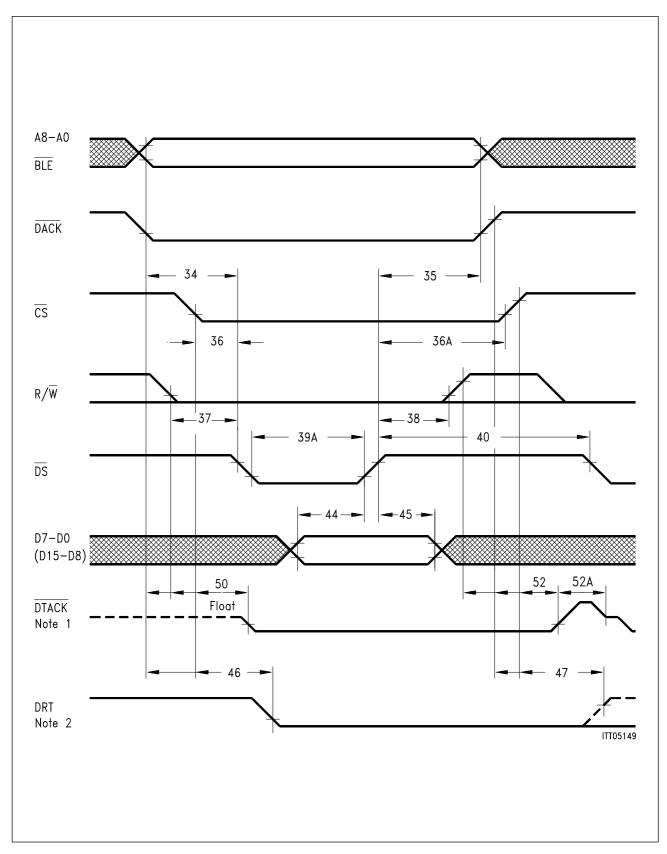

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8                 | DRT0<br>DRT1<br>DRT2<br>DRT3<br>DRT4<br>DRT5<br>DRT6<br>DRT7 | O                       | DMA Request Transmitter (Channel 0 7) The transmitter on a serial channel requests a DMA transfer by activating the corresponding DRT line. The request remains active as long as the corresponding Transmit FIFO requires data transfers. The amount of data bytes to be transferred from the system memory to the ESCC8 serial channel (= byte count) must be written first to the XBCH, XBCL registers. Always blocks of data (n x 32 bytes + REST, n = 0, 1,) are transferred till the Byte Count is reached. DRTn is deactivated with the beginning of the last write cycle. |

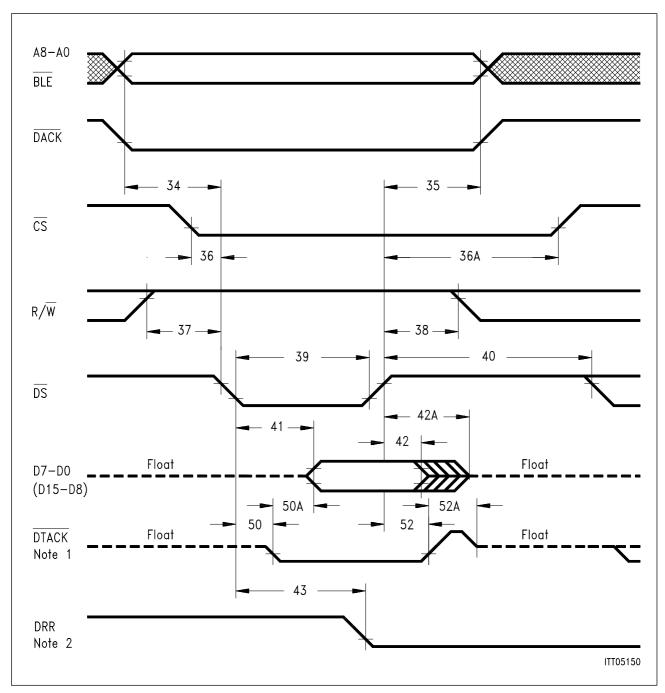

| 160<br>159<br>158<br>157<br>156<br>155<br>154<br>153 | DRR0<br>DRR1<br>DRR2<br>DRR3<br>DRR4<br>DRR5<br>DRR6<br>DRR7 | 0                       | DMA Request Receiver (Channel 0 7) The receiver on a serial channel requests a DMA transfer by activating the corresponding DRT line. The request remains active as long as the corresponding Receive FIFO requires data transfers, thus always blocks of data are transferred. DRRn is deactivated immediately following the falling edge of the last read cycle.                                                                                                                                                                                                                |

| Pin No.                                          | Symbol                                                                       | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|--------------------------------------------------|------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

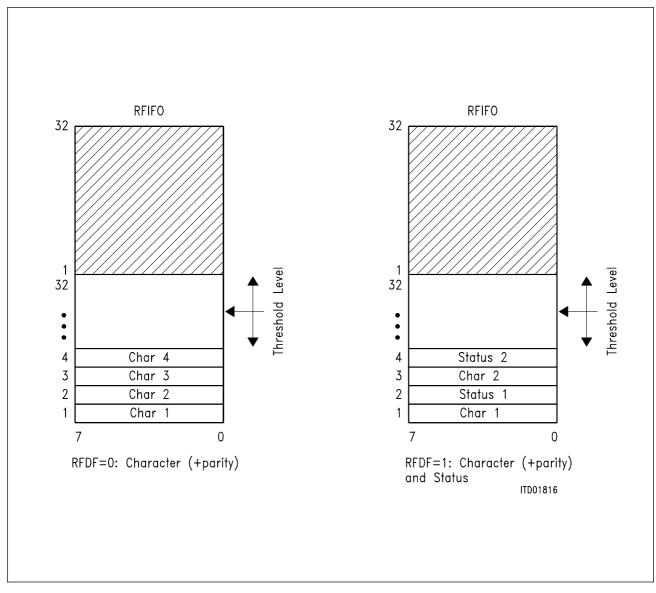

| 73<br>74<br>75<br>76<br>77<br>78<br>79<br>80     | DACKO DACK1 DACK2 DACK3 DACK4 DACK5 DACK5 DACK6 DACK7                        |                         | <b>DMA Acknowledge</b> (Channel 0 7) A low signal on these pins informs the ESCC8 that the requested DMA cycle controlled via DRT or DRR of the corresponding channel is in progress, i.e. the DMA controller has achieved bus mastership from the CPU and will start data transfer cycles (either write or read). In conjunction with a read or write operation these inputs serve as Access Enable (similar to $\overline{\text{CS}}$ ) to the respective FIFOs. If $\overline{\text{DACK}}$ is active, the input to pins A1A8 is ignored and the FIFOs are implicitly selected. A0 and $\overline{\text{BHE/BLE}}$ are used to select byte or word access. If not used, these pins must be connected to $V_{\text{DD}}$ . |  |

| 14<br>16<br>20<br>22<br>112<br>110<br>108<br>106 | RXD0<br>RXD1<br>RXD2<br>RXD3<br>RXD4<br>RXD5<br>RXD6<br>RXD7                 | I<br>(O/oD)             | Receive Data (Channel 0 7) Serial data is received on these pins. May be switched to T×D function via bit CCR2.SOC1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 49<br>50<br>51<br>52<br>69<br>70<br>71           | RXCLK0<br>RXCLK1<br>RXCLK2<br>RXCLK3<br>RXCLK4<br>RXCLK5<br>RXCLK5<br>RXCLK6 | I                       | Receive Clock (Channel 0 7) The function of these pins depends on the selected clock mode. In each channel, R×CLKn may supply either  - the receive clock (clock mode 0), or  - the receive and transmit clock (clock mode 1, 5), or  - the clock input for the baud rate generator (clock mode 2, 3).                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Pin No.                                              | Symbol                                                                                               | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 41<br>42<br>43<br>44<br>45<br>46<br>47<br>48         | RTS0<br>RTS1<br>RTS2<br>RTS3<br>RTS4<br>RTS5<br>RTS6<br>RTS7                                         | 0                       | Request to Send (Channel 0 7) When the RTS bit in the MODE register is set, the RTS signal goes low. When the RTS bit is reset, the signal goes high if the transmitter has finished and there is no further request for a transmission. In bus configuration, RTS can be programmed via CCR2 to:  — go low during the actual transmission of a frame shifted by one clock period, excluding collision bits.  — go low during reception of a data frame.  — stay always high (RTS disabled).                                                                               |  |

| 134<br>133<br>132<br>131<br>130<br>129<br>128<br>127 | CTS0/CxD0<br>CTS1/CxD1<br>CTS2/CxD2<br>CTS3/CxD3<br>CTS4/CxD4<br>CTS5/CxD5<br>CTS6/CxD6<br>CTS7/CxD7 | 1                       | Clear to Send (Channel 0 7) A low on the CTSn input enables the respective transmitter. Additionally, an interrupt may be issued if a state transition occurs at the CTSn pin (programmable feature).  If no "Clear To Send" function is required, the CTSn inputs can be directly connected to GND.  Collision Data (Channel 0 7) In a bus configuration, the external serial bus must be connected to the corresponding C×D pin for collision detection.                                                                                                                 |  |

| 126<br>125<br>124<br>123<br>122<br>121<br>120<br>119 | CD0<br>CD1<br>CD2<br>CD3<br>CD4<br>CD5<br>CD6<br>CD7                                                 |                         | <ul> <li>Carrier Detect (Channel 0 7)</li> <li>The function of this pin depends on the select clock mode. It can supply: <ul> <li>either a modem control or a general purpose input (clock modes 0,2,3,4,6,7). If auto-star programmed, it functions as a receiver enal signal.</li> <li>or a receive strobe signal (clockmode 1).</li> <li>or a frame synchronization signal in time-sl oriented operation mode (clock mode 5).</li> </ul> </li> <li>Additionally, an interrupt may be issued if a stat transition occurs at the CDn pin (programmab feature).</li> </ul> |  |

| Pin No.                                          | Symbol                                                       | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                          |  |

|--------------------------------------------------|--------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 13<br>15<br>19<br>21<br>113<br>111<br>109<br>107 | TXD0<br>TXD1<br>TXD2<br>TXD3<br>TXD4<br>TXD5<br>TXD6<br>TXD7 | O/oD                    | Transmit Data (Channel 0 7) Transmit data is shifted out via these pins. They can be programmed to be either a push-pull or open drain output to support bus configurations.  Note: Pin TxD is "or" ed with pin RTS if NRZI encoding and IDLE as Interframe Time Fill are selected and bit MODE.RTS is reset.  May be switched to RxD function via bit CCR2.SOC1. |  |

| 9<br>10<br>11<br>12<br>118<br>117<br>116<br>115  | TXCLK0 TXCLK1 TXCLK2 TXCLK3 TXCLK4 TXCLK5 TXCLK6 TXCLK7      | I/O                     |                                                                                                                                                                                                                                                                                                                                                                   |  |

| Pin No.                                                                                                               | Symbol                           | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|-----------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 63<br>64                                                                                                              | XTAL1<br>XTAL2                   | (O)                     | Crystal Connection  If the internal oscillator is used for clock generation the external crystal has to be connected to these pins. Moreover, XTAL1 may be used as common clock input for all channels provided by an external clock generator.  All versions: common use for both channels in clock modes 4,6,7.  Version 2 upward: additionally used in clock mode 0b and for master clock applications.                                                                                                                                                                                                                                                     |  |

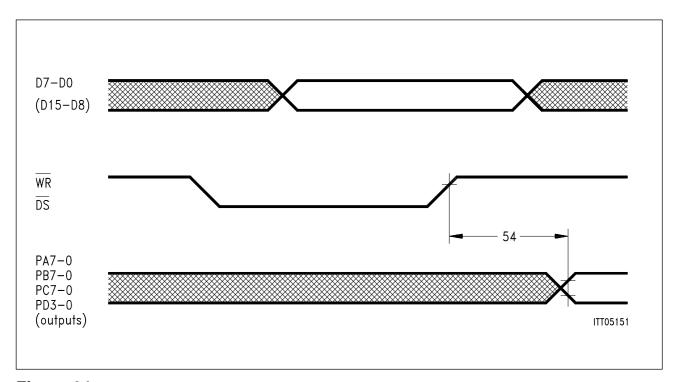

| $ \begin{array}{c} 152 \rightarrow 145 \\ 53 \rightarrow 60 \\ 142 \rightarrow 135 \\ 65 \rightarrow 68 \end{array} $ | PA0 7<br>PB0 7<br>PC0 7<br>PD0 3 | I/O                     | <ul> <li>Parallel Port (Port A,B,C,D)</li> <li>Four general purpose bi-directional parallel ports (port A,B,C: 8 bit; port D: 4 bit). Every pin is individually programmable to operate as an output or an input (Port Configuration Register PCRA,B,C,D).</li> <li>If defined as output, the state of the pin is directly controlled via the microprocessor interface(PortValueRegister PVRA,B,C,D)</li> <li>If defined as input, its state can be read via PVRA,B,C,D. All changes may be indicated via an interrupt status (Port Interrupt Mask register PIMA,B,C,D, Port Interrupt Status register PISA,B,C,D, interrupt is output on pin INT).</li> </ul> |  |

| 18, 32, 61,<br>102, 114,<br>143                                                                                       | $V_{SS}$                         | I                       | Ground (0 V) For correct operation, all six pins have to be connected to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 17, 31, 62,<br>103, 144                                                                                               | $V_{DD}$                         | I                       | Positive Power Supply (5 V) For correct operation, all five pins have to be connected to positive power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 83                                                                                                                    | TEST                             | I                       | Test Input This pin always has to be connected to $V_{\rm SS}$ . (Test input for the manufacturer)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

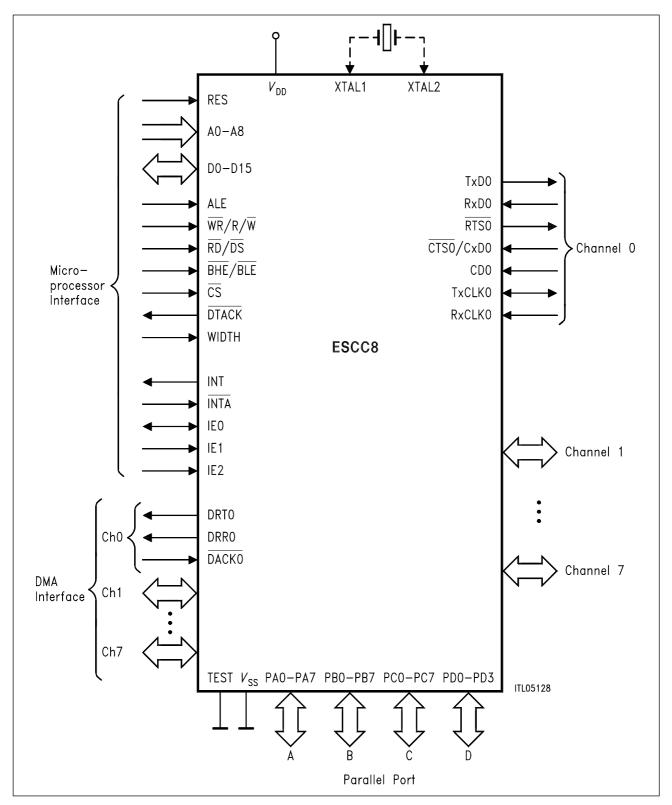

### 1.2 Logic Symbol

Figure 1 ESCC8 Logic Symbol

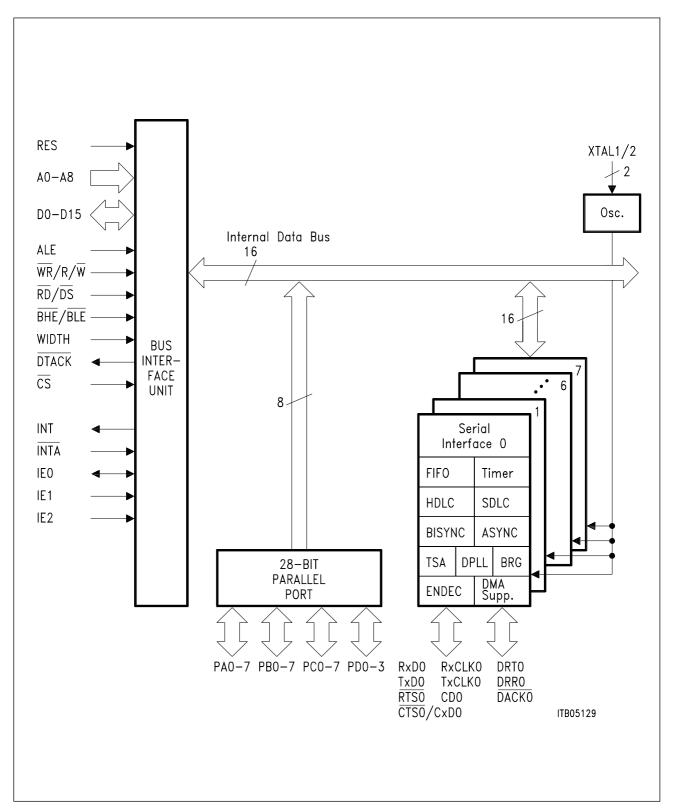

### 1.3 Functional Block Diagram

Figure 2 Functional Block Diagram SAB 82538

The ESCC8 (SAB 82538) comprises eight completely independent full-duplex serial interfaces which support HDLC/SDLC, BISYNC and ASYNC protocols. Layer-1 functions are performed by means of internal oscillator, Baud Rate Generator (BRG), Digital Phase Locked Loop (DPLL), and Time-Slot Assignment circuits (TSA, only available for version SAB 82538H-10). Encoding / decoding of serial data can be done by using NRZ, NRZI, FM0, FM1, and Manchester encoding schemes.

An 28-bit universal port is provided which can be used for additional modem control lines or for general I/O purposes.

Associated with each serial channel is a set of independent command and status registers and 64-byte deep FIFOs for transmit and receive direction. Access is done via the flexible 8/16-bit microprocessor interface. DMA capability has been added to the ESCC8 by means of a 16-channel DMA interface with one DMA request line for each transmitter and receiver of both channels. The interrupt structure of ESCC8 supports interrupt driven systems using interrupt polling, daisy chaining or interrupt vector control.

### 1.4 System Integration

### 1.4.1 General Aspects

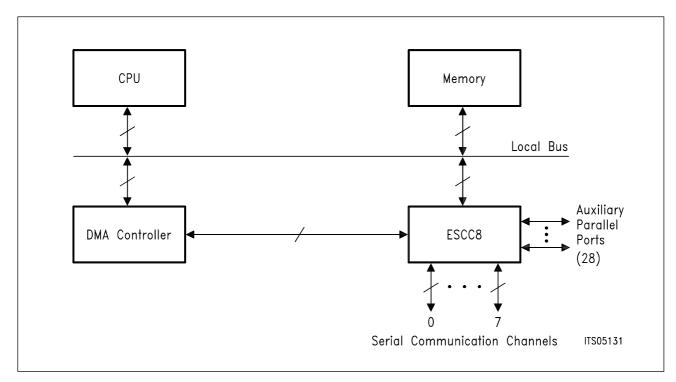

Figure 3

General System Integration of ESCC8

Figure 3 gives a general overview of system integration of ESCC8.

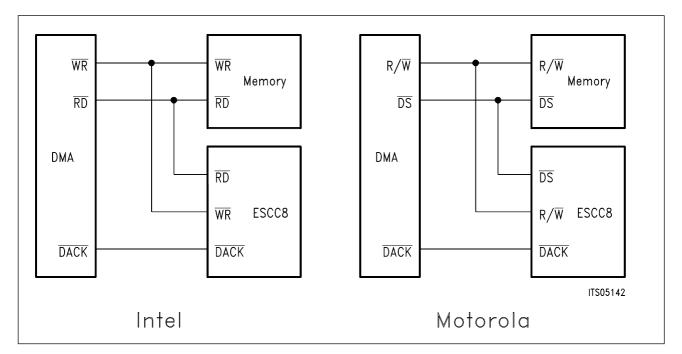

The ESCC8's bus interface consists of an 8/16-bit bidirectional Data bus (D0-D15), nine Address Line inputs (A0-A8), three control inputs (RD / DS, WR / R/W, CS), five signals for interrupt support (INT, INTA, IE0-2) and a 16-channel DMA interface. Mode input pins (strapping options) allow the bus interface to be configured for 8/16-bit bus width and for either Siemens/Intel or Motorola environment.

Generally, there are two types of transfers occurring via the system bus:

- Command/Status transfers, which are always controlled by the CPU. The CPU sets the operation mode (Initialization), controls function sequences and gets status information by writing or reading the ESCC8's registers (via CS, WR or RD, and register address via A0-A8, BHE).

- Data Transfers, which are effectively performed by DMA without CPU interaction using the ESCC8's DMA interface (DMA Mode). Optionally, interrupt controlled data transfer can be done by the CPU (Interrupt Mode).

#### 1.4.2 Environment

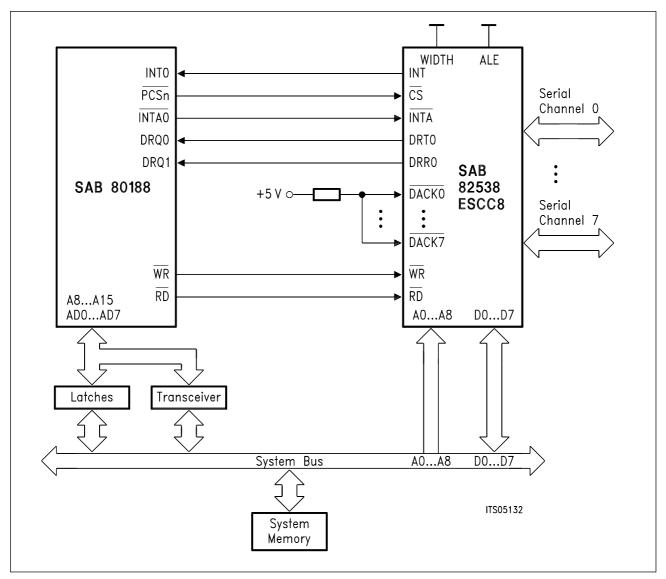

### 1.4.2.1 ESCC8 with SAB 80188 Microprocessor

A system with minimized additional hardware expense can be build up with a SAB 80188 microprocessor as shown in **figure 4**.

Figure 4

ESCC8 with SAB 80188 CPU

The ESCC8 is connected to the demultiplexed system bus. Data transfer for one serial channel can be done by the 2-channel on-chip DMA controller of the 80188, the other channels are serviced by interrupt. Since the 80188 does not provide DMA Acknowledge outputs, data transfer from/to ESCC8 is controlled via CS, RD or WR Address information (A1 ... A8) and the DACK0-7 inputs are not used. A0 and BHE/BLE are used to select byte or word access.

This solution supports applications with a high speed data rate in one serial channel with minimum hardware expense making use of the on-chip peripheral functions of the 80188 (chip select logic, interrupt controller, DMA controller).

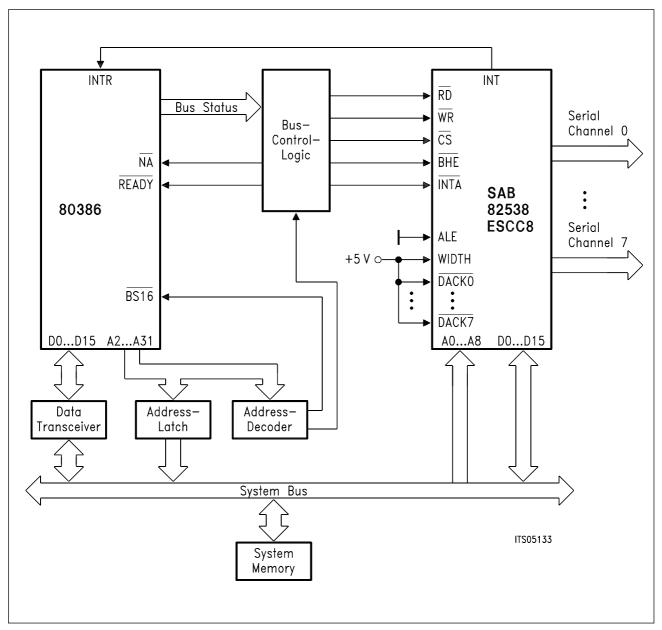

#### 1.4.2.2 ESCC8 with 80386

In high-performance 32-bit systems based on an 80386 microprocessor a separate control logic (e.g. sequencer PALs) is normally provided to generate all necessary control signals for interfacing to I/O devices. Address and data lines are buffered via latches or transceivers. An interface to ESCC8 is for this case sketched in **figure 5**.

Figure 5 ESCC8 with 80386  $\mu$ P

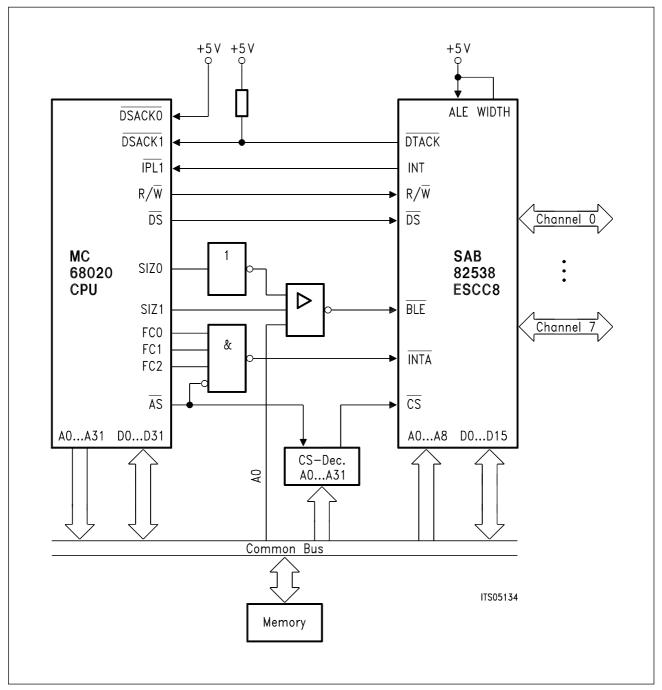

### 1.4.2.3 ESCC8 with MC 68020, 68030

**Figure 6** gives an example of interfacing the ESCC8 to a 32-bit Motorola microprocessor. Some glue logic is necessary. The signal BUS LOW ENABLE (BLE) has to be decoded out of transfer size information (SIZ0,1) and A0. The ESCC8 interface logic has to respond as a 16-bit peripheral (DSACK1,0 =  $01_H$ ) during register access and interrupt acknowledge cycles.

Figure 6 ESCC8 with 68020  $\mu\text{P}$

### 1.4.2.4 Interrupt Cascading

The ESCC8 supports two cascading schemes which can be selected by programming the IPC register:

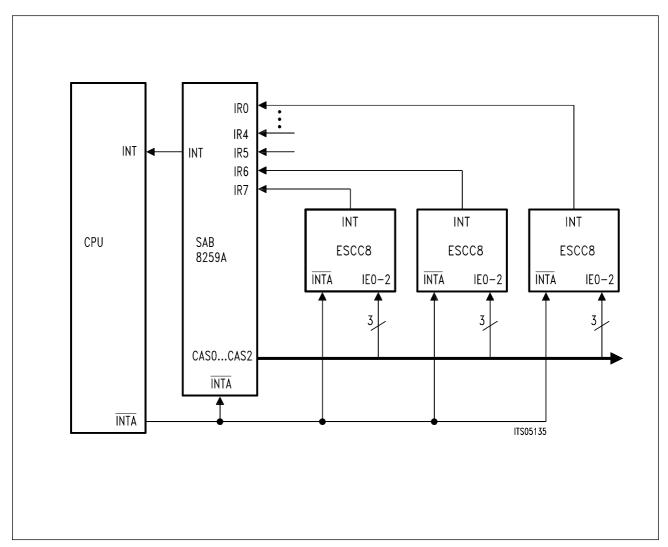

#### **Slave Mode**

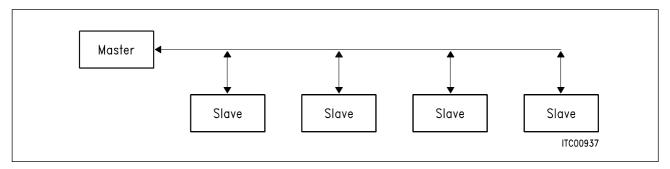

Interrupt outputs of several devices (slaves) are connected to a priority resolving unit (e.g. interrupt controller). The slave which is selected for the interrupt service routine is addressed via special address lines during the interrupt acknowledge cycle. For this application the ESCC8 offers three Interrupt Enable inputs (IE0, IE1,IE2) and a programmable 3-bit slave ID.

Figure 7

Interrupt Cascading (Slave Mode) in Intel Bus Mode

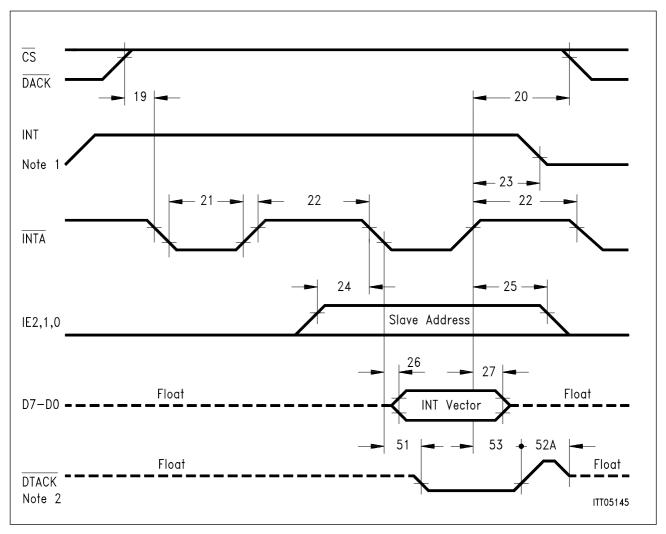

For Intel type microprocessor systems the 2-cycle interrupt acknowledge scheme is supported ('86 mode).

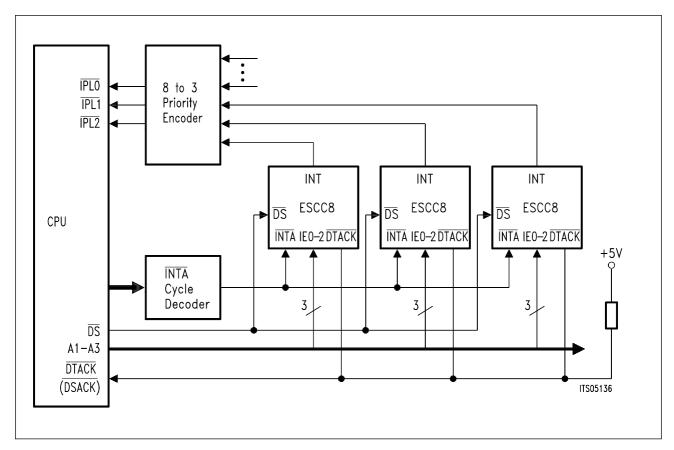

Figure 8 Interrupt Cascading (Slave Mode) in Motorola Bus Mode

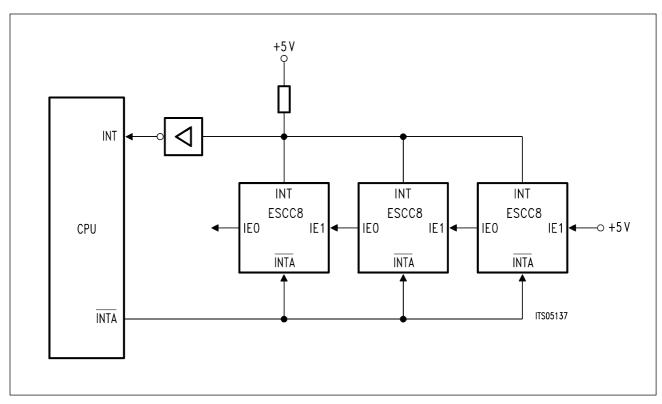

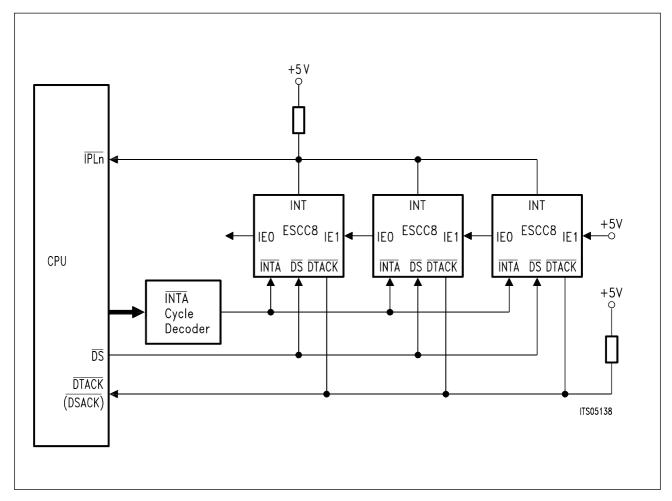

### **Daisy Chaining**

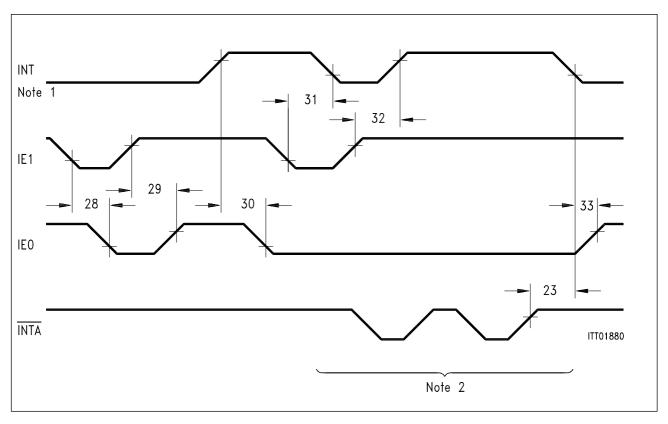

If selected via IPC register the Interrupt Enable pins IE0, IE1 are used for building a Daisy Chain by connecting the Interrupt Enable Output (IE0) of the higher priority device to the Interrupt Enable Input (IE1) of the lower priority device. The highest priority device has IE1 pulled high (**refer to figure 9 and 10**). IE2 is unused and has to be fixed to "0" or "1".

Figure 9

Interrupt Cascading (Daisy Chaining) in Intel Bus Mode

For Intel type microprocessor systems the 2-cycle interrupt acknowledge scheme is supported ('86 mode). Maximum available settling time for the chain: from the beginning of the first INTA cycle to the beginning of the second.

Figure 10

Interrupt Cascading (Daisy Chaining) in Motorola Bus Mode

For Motorola type microprocessor systems the maximum available settling time for the chain is much shorter: from the beginning of the INTA cycle to the falling edge of signal DS.

### **2** Functional Description

#### 2.1 General

The ESCC8 distinguishes itself from other communication controllers by its advanced characteristics. The most important are:

- Eight independent serial channels.

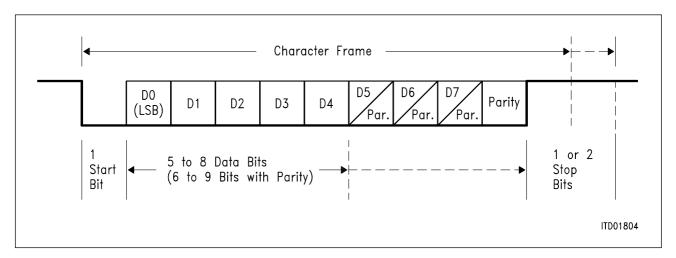

- Support of HDLC, SDLC, BISYNC/MONOSYNC and Asynchronous protocols.

- Support of layer-2 functions (HDLC mode).

In addition to those bit-oriented functions commonly supported by HDLC controllers, such as bit stuffing, CRC check, flag and address recognition, the ESCC8 provides a high degree of procedural support.

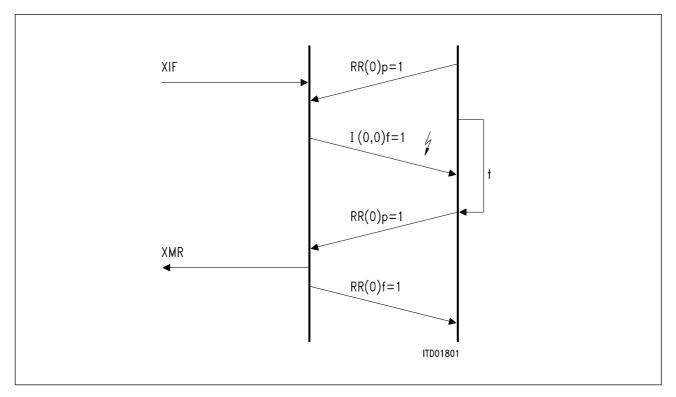

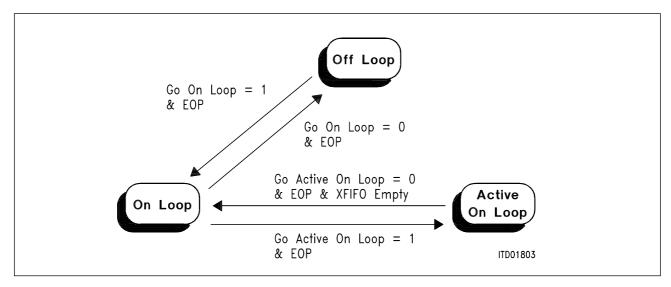

In a special operating mode (auto-mode), the ESCC8 processes the information transfer and the procedure handshaking (I- and S-frames of HDLC protocol) autonomously. The only restriction is that the window size (= number of outstanding unacknowledged frames) is limited to 1, which is sufficient for many applications. The communication procedures are mainly processed between the communication controllers and not between the attached processors. Thus the dynamic load on the CPU and the software expense is greatly reduced.

The CPU is informed about the status of the procedure and has mainly to manage the receive and transmit data. In order to maintain cost effectiveness and flexibility, the handling of unnumbered (U) frames, and special functions such as error recovery in case of protocol errors, are not implemented in hardware and must be done by the user's software.

Extended support of different link configurations.

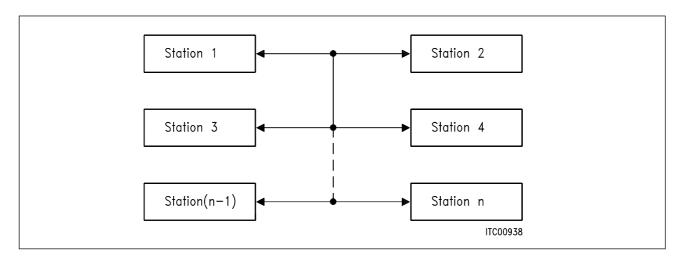

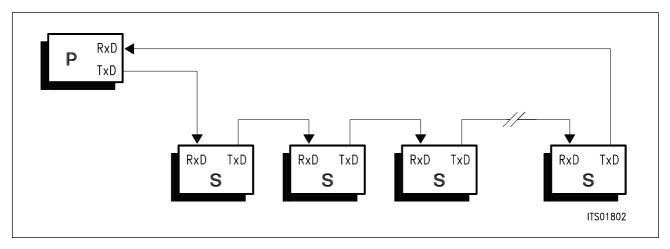

Besides the point-to-point configurations, the ESCC8 allows the implementation of point-to-multipoint or multi-master configurations without additional hardware or software expense.

In point-to-multipoint configurations, the ESCC8 can be used as a master or as a slave station. Even when working as slave station, the ESCC8 can initiate the transmission of data at any time. An internal function block provides means of idle and collision detection and collision resolution, which are necessary if several stations start transmitting simultaneously. Thus, a multi-master configuration is also possible.

Telecom specific features.

In a special operating mode, the ESCC8 can transmit or receive data packets in one of up to 64 time-slots of programmable width (clock mode 5). Furthermore, the ESCC8 can transmit or receive variable data portions within a defined window of one or more clock cycles in conjunction with an external strobe signal (clock mode 1). These features make the ESCC8 suitable for applications using time division multiplex methods, such as time-slot oriented PCM systems or systems designed for packet switching.

- FIFO buffers for efficient transfer of data packets.

- A further speciality of ESCC8 are the 64-byte deep FIFO buffers used for the temporary storage of data packets transferred between the serial communications interface and the parallel system bus. Because of the overlapping input/output operation (dual-port behaviour), the maximum message length is not limited by the size of the buffer. The dynamic load of the CPU is drastically reduced by transferring the data packets block by block via Direct Memory Access supported by the ESCC8. The CPU only has to initiate the data transmission by the ESCC8 and determine the status in case of completed reception, but is not involved in data transfers.

- The 16-bit wide microprocessor interface enables high data throughput and offers a high flexibility for connection to both 8/16-bit Siemens/Intel and Motorola type microprocessor systems. Moreover, interrupt driven systems are supported by vectored interrupts and interrupt cascading capabilities.

- In addition to standard modem control lines associated with each of the serial channels, 28 universal ports are provided for applications related to or independent of the serial channels.

### **Link Configurations**

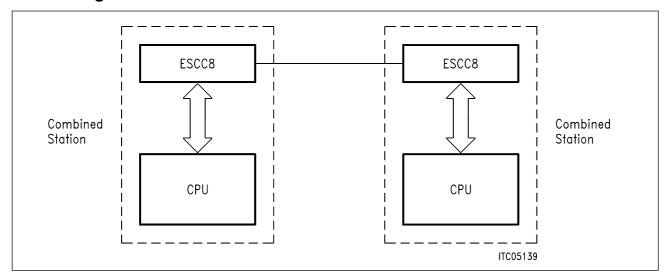

Figure 11 Point-to-Point Configuration

Figure 12 Point-to-Multipoint Configuration

Figure 13 Multimaster Configuration

### 2.2 Microprocessor Interface

### 2.2.1 Register Set

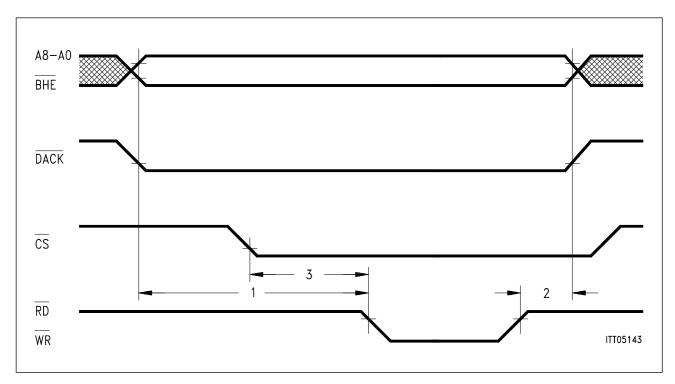

The communication between the CPU and the ESCC8 is done via a set of directly accessible registers. The interface may be configured as Siemens/Intel or Motorola type with a selectable data bus width of 8 or 16 bits.

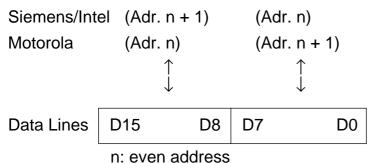

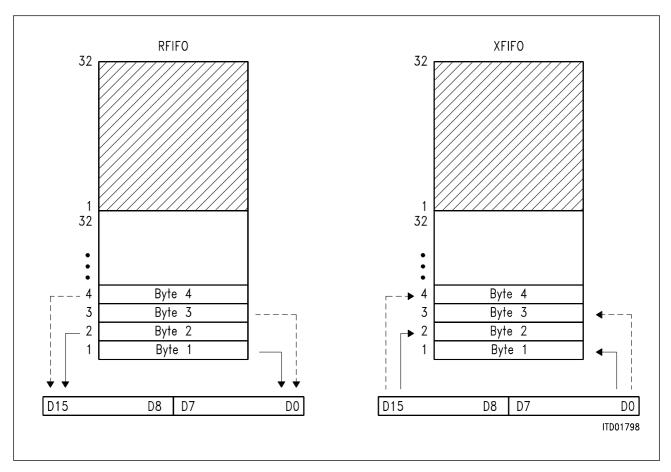

The CPU transfers data to/from the ESCC8 (via 64 byte deep FIFOs per direction and channel), sets the operating modes, controls function sequences, and gets status information by writing or reading control/status registers. All accesses can be done as byte or word accesses if enabled. If 16-bit bus width is selected, access to lower/upper part of the data bus is determined by address line A0 and signal BHE/BLE as shown in table 1 and 2.

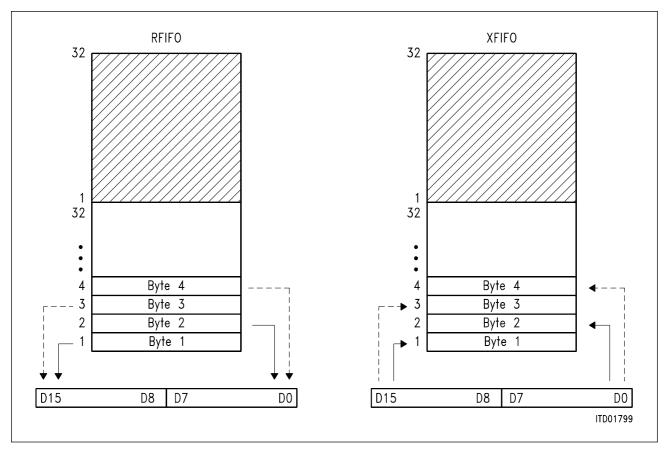

### Mixed Byte/Word Access to the FIFOs

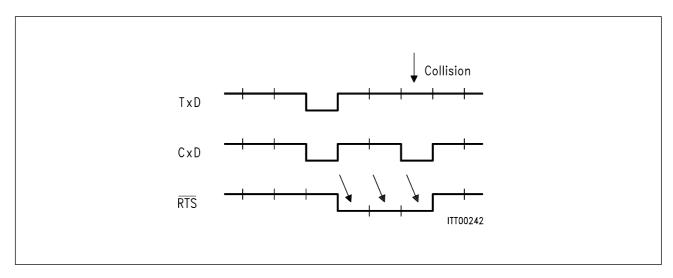

Reading from or writing to the internal FIFOs (RFIFO and XFIFO of each channel) can be done using a 8-bit (byte) or 16-bit (word) access depending on the selected bus interface mode. In version 1 of ESCC8, byte access in the case of 16-bit bus interface mode is allowed if not mixed with word accesses when reading from or writing to the same pool.