# SIEMENS

## **ISDN Burst Tranceiver Circuit (IBC)**

#### **Preliminary Data**

CMOS IC

**PEB 2095**

| Туре                     | Ordering Code                | Package                    |

|--------------------------|------------------------------|----------------------------|

| PEB 2095-C<br>PEB 2095-N | Q67100-H8398<br>Q67100-H8396 | C-DIP-24<br>PL-CC-28 (SMD) |

| PEB 2095-P               | Q67100-H8397                 | P-DIP-24                   |

The PEB 2095 ISDN Burst Transceiver Circuit (IBC) is a half duplex transceiver for the 2-wire transmission line (CCITT U-reference point). Full duplex transmission is achieved using a time compression multiplex (ping-pong) technique. Furthermore, the device links the 2-wire transmission line to the ISDN Oriented Modular (IOM) interface and hence to the powerful Siemens ISDN device family. From the point of view of the OSI communications protocol model, the device manages layer-1 of the interface protocol and can communicate with other layer-1 or layer-2 devices over the IOM interface.

A second device, the PEB 2090 ISDN Echo Cancellation Circuit (IEC), may also be used at the U-reference point. The device chosen depends on the application. The IBC proves more cost-effective for shorter range transmission applications (2 – 3.5 km), especially PBX.

The IBC is available as a 24-pin CMOS device.

The device operates from a single 5-V power supply.

The maximum power consumption is 80 mW.

#### Features:

- Half duplex burst mode 2-wire U-interface transceiver

- Mode configurable to function at both ends of the line

- 144 kbit/s user bit rate (2B + D)

- 384-kHz line clock rate

- IOM compatible

- Clock and frame recovery

- Adaptive line equalization and amplification at receiver

- Implementation of activation/deactivation procedures

- Built-in wake-up function for activation from power down state

- Switching of test loops

- Typical length of loop: up to 3.5 km with 0.6 mm diameter wire

- Advanced CMOS technology

- Low power consumption: 6 mW power down

80 mW power up (maximum)

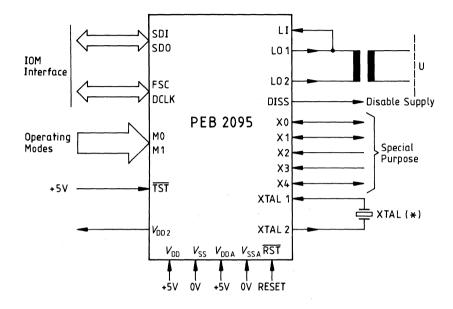

## Logic Symbol

\*) An external oscillator can also be used as a clock input to XTAL1. In this configuration XTAL2 is not connected.

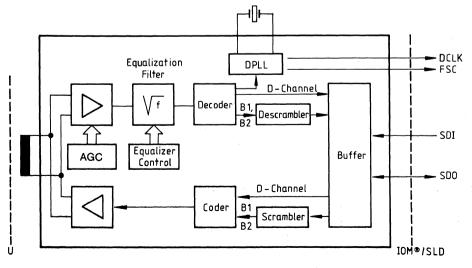

#### **Block Diagram**

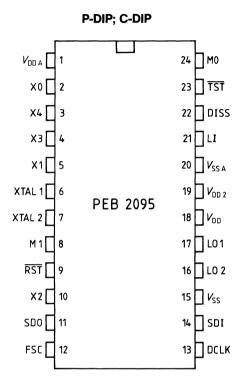

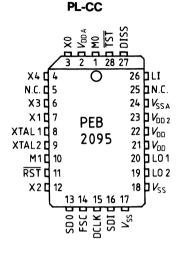

## **Pin Configurations**

#### (top view)

\*) XTAL2 not connected when external oscillator is used

## Pin Definitions and Functions

| Pin No.<br>P-DIP       | Pin No.<br>PL-CC            | Symbol                                                                     | Input (I)<br>Output (O)         | Function                                                                                                 |                                                                 |

|------------------------|-----------------------------|----------------------------------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| 16<br>17<br>21         | 20<br>19<br>26              | L01<br>L02<br>LI                                                           | 0<br>I                          | Line transmitter; o<br>Line transmitter; o<br>Line receiver                                              |                                                                 |

| 11<br>14<br>13<br>12   | 13<br>16<br>15<br>14        | SD0<br>SDI<br>DCLK<br>FSC                                                  | 0<br> <br> /0<br> /0            | Serial data out<br>Serial data in<br>Serial data clock<br>Frame sync.                                    | IOM interface                                                   |

| 24<br>8                | 1<br>10                     | M0<br>M1                                                                   | 1                               | Operating mode se                                                                                        | etup pins                                                       |

| 2<br>5<br>10<br>4<br>3 | 3<br>7<br>12<br>6<br>4      | X0<br>X1<br>X2<br>X3<br>X4                                                 | /O<br> /O<br> <br> <br> <br> /O | Multifunctional pin                                                                                      | s; mode specific functions                                      |

| 6<br>7                 | 8<br>9                      | XTAL1<br>XTAL2                                                             | <br>0                           |                                                                                                          | axt∈rnal oscillator input.<br>onnection (n.c. when<br>is used). |

| 23                     | 28                          | TST                                                                        | 1                               | Device test pin; no<br>always.                                                                           | ot for general use; tie high                                    |

| 22                     | 27                          | DISS                                                                       | 0                               | Disable supply                                                                                           |                                                                 |

| 9                      | 11                          | RST                                                                        | 1                               | Hardware reset pir                                                                                       | n; active low                                                   |

| 18<br>15<br>1<br>20    | 21, 22<br>17, 18<br>2<br>24 | V <sub>DD</sub><br>V <sub>SS</sub><br>V <sub>DDA</sub><br>V <sub>SSA</sub> |                                 | Digital power supply 5 V $\pm$ 5%<br>Digital ground<br>Analog power supply 5 V $\pm$ 5%<br>Analog ground |                                                                 |

| 19                     | 23                          | V <sub>DD2</sub>                                                           | 0                               | capa                                                                                                     | ected to V <sub>SSA</sub> via 10 nF                             |

|                        | 5; 25                       | N.C.                                                                       |                                 | Not connected inte                                                                                       | ernally                                                         |

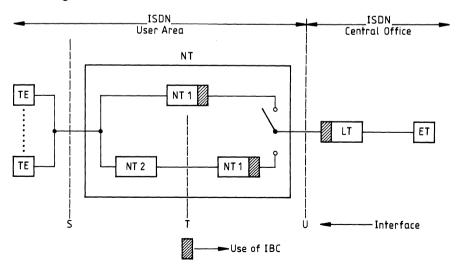

#### System Integration

There are three operating modes:

- LT: Line Termination i.e. in the Local Exchange/PBX

- TE: Terminal Equipment i.e. in the Subscriber Terminal

- NT: Network Termination

Two examples of LT mode are illustrated, one connected directly to the terminal, one connected to a network termination. In the latter case, the terminal is connected over the S interface for the network termination. Because of the multiplexing facility on the S-bus to eight terminals may be connected to one network termination and hence to one subscriber line. In the former case (without a network termination) only one terminal per subscriber line is possible. The diagram also indicates that either the IBC or the IEC may be used for 2-wire transmission. Choice is dependent upon the transmission line characteristics, but in general the IBC is the more cost-effective for shorter range transmission applications (especially PBX).

In the LT mode, the IBC managers layer-1 functions and communicates over the IOM interface with the ICC (ISDN Communication Controller) which handles most layer-2 functions. A microprocessor (handling higher layer functions) controls and communicates with the ICC. A similar configuration is required in the TE mode, employing the same division of tasks.

In the NT mode, however, the configuration is much different. In this case the network termination is acting as an NT1 (according to CCITT notation). **Figure 1** illustrates two possible NT configurations.

#### Figure 1 NT Configuration

In both cases, NT1 refers to a simple layer-1 translation between the U interface and the S/T interface. This is achieved by the simple pairing of the IBC with an IOM compatible S-bus interface circuit (e.g. the SBC PEB 2080).

In this configuration, no ICC or microprocessor is required because layer-2 and higher are passed transparently through NT1. The IOM interface acts as an intermediate interface common to both devices.

On the other hand NT2 in **figure 1** differs from NT1 in that it includes higher level OSI functions. It could, for example, be a PBX. In this case the PBX would be connected directly over the S interface (not U interface) to the subscriber terminal(s).

**Note:** Figure 1 illustrates the CCITT definition of the U reference point i.e. between a local exchange and a network termination. The direct connection of terminals to a PBX over a 2-wire loop is not considered by CCITT since it is not in the public network domain. Since the IBC can be used in both the aforementioned configurations, this document, for simplicity, will use the term U reference point for both. Furthermore the term U interface will refer only to the time division multiplexing technique for transmission over a 2-wire loop.

#### **Functional Description**

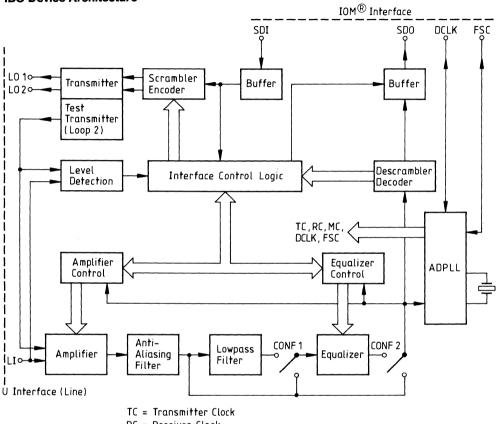

#### **IBC Device Architecture and General Functions**

The ISDN Burst Transceiver Circuit (IBC PEB 2095) performs the layer-1 functions of the time-division multiplex implementation of the U interface. This is a half duplex technique (ping-pong) involving transmission by only one device at any one time. Furthermore the IBC acts a link between the U interface to the IOM interface and hence to other layer-1 or layer-2 devices within the system. **Figure 2** depicts the device architecture.

Figure 2 IBC Device Architecture

RC = Receiver Clock

MC = Master Clock

Some of the relationships between the blocks of the device architecture and the IBC functions outlined below can be traced at this stage. This section, however, will deal in more detail with these relationships.

#### The following are the main functions of the IBC

- Activation/deactivation procedures. Activation may be initialized by either infos from the line or primitives from the IOM interface

- To increase the quality of signal received from the line, the receiver stage contains both an adaptive amplifier and equalizer

- Synchronous timing must be maintained on both sides of the device. All internal clocks are synchronized to the upstream data clock (system clock). All generated downstream clocks are synchronized, in turn, to these internal clocks.

- Testing and diagnostic functions: Testloops may be closed, test signals may be generated.

Furthermore, the IBC must also link 2 different interfaces, the IOM interface and the U interface. To do this transparently, the IBC must compensate for the following main differences between them:

- The U interface is a burst mode interface while the IOM interface is continuous

- The frame structure and data transmission techniques on both interfaces are different

- The B channels are scrambled on the U interface and unscrambled on the IOM interface

- The clock rates are different and are transmitted in a different manner. In the U interface the clock is implicit in the data stream; in the IOM interface 2 separate clocks, DCLK and FSC, must be provided.

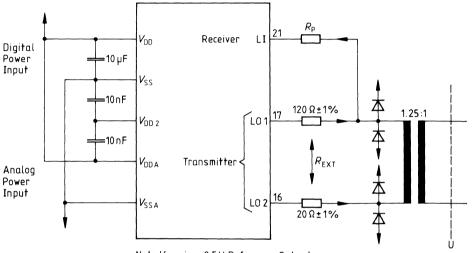

#### **Analog Functions**

**Figure 3** depicts the analog and power connections to the IBC. Both analog and digital power may be connected to a single power source. The reference voltage  $V_{DD2}$  must be linked by two 10 nF capacitors to  $V_{SS}$  and  $V_{DDA}$ . External to the transmitter and receiver a transformer (ratio 1.25:1) and external resistance ( $R_{EXT} = 140 \ \Omega \pm 1\%$ ) are connected as shown. Voltage overload protection is achieved by splitting  $R_{EXT}$  into 120  $\Omega$  and 20  $\Omega$  (for current limitation) and adding clamping diodes. If required a resistor may be added to the signal input line for current limitation.

The transmitter stage is realized as a voltage source with an internal resistance  $R_i = 15 \ \Omega \pm 40\%$ . It delivers a pulse of amplitude 2 V  $\pm 10\%$  (0-to-peak). Assuming a transformer winding resistance of the order of 1  $\Omega$ , the output resistance seen from the U interface will be 100  $\Omega$ .

Referring again to **figure 2**, the receiver input stages can be seen. They consist of a variable gain amplifier, to compensate for signal losses on the line (dynamic range 30 dB). This is followed by an anti-aliasing filter and a switched capacitor low pass filter. Finally a switched capacitor equalizer suppresses the out-of-band noise, which has passed the (anti-aliasing) filter stage, while keeping the pulse distortion low (dynamic range 15.36 dB).

## Figure 3 IBC Analog Connections

Note  $V_{DD2}$  is a 2.5 V Reference Output

Both the amplifier and the equalizer are adaptive. The amplifier has 128 possible settings and the equalizer 8 (in this sense they are digital). The adaptive logic can be stopped by externally setting the amplifier and equalizer over the IOM interface. Once set in this way, the settings remain constant. The monitor channel can also be used to program some other functions.

The level detection block monitors the receive line and informs the interface logic when an incoming signal is present. It also monitors the test transmitter to perform a similar function during test loop implementation.

#### **Digital Functions**

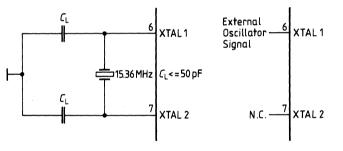

The DPLL circuitry works with an external oscillator or crystal of 15.36 MHz  $\pm$  100 ppm. This is used to synchronize all bit and frame clocks with the incoming system clock (i.e. from upstream). In the LT mode, the system clock is supplied over the IOM interface. Generation of half-bauded AMI pulses for the line is accomplished by deriving a synchronous transmitter clock using the DPLL. At the NT/TE end of the line, the data clock of 384 kHz is implicitly received in the data stream and is extracted by the IBC. From this all synchronous clocks are derived with the aid of the DPLL.

An incorporated finite state machine controls ISDN layer-1 activation/deactivation. This includes wake signal recognition in the "deactivated" state.

Due to the burst nature of U interface communication and the continuous nature of communication on the IOM interface, a buffer memory is required to compensate for timing differences.

The digital control logic also sets the adaptive coefficients on the AGC amplifier and the SC equalization filter.

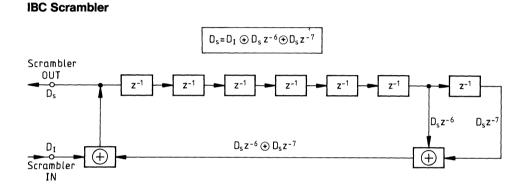

#### Scrambler/Descrambler

B channel data on the U interface is scrambled to give a flat continuous power density spectrum and to ensure enough pulses are present on the line for a reliable clock extraction to be performed at the downstream end.

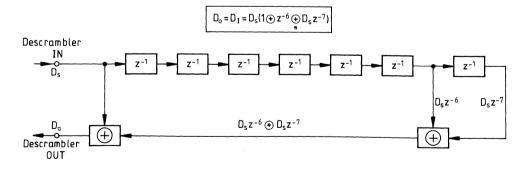

The IBC therefore, contains a scrambler and descramber, in the transmit and receive directions respectively. The basic form of these are illustrated in **figure 4** and **figure 5**.

The form is in accordance with the CCITT V.27 scramber/descrambler and contains supervisory circuitry which ensures no periodic patterns appear on the line.

#### Figure 5 IBC Descrambler

Figure 4

#### Interfaces

The IBC operates 3 interfaces:

- U interface

- IOM interface

- SLD interface

#### U Interface

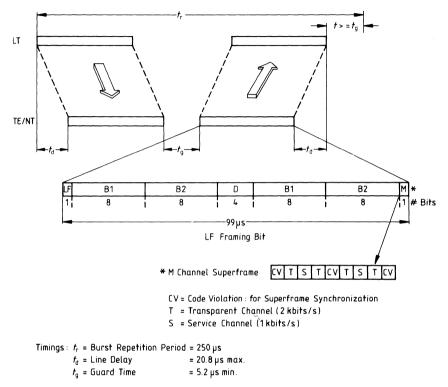

**Figure 6** demonstrates the general principles of the U interface burst mode communication technique. A frame transmitted by the exchange (LT) is received by the terminal equipment (TE) after a given propagation delay. The terminal equipment waits a minimum guard time (5.2  $\mu$ s) while the line clears. It then transmits a frame to the exchange. The exchange will begin a transmission every 250  $\mu$ s (known as the burst repetition period). However, the time between the reception of a frame from the TE and the beginning of transmission of the next frame by the LT must be greater than the minimum guard time. Communication between an LT and an NT follows the exact same procedure.

Within a burst, the data rate is 384 kbit/s and the 38-bit frame structure is as shown in **figure 4**. The framing bit (LF) is always logical "1". The frame also contains the user channels (2B+D). Note that the B channels are scrambled. It can readily be seen that in the 250  $\mu$ s burst repetition period, 4 D bits, 16 B1 bits and 16 B2 bits are transferred in each direction. This gives an effective full duplex data rate of 16 kbit/s for the D channel and 64 kbit/s for each B channel.

The final bit of the frame is called the M bit. Four successive M bits, from four successive U frames, constitute a superframe (figure 6). Three signals are carried in this superframe. Every fourth M bit is a code violation (CV) and is used for superframe synchronization. This can be regarded as the first bit of the superframe. From this reference, bit 3 of the superframe is the service channel bit (S). The S channel bit is transmitted once in each direction in every fourth burst repetition period. Hence the duplex S channel has a data rate of 1 kbit/s. It conveys test loop control information from the LT to the TE/NT and reports of transmission errors from the TE/NT to the LT. Bit 2 and bit 4 of the superframe are T bits. These constitute the 2 kbit/s T channel which extends the T channel of the IOM frame (figure 7) onto the U interface.

## Figure 6 U Interface Transmission/Reception

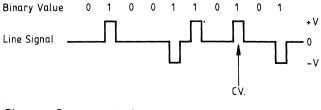

The coding technique used on the U interface is half-bauded AMI code (i.e. with a 50% pulse width). **Figure 7** illustrates the code. As can be seen, a logical '0' corresponds to a neutral level, a logical '1' is coded as alternate positive and negative pulses. The figure also illustrated how a code violation may be achieved (CV); either two successive positive (as shown) or negative pulses.

## Figure 7 Half-Bauded AMI Code

#### Absolute Maximum Ratings

| Parameter                                 | Symbol           | Limit Values                | Unit |

|-------------------------------------------|------------------|-----------------------------|------|

| Ambient temperature under bias            | T <sub>A</sub>   | 0 to 70                     | °C   |

| Storage temperature                       | T <sub>stg</sub> | -65 to 125                  | °C   |

| Voltage on any pin with respect to ground | Vs               | $-0.3$ to $V_{\rm DD}$ +0.3 | V    |

#### Line Overload Protection

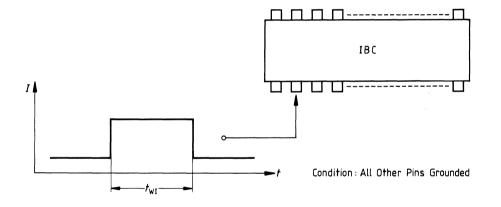

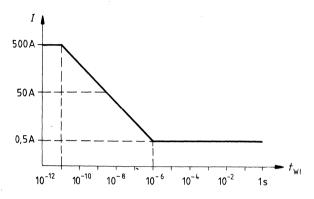

The maximum input current (under overvoltage conditions) is given as a function of the width of a rectangular input current pulse (figure 8).

#### Figure 8

## **Test Condition for Maximum Input Current**

## Figure 9

## **Transmitter Input Current**

The destruction limits are given in **figure 9**  $R_1 \ge 250 \ \Omega$ .

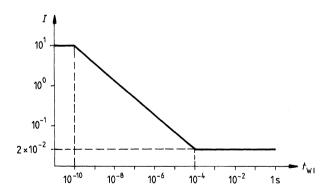

## Figure 10

## **Receiver Input Current**

The destruction limits are given in **figure 10**  $R_1 \ge 250 \Omega$ .

## **DC Characteristics**

$T_{\rm A} = 0$  to 70 °C;  $V_{\rm DD} = 5$  V ± 5%;  $V_{\rm SS} = 0$  V;  $V_{\rm SSA} = 0$  V

|                                                                                                       |                                      | Li                                           | mit Value            | S           |                                                                            |                      |

|-------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------|----------------------|-------------|----------------------------------------------------------------------------|----------------------|

| Parameter                                                                                             | Symbol                               | min.                                         | max.                 | Unit        | Test Conditions                                                            | Remarks              |

| L-input voltage                                                                                       | V <sub>IL</sub>                      | V <sub>SS</sub> -0.4                         | 0.8                  | ۷           |                                                                            |                      |

| H-input voltage                                                                                       | V <sub>IH</sub>                      | 2.0                                          | V <sub>DD</sub> +0.4 | ۷           |                                                                            |                      |

| L-output voltage <sup>1)</sup><br>L-output voltage <sup>2)</sup>                                      | V <sub>OL1</sub><br>V <sub>OL2</sub> |                                              | 0.45<br>0.45         | V<br>V      | $I_{\rm OL}$ = 2 mA<br>$I_{\rm OL}$ = 7 mA                                 | All<br>pins          |

| H-output voltage<br>H-output voltage                                                                  | V <sub>он</sub><br>V <sub>он</sub>   | 2.4<br>V <sub>DD</sub> -0.5                  |                      | V<br>V      | $I_{\rm OH} = -400 \ \mu {\rm A}$<br>$I_{\rm OH} = -200 \ \mu {\rm A}$     | except<br>L01,2      |

| Power supply current operational<br>Power supply current power down                                   | I <sub>CC</sub><br>I <sub>CC</sub>   |                                              | 13<br>1.3            | mA<br>mA    | $V_{\rm DD} = 5$ V, inputs at<br>0 V or $V_{\rm DD}$ , no<br>output loads. | LI<br>XTAL1<br>XTAL2 |

| Input leakage current                                                                                 | ILI                                  | 1                                            | 10                   | μA          | $0V < V_{\rm IN} < V_{\rm DD}$ to $0V$                                     |                      |

| Output leakage current                                                                                | ILO                                  |                                              | 10                   | μA          | 0V <v<sub>OUT<v<sub>DD to 0V</v<sub></v<sub>                               |                      |

| Absolute value of <sup>3)</sup><br>output pulse amplitude <sup>4)</sup><br>$(V_{L01} - V_{L02})^{5)}$ | V <sub>X</sub>                       | 4.45<br>5.25<br>0                            | 5.25<br>4.45<br>0    | V<br>V<br>V | $I_0 \le 16 \text{ mA}$ $I_0 \le 16 \text{ mA}$ $I_0 = 0$                  |                      |

| Pulse width                                                                                           | Pw                                   | 1.22                                         | 1.38                 | μs          |                                                                            | L01,2                |

| Transmitter output impedance                                                                          | R <sub>X</sub>                       | 9                                            | 21                   | Ω           |                                                                            |                      |

| L-input voltage<br>H-input voltage                                                                    | V <sub>IL</sub><br>V <sub>IH</sub>   | V <sub>DD</sub> -0.5<br>V <sub>DD</sub> -0.5 |                      | V<br>V      |                                                                            | XTAL1                |

| L-output voltage<br>H-output voltage                                                                  | V <sub>ol</sub><br>V <sub>oh</sub>   | V <sub>DD</sub> -0.5                         | 0.5                  | V<br>V      | I <sub>O</sub> ≤100 μA<br>C <sub>L</sub> ≤100 pF                           | XTAL2                |

Notes: 1) All outputs except SDO

- 2) Output SDO only

- 3) Positive pulse

- 4) Negative pulse

- 5) No pulse

## Capacitances

$T_{\rm A} = 0$  to 70 °C;  $V_{\rm DD} = 5$  V ± 5%;  $V_{\rm SS} = 0$  V;  $V_{\rm SSA} = 0$  V

|                                             |                                    | Limit Values |        |          |         |

|---------------------------------------------|------------------------------------|--------------|--------|----------|---------|

| Parameter                                   | Symbol                             | min.         | max.   | Unit     | Remarks |

| Input capacitances<br>Output capacitance    | C <sub>IN</sub><br>C <sub>IO</sub> |              | 7<br>7 | pF<br>pF |         |

| Output capacitance against V <sub>SSA</sub> | C <sub>OUT</sub>                   |              | 10     | pF       | L01,2   |

| Load capacitance                            | CL                                 |              | 50     | pF       | XTAL1,2 |

Figure 11 Recommended Oscillator Circuits

Crystal Oscillator Mode

Driving from External Source

#### **AC Characteristics**

$T_{\rm A} = 0$  to 70 °C,  $V_{\rm DD} = 5$  V ± 5%

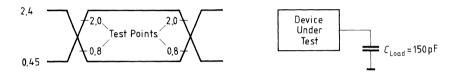

Inputs are driven at 2.4 V for a logic "1" and at 0.4 V for a logic "0". Timing measurements are made at 2.0 V for a logic "1" and at 0.8 V for a logic "0".

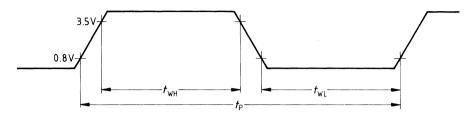

The AC testing input/output waveforms are shown below.

## Figure 12

#### Input/Output Waveform for AC Tests

#### **Clock Timing**

The following timing-descriptions summarizes the clocks produced in the different operating modes and their respective duty cycles. The table also indicates which clocks are derived directly from the crystal and which are synchronized to the line using the on-board DPLL circuitry.

# Table 1Mode Specific Pin Functions

| Mode                  | Name  | Description                | Pin        | I/O | Function                                                                                                                                                                                                                                                                                                       |

|-----------------------|-------|----------------------------|------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LT                    | PFOFF | Power Feed OFF             | X4         | 1   | Puts the IBC into a powerfeed off<br>state. This state is indicated by<br>C/I code HI.                                                                                                                                                                                                                         |

| LT                    | MPF   | Main Power<br>Feed         | ХЗ         | 1   | The 8-bit supply current equivalent<br>is read serially through this pin<br>into I (7:0) from the local power<br>supply. The read is synchronous<br>to the B1 channel in the IOM frame<br>(time slot 0 in LT:mux mode).<br>Used for power supply control by<br>the layer-2 device. Tie low when<br>not in use. |

| TE/NT                 | ENCK  | Enable Clocks              | ХЗ         | I   | Enables clocks in 'deactivated' state. Also during $RST = 0$ , outputs are low impedance when $\overline{ENCK} = 0$ and high impedance otherwise.                                                                                                                                                              |

| NT                    | SSP   | Send Single<br>Pulses      | X1         | 1   | Test mode 1                                                                                                                                                                                                                                                                                                    |

|                       | SCP   | Send Contin.<br>Pulses     | X2         | I   | Test mode 2                                                                                                                                                                                                                                                                                                    |

| LT<br>norm.<br>or SLD | CONF4 | Programmable<br>Output Pin | X0         | 0   | Programmed over monitor channel.<br>Useful to control other devices.                                                                                                                                                                                                                                           |

| LT                    | TS0-2 | Time Slot<br>0 – 2         | X0,<br>1,2 | 1   | In MUX mode, one of eight possible<br>time slots is selected to be read<br>by the device<br>(TS0 – LSB)                                                                                                                                                                                                        |

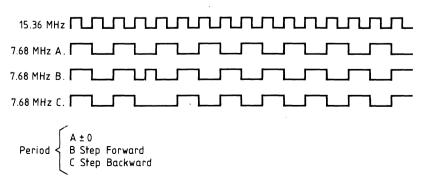

### Figure 13 Output Clock Relationships

**Figure 13** shows the relationship between the various clock outputs form the IBC. The crystal frequency is 15.36 MHz. All clock outputs have a duty cycle of 1:1 except 2.56 MHz (1:2). Note that the following are derived directly from the crystal oscillator; 15.36 MHz, 3.84 and 2.56 MHz. They are not synchronized to the line. Their accuracy will be, to a first order, governed by the crystal accuracy ( $\pm$  100 ppm maximum).

The following clocks are derived both from the crystal and, with the help of the DPLL, from the line; 7.68 MHz, 1.536 MHz, DCLK and FSC. Synchronization may be regarded as a two stage process. Firstly, a synchronous 7.68 MHz signal is derived using the DPLL. Secondly, all other syncronous clocks are derived, by simple division, from 7.68 MHz synchronous. Because of the internal method of synchronization employed, the 7.68 MHz signal may "step forward or back" by 1 crystal period (**see figure 14**). Hence the period of 7.68 MHz, and all synchronous clocks derived from it, may vary by one crystal period ( $\pm$  65 ns). This, to a first order, gives the accuracy of the various synchronous clocks. **Table 2** to **table 6** detail the accuracy of the clock outputs with respect to the symbols.

#### Figure 14 Possible 7.68 MHz Clocks

## Figure 15 Clock Timing Symbols

## Table 2

## DCLK Timing

| Parameter                                                        |                                                      | Limit Values       |                    |                      |                |                 |

|------------------------------------------------------------------|------------------------------------------------------|--------------------|--------------------|----------------------|----------------|-----------------|

|                                                                  | Symbol                                               | min.               | typ.               | max.                 | Unit           | Test Conditions |

| TE/NT 512 kHz<br>TE/NT 512 kHz<br>TE/NT 512 kHz<br>TE/NT 512 kHz | t <sub>P</sub><br>t <sub>WH</sub><br>t <sub>WL</sub> | 1888<br>944<br>944 | 1953<br>977<br>977 | 2019<br>1009<br>1009 | ns<br>ns<br>ns | Output          |

| LT mode<br>LT mode                                               | t <sub>WH</sub><br>t <sub>WL</sub>                   | 90<br>90           |                    |                      | ns<br>ns       | } Input         |

## Table 3 FSC Timing

| Parameter                                                                                |                                                      | Limit Values             |                       |                          |                |                 |

|------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------|-----------------------|--------------------------|----------------|-----------------|

|                                                                                          | Symbol                                               | min.                     | typ.                  | max.                     | Unit           | Test Conditions |

| TE/NT 8 kHz 1:1<br>TE/NT 8 kHz 1:1<br>TE/NT 8 kHz 1:1                                    | t <sub>P</sub><br>t <sub>WH</sub><br>t <sub>WL</sub> | 124.93<br>62.46<br>62.46 | 125<br>62.5<br>62.5   | 125.07<br>62.54<br>62.54 | μs<br>μs<br>μs | _ } Output      |

| TE (SEL) 8 kHz 63:1<br>TE (SEL) 8 kHz 63:1<br>TE (SEL) 8 kHz 63:1<br>TE (SEL) 8 kHz 63:1 | t <sub>P</sub><br>t <sub>WH</sub><br>t <sub>WL</sub> | 124.93<br>122.08<br>1888 | 125<br>123.05<br>1953 | 125.07<br>124.02<br>2019 | μs<br>μs<br>ns |                 |

## Table 4

## X4 Clock Timing

|                 |                 | Limit Values |      |      |      |                           |

|-----------------|-----------------|--------------|------|------|------|---------------------------|

| Parameter       | Symbol          | min.         | typ. | max. | Unit | Test Conditions           |

| TE 2.56 MHz 1:2 | t <sub>P</sub>  | -100         | 390  | +100 | ns   | $OSC \pm 100 \text{ ppm}$ |

| TE 2.56 MHz 1:2 | twn             | -100         | 130  | +100 | ns   | $OSC \pm 100 \text{ ppm}$ |

| TE 2.56 MHz 1:2 | twL             | -100         | 260  | +100 | ns   | $OSC \pm 100 \text{ ppm}$ |

| NT 7.68 MHz 1:1 | t <sub>P</sub>  | 65           | 130  | 196  | ns   |                           |

| NT 7.68 MHz 1:1 | t <sub>wH</sub> | 65           | 65   | 131  | ns   |                           |

| NT 7.68 MHz 1:1 | t <sub>WL</sub> | 65           | 65   | 131  | ns   |                           |

## Table 5 X1 Clock Timing

| Parameter     |                 |      | Limit Valu | es   |      |                        |

|---------------|-----------------|------|------------|------|------|------------------------|

|               | Symbol          | min. | typ.       | max. | Unit | <b>Test Conditions</b> |

| TE: 1.536 MHz | t <sub>P</sub>  | 585  | 651        | 717  | ns   |                        |

| TE: 1.536 MHz | t <sub>wH</sub> | 260  | 326        | 391  | ns   |                        |

| TE: 1.536 MHz |                 | 260  | 326        | 391  | ns   |                        |

| LT* 15.36 MHz |                 | -100 | 65.1       | +100 | ns   | OSC ± 100 ppm          |

| LT* 15.36 MHz | t <sub>wH</sub> | -100 | 65.1       | +100 | ns   | OSC ± 100 ppm          |

| LT* 15.36 MHz | t <sub>WL</sub> | -100 | 65.1       | +100 | ns   | OSC ± 100 ppm          |

\* in normal and SLD modes only

## Table 6

## X0 Clock Timing

|                              |                 |              | Limit Valu | ies          |          |                                |

|------------------------------|-----------------|--------------|------------|--------------|----------|--------------------------------|

| Parameter                    | Symbol          | min.         | typ.       | max.         | Unit     | <b>Test Conditions</b>         |

| TE: 3.84 MHz                 | t <sub>P</sub>  | -100         | 260        | +100         | ns       | OSC ± 100 ppm                  |

| TE: 3.84 MHz<br>TE: 3.84 MHz | t <sub>WH</sub> | -100<br>-100 | 130<br>130 | +100<br>+100 | ns<br>ns | OSC ± 100 ppm<br>OSC ± 100 ppm |

Finally table 7 defined the rise and fall times of DCLK and FSC clocks in the various modes.

## Table 7 DCLK/FSC Rise and Fall Timing

| Parameter           |                | Limit Values |      |                |                |                              |

|---------------------|----------------|--------------|------|----------------|----------------|------------------------------|

|                     | Symbol         | min.         | typ. | max.           | Unit           | Mode                         |

| TRD; DCLK rise time | t <sub>r</sub> |              |      | 50<br>60<br>25 | ns<br>ns<br>ns | NT/TE<br>LT normal<br>LT MUX |

| TFD; DCLK fall time | t <sub>f</sub> |              |      | 50<br>60<br>25 | ns<br>ns<br>ns | NT/TE<br>LT normal<br>LT MUX |

| TFR; FSC rise time  | t <sub>r</sub> |              |      | 50<br>60<br>50 | ns<br>ns<br>ns | NT/TE<br>LT normal<br>LT MUX |

| TFF; FSC fall time  | t <sub>f</sub> |              |      | 50<br>60<br>50 | ns<br>ns<br>ns | NT/TE<br>LT normal<br>LT MUX |

#### **IOM Interface**

Given the clock accuracies defined in the previous section, the following paragraphs define the timing relationship between the data and the DCLK and FSC clocks.

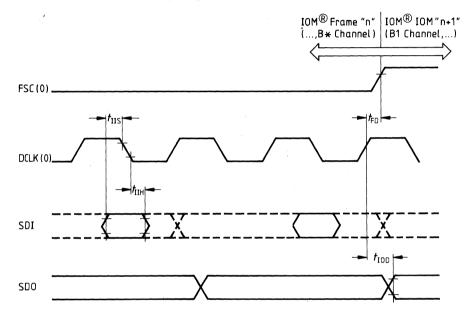

#### Normal Mode Master Mode (TE/NT mode)

#### Normal TE/NT Mode Timing Diagram

#### Normal TE/NT Mode Timing

|                       | Symbol           | Limit Values |      |      | Test                      |

|-----------------------|------------------|--------------|------|------|---------------------------|

| Parameter             |                  | min.         | max. | Unit | Conditions                |

| Frame sync. delay     | t <sub>FD</sub>  | -20          | 20   | ns   | $C_{L} = 100 \text{ pF}$  |

| IOM output data delay | t <sub>IOD</sub> |              | 200  | ns   | $C_{\rm L} = 100  \rm pF$ |

| IOM input data setup  | t <sub>IIS</sub> | 20           |      | ns   |                           |

| IOM input data hold   | t <sub>IIH</sub> | 50           |      | ns   |                           |

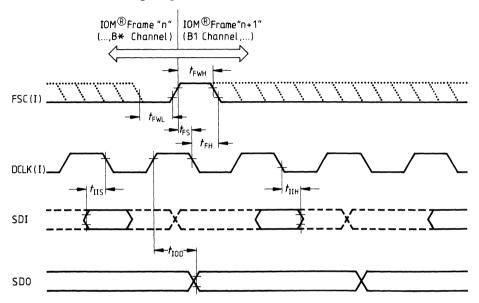

## Slave Mode (LT) Normal LT Mode Timing Diagram

## Normal LT Mode Timing

|                  | Limit Values                                                                                                       |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                   |

|------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol           | min.                                                                                                               | max.                                                                                                                                                                   | Unit                                                                                                                                                                                                                                                                              |

| t <sub>FH</sub>  | 50                                                                                                                 |                                                                                                                                                                        | ns                                                                                                                                                                                                                                                                                |

| t <sub>FS</sub>  | 30                                                                                                                 |                                                                                                                                                                        | ns                                                                                                                                                                                                                                                                                |

| t <sub>FWH</sub> | 80                                                                                                                 |                                                                                                                                                                        | ns                                                                                                                                                                                                                                                                                |

| t <sub>FWL</sub> | 2150                                                                                                               |                                                                                                                                                                        | ns                                                                                                                                                                                                                                                                                |

| t <sub>IOD</sub> |                                                                                                                    | 200                                                                                                                                                                    | ns                                                                                                                                                                                                                                                                                |

| t <sub>IIS</sub> | 20                                                                                                                 |                                                                                                                                                                        | ns                                                                                                                                                                                                                                                                                |

| t <sub>IIH</sub> | 50                                                                                                                 |                                                                                                                                                                        | ns                                                                                                                                                                                                                                                                                |

|                  | t <sub>FH</sub><br>t <sub>FS</sub><br>t <sub>FWH</sub><br>t <sub>FWL</sub><br>t <sub>IOD</sub><br>t <sub>IIS</sub> | Symbol         min.           t <sub>FH</sub> 50           t <sub>FS</sub> 30           t <sub>FWH</sub> 80           t <sub>FWL</sub> 2150           t <sub>IOD</sub> | Symbol         min.         max.           t <sub>FH</sub> 50         -           t <sub>FS</sub> 30         -           t <sub>FWH</sub> 80         -           t <sub>FWL</sub> 2150         -           t <sub>IOD</sub> 200         -           t <sub>IIS</sub> 20         - |

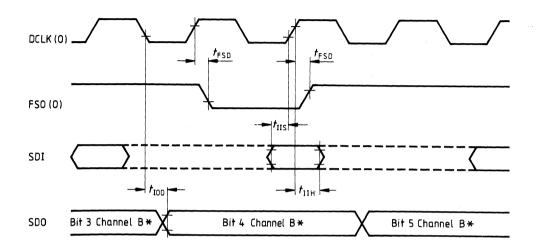

## TE Inverted Mode Inverted TE Mode Timing Diagram

## Inverted TE Mode Timing

|                       | Symbol           | Limit Values |      |      | Test                     |

|-----------------------|------------------|--------------|------|------|--------------------------|

| Parameter             |                  | min.         | max. | Unit | Conditions               |

| Frame sync delay      | t <sub>FSD</sub> | -20          | 20   | ns   | $C_{L} = 100 \text{ pF}$ |

| IOM output data delay | t <sub>IOD</sub> |              | 200  | ns   | $C_{L} = 100 \text{ pF}$ |

| IOM input data setup  | t <sub>IIS</sub> | 20           |      | ns   |                          |

| IOM input data hold   | t <sub>IIH</sub> | 50           |      | ns   |                          |

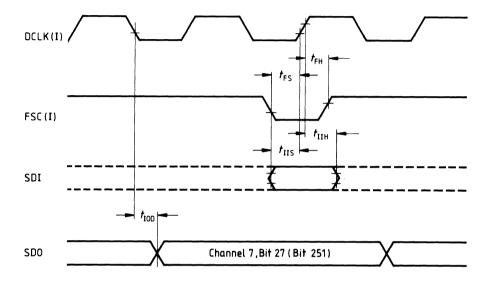

## LT MUX Mode Inverted LT MUX Mode Timing Diagram

#### Inverted LT MUX Mode Timing

|                       |                  | Limit Values |      |      |

|-----------------------|------------------|--------------|------|------|

| Parameter             | Symbol           | min.         | max. | Unit |

| Frame sync hold       | t <sub>FH</sub>  | 50           |      | ns   |

| Frame sync setup      | t <sub>FS</sub>  | 20           |      | ns   |

| Frame sync high       | t <sub>FH</sub>  | 124.8        |      | μs   |

| Frame sync low        | t <sub>EL</sub>  | 70           | 200  | ns   |

| IOM output data delay | t <sub>IOM</sub> |              | 200  | ns   |

| IOM input data setup  | t <sub>IIS</sub> | 20           |      | ns   |

| IOM output data hold  | t <sub>IIH</sub> | 50           |      | ns   |

#### **Receiver Stage Properties**

#### **Receiver Stage Properties**

| Input Stage / | Measured Property                               | dB              |

|---------------|-------------------------------------------------|-----------------|

| Line amplifie | r — dynamic range<br>— resolution (128 setting) | 0 – 30<br>0.236 |

| Anti-aliasing | filter and low pass filters                     |                 |

| > 1.1 MHz     | <ul> <li>minimum attenuation</li> </ul>         | 30              |

| > 1.1 MHz     | - typical attenuation                           | 35              |

| Equalizer     | – dynamic range                                 | 0 – 15.36 dB    |

|               | <ul> <li>resolution (8 settings)</li> </ul>     | 2.194           |