# Signal Processing Codec Filter (SICOFI)

#### **Preliminary Data**

CMOS IC

**PEB 2060**

| Туре       | Ordering Code | Package        |

|------------|---------------|----------------|

| PEB 2060-P | Q67100-Z170   | P-DIP-22       |

| PEB 2060-N | Q67100-Z8393  | PL-CC-28 (SMD) |

The Signal Processing Codec Filter (SICOFI®) PEB 2060 is a fully integrated PCM codec (coder/decoder) and transmit/receive filter fabricated in advanced CMOS technology for applications in digital telecommunication systems. Based on a digital filter concept, the PEB 2060 provides improved transmission performance and high flexibility. The digital signal processing approach supports software controlled adjustment of the analog behavior, including attractive features such as programmable transhybrid balancing, impedance matching, gain and frequency response correction.

## Features

- Single chip codec and filter

- Band limitation according to CCITT and AT&T recommendations

- Digital Signal Processing techniques

- Digital voice transmission

- PCM encoded (A-law or µ-law)

- linear (16 bit 2s complement)

- Programmable digital filters for

- impedance matching

- transhybrid balancing

- gain

- frequency response correction

- Configurable three pin serial interface

- 512-kHz-SLD-Bus (e.g. to PEB 2050/51)

- burst mode with bit rates up to 8 MHz

- Programmable signaling interface to peripherals (e.g. SLIC)

- High performance A/D and D/A conversion

- Programmable analog gain

- Advanced test capabilities

- three digital loop back modes

- two analog loop back modes

- on chip sine wave generation

- No trimming or adjustments

- No external components

- Variable SICOFI Master Clock selection

- Signaling expansion possible

- Prepared for three-party conferencing

- Advanced low power 2 μCMOS technology

- Power supply +/-5 V

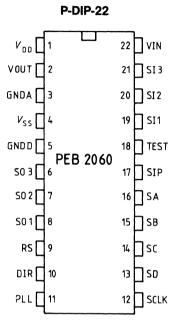

# **Pin Configuration**

(top view)

PL-CC-28

.....

|                   |             | TUOV du | יט<br>2 מיט<br>2 |                    |        | -    |    |   |      |

|-------------------|-------------|---------|------------------|--------------------|--------|------|----|---|------|

| N.C. 1            | 4           |         |                  | Ò                  |        |      | 26 | 5 | SI2  |

| GNDA              | 5           |         |                  | -                  |        |      | 25 | þ | N.C. |

| V <sub>SS</sub> I | 6           |         |                  |                    |        |      | 24 | Þ | SI1  |

| GNDDI             | <b>d</b> 7  |         |                  |                    |        |      | 23 | þ | TEST |

| S031              |             | PE      | P                | 20                 | )6(    | )    | 22 | ٦ | N.C. |

| S02               | 9           |         |                  |                    |        |      | 21 | þ | SIP  |

| S01               | <b>d</b> 10 |         |                  |                    |        |      | 20 | þ | SA   |

| N.C.              | 11          |         |                  |                    |        |      | 19 | þ | SB   |

| RS                | 12          |         |                  |                    |        |      | 18 | þ | SC   |

|                   | l           | 13      | 14               | 15                 | 16     | 17   |    |   |      |

|                   | -           | DIRC    | PLL              | <b>ט</b> יט<br>אינ | SCLK D | so d |    |   |      |

| Pin No.<br>P-DIP     | Pin No.<br>PL-CC     | Symbol               | Input (I)<br>Output (O)  | Function                                                                                                                                                                                                                                                              |  |  |

|----------------------|----------------------|----------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1                    | 1                    | V <sub>DD</sub>      | 1                        | Power supply +5 V                                                                                                                                                                                                                                                     |  |  |

| 4                    | 6                    | V <sub>SS</sub>      |                          | Power supply -5 V                                                                                                                                                                                                                                                     |  |  |

| 3<br>5               | 5<br>7               | GNDA<br>GNDD         | 1                        | Ground analog, not internally connected to GNDI<br>All analog signals are referred to this pin.<br>Ground digital, not internally connected to GND,<br>All digital signals are referred to this pin.                                                                  |  |  |

| 22                   | 28                   | VIN                  |                          | Analog voice input to transmit path.                                                                                                                                                                                                                                  |  |  |

| 2                    | 3                    | VOUT                 | 0                        | Analog voice output of the received digital voice.                                                                                                                                                                                                                    |  |  |

| 12                   | 16                   | SCLK                 |                          | Slave clock.                                                                                                                                                                                                                                                          |  |  |

| 10                   | 13                   | DIR                  |                          | Frame synchronisation signal (direction signal).                                                                                                                                                                                                                      |  |  |

| 17                   | 21                   | SIP                  | /O                       | Serial Interface Port, bidirectional serial data port.                                                                                                                                                                                                                |  |  |

| 9<br>18<br>11        | 12<br>23<br>14       | RS<br>TEST<br>PLL    | 1                        | Reset input, active high, RS forces the SICOFI to<br>power down mode and resets the configuration<br>registers.<br>Test input, normally connected to GNDD.<br>Master clock selection (PLL/external clock).                                                            |  |  |

| 19                   | 24                   | SI1                  |                          | Signaling Inputs. Data present at SI is sampled and transmitted via the serial interface.                                                                                                                                                                             |  |  |

| 20                   | 26                   | SI2                  |                          |                                                                                                                                                                                                                                                                       |  |  |

| 21                   | 27                   | SI3                  |                          |                                                                                                                                                                                                                                                                       |  |  |

| 8                    | 10                   | SO1                  | 0                        | Signaling Outputs. Data received via the serial interface is latched and fed to these outputs.                                                                                                                                                                        |  |  |

| 7                    | 9                    | SO2                  | 0                        |                                                                                                                                                                                                                                                                       |  |  |

| 6                    | 8                    | SO3                  | 0                        |                                                                                                                                                                                                                                                                       |  |  |

| 16<br>15<br>14<br>13 | 20<br>19<br>18<br>17 | SA<br>SB<br>SC<br>SD | I/O<br>I/O<br>I/O<br>I/O | Programmable I/O signaling pins. Each of these<br>pins may be declared input or output individually<br>with adequate SICOFI status settings. If 2<br>SICOFIs are connected to 1 serial interface,<br>pin SA (high/low) assigns voice, control and<br>signaling bytes. |  |  |

# **Pin Definitions and Functions**

#### **SICOFI** Principles

The SICOFI codec filter solution is a highly digital approach utilizing the advantages of digital signal processing such as excellent performance, high flexibility, easy testing, no sensitivity to fabrication and temperature variations, no problems with crosstalk and power supply rejection.

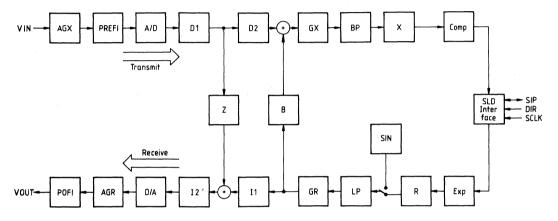

# Figure 1

#### SICOFI Signal Flow Graph

## **Transmit Direction**

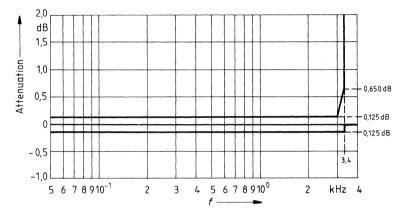

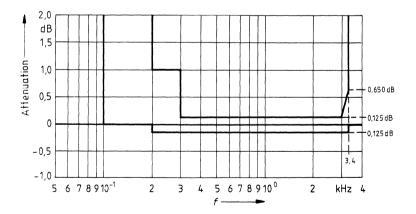

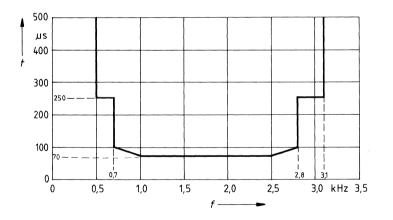

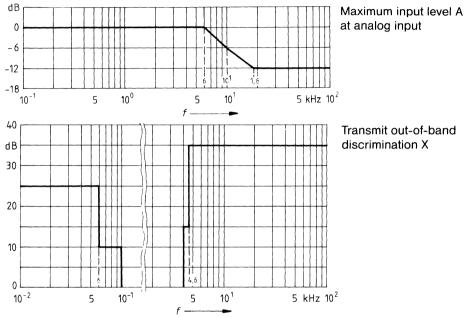

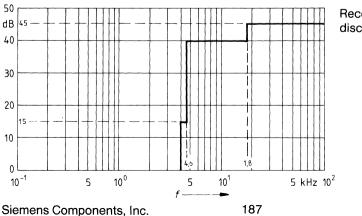

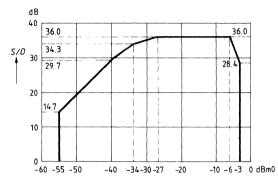

The analog input signal is A/D converted, digitally filtered and transmitted either PCMencoded or linear. Antialiasing is done with a 2nd order Sallen-Key prefilter (PREFI). The A/D Converter (ADC) is a modified slopeadaptive interpolative sigma-delta modulator with a sampling rate of 128 kHz. Digital downsampling to 8 kHz is done by subsequent decimation filters D1 and D2 together with the PCM bandpass filter (BP).

## **Receive Direction**

The digital input signal is received PCM-encoded or linear, digitally filtered and D/A converted to generate the analog output signal. Digital interpolation up to 128 kHz is done by the PCM lowpass filter (LP) and the interpolation filters I1 and I2. The D/A Converter (DAC) output is fed to the 2nd order Sallen-Key postfilter (POSI).

#### Programmable Functions

The high flexibility of the SICOFI is based on a variety of user programmable filters, which are analog gain adjustment AGR and AGX, digital gain adjustment GR and GX, frequency response adjustment R and X, impedance matching filter Z and the transhybrid balancing filter B.

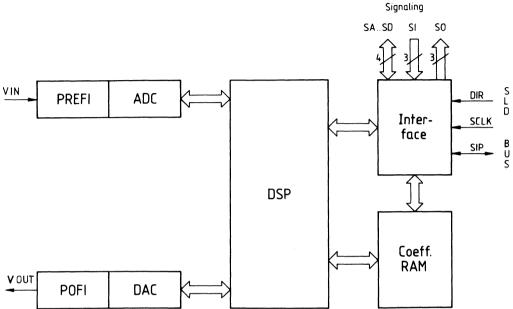

The SICOFI bridges the gap between analog and digital voice signal transmission in modern telecommunication system.

High performance oversampling analog-to-digital converter (ADC) and digital-to-analog converter (DAC) provide the conversion accuracy required. An analog antialiasing prefilter (PREFI) and smoothing postfilter (POFI) is included. The dedicated on chip digital signal processor (DSP) handles all the algorithms necessary, e.g. PCM bandpass filtering, sample rate conversion and PCM companding. The three pin serial SLD-Bus interface handles digital voice transmission and SICOFI feature control. Specific filter programming is done by downloading coefficients to the coefficient ram (CRAM).

The ten pin parallel signaling interface provides for a powerful per line SLIC control.

#### Serial Interface

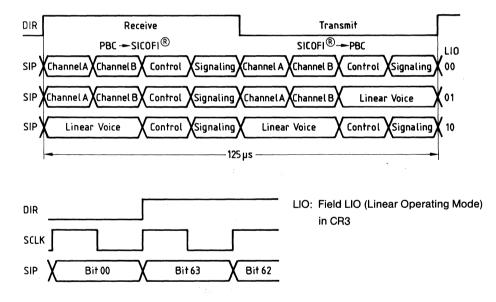

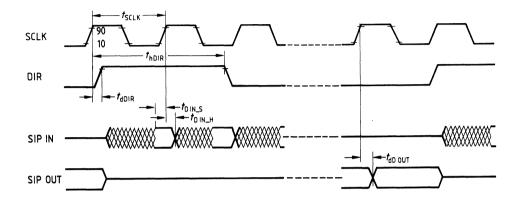

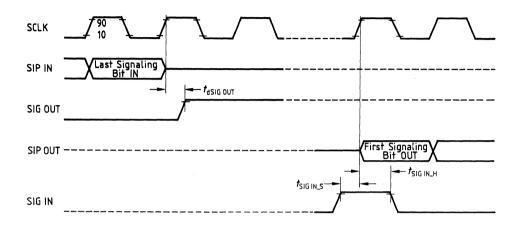

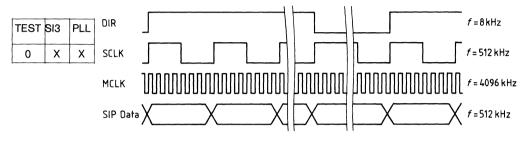

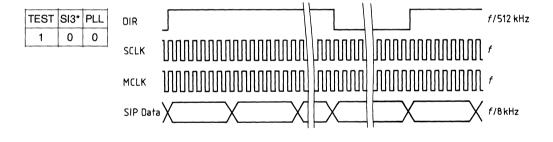

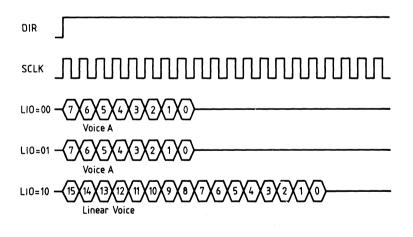

The exchange of data on the SLD-Bus is based on a bidirectional, bitserial interface consisting of three pins: SIP, DIR and SCLK.

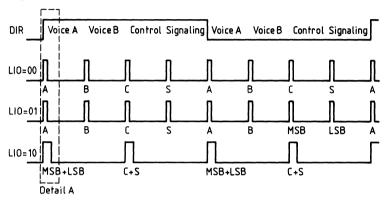

Data is written or read out on the Serial Interface Port (SIP) under control of the frame synchronisation signal DIR with a period of 125  $\mu$ s\*). The interface clock frequency supplied at the Slave CLocK pin SCLK is 512 kHz\*). The rate of the serial data stream on the SIP pin is 512 kbit/s, that is 64 bits per each 8 kHz frame\*).

Starting with the rising edge DIR, four bytes of information are transfered on the SLD-Bus to the SICOFI, followed by four bytes from the SICOFI to the SLD-Bus.

Bit 7 is the first bit transfered and bit 0 is the last one of each byte.

# Figure 3

#### Byte Sequence and Timing at Serial Interface Port SIP

<sup>\*)</sup> for applications with other clock rates see appendix A

Siemens Components, Inc.

## Programming

A message-orientated byte transfer is used, due to the fact that the SICOFI needs extended control information. One control byte per frame and direction is transfered. With the appropriate received commands, data can be written to the SICOFI or read from the SICOFI onto the SLD-bus.

Data transfer to the SICOFI starts with a write command, followed by up to 8 bytes of data. The SICOFI responds to a read command with the requested information, starting at the next transmission period. If no status modification or data exchange is required a NOP byte is transfered (see Programming Procedure).

#### **Classes of Control Bytes**

The 8-bit control bytes consist of either commands, status information or data. There are three different classes of SICOFI commands:

- NOP NO OPERATION: no status modification or data exchange

- SOP STATUS OPERATION: SICOFI status setting/monitoring

- COP COEFFICIENT OPERATION: filter coefficient setting/monitoring

The class of command is selected by bit 2 and 3 of the control byte as shown below. Due to the extended SICOFI feature control facilities, SOP- and COP-commands contain additional information.

| BIT | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|---|---|---|---|---|---|---|---|

| NOP | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| SOP |   |   |   |   | 0 | 1 |   |   |

| COP |   |   |   |   | X | 0 |   |   |

## NOP Command

If no status modification of the SICOFI or control data exchange is required, a No Operation Byte NOP is transfered.

| BIT | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|---|---|---|---|---|---|---|---|

|     | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

X .... don't care

## SOP Command

To modify or evaluate the SICOFI status, the contents of up to four configuration registers CR1, CR2, CR3 and CR4 may be transferred to or from the SICOFI. This is done by a SOP-Command (Status Operation Command).

| BIT  | 7                                                                                                                                                                    | 6                           | 5                    | 4           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2            | 1                                     | 0           |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------|-------------|--|

|      | AD                                                                                                                                                                   | R/W                         | PU                   | TR          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1            | LS                                    | EL          |  |

|      |                                                                                                                                                                      |                             | <u></u>              | •           | <ul> <li>A 2000 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 10</li></ul> |              | • • • • • • • • • • • • • • • • • • • |             |  |

| AD   | Address In                                                                                                                                                           | formation                   | AD = (<br>AD = 1     |             | SICOFI add                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                       |             |  |

|      | This bit is e                                                                                                                                                        | evaluated if                |                      |             | SICOFI add                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              | ort.                                  |             |  |

|      |                                                                                                                                                                      | s accessed<br>Iling Byte, I |                      |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | el at pin SA |                                       |             |  |

|      |                                                                                                                                                                      |                             | -                    | -           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |                                       |             |  |

| R/W  | Read/Write                                                                                                                                                           | e Informatio                |                      |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |                                       |             |  |

|      | R/W = 1 Read from SICOFI<br>Enables reading from the SICOFI or writing information to the SICOFI.                                                                    |                             |                      |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |                                       |             |  |

| PU   | -                                                                                                                                                                    | Power Dov                   |                      |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -            | -up mode                              | (operating) |  |

|      | (see also (                                                                                                                                                          | CR3)                        | PU = (               |             | ets the SIC<br>ndby mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •            | ver-down                              |             |  |

| TR   | Three Part                                                                                                                                                           | y Conferen                  | ce TR = <sup>-</sup> | l The       | received v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | oice bytes   | of Channel                            | A and       |  |

|      | Three Party Conference $TR = 1$ The received voice bytes of Channel A and<br>Channel B are added (A + B). The result is<br>filtered, D/A converted and transfered to |                             |                      |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |                                       |             |  |

|      |                                                                                                                                                                      |                             |                      |             | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              | e also CR3                            |             |  |

| LSEL | Length Sel                                                                                                                                                           | ect Informa                 | tion (see a          | also Progra | amming Pr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ocedure)     |                                       |             |  |

|      | This two bi                                                                                                                                                          | t field ident               | ifies the nu         | umber of si | ubsequent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | data bytes   |                                       |             |  |

- LSEL = 0 0 no byte following LSEL = 1 1 CR1 is following LSEL = 1 0 CR2 and CR1 are following

- LSEL = 0 1 CR4, CR3, CR2 and CR1 are following in this case the PU and TR bits are not overwritten.

## CR1 Configuration Register 1

This configuration register is used for enabling/disabling the programmable digital filters (DB..RG) and for accessing tesmodes (TM1).

| BIT | 7                  | 6           | 5  | 4                                                     | 3  | 2 | 1     | 0 |  |

|-----|--------------------|-------------|----|-------------------------------------------------------|----|---|-------|---|--|

|     | DB                 | RZ          | RX | RR                                                    | RG |   | T M 1 |   |  |

|     |                    |             |    |                                                       |    |   |       |   |  |

| DB  | Disable B-         | Filter      |    | B = 0:B-<br>B = 1:B-                                  |    |   |       |   |  |

| RZ  | Z Restore Z-Filter |             |    | RZ = 0: Z-Filter disabled<br>RZ = 1: Z-Filter enabled |    |   |       |   |  |

| RX  | Restore X-         | Filter      |    | RX = 0:X-Filter disabled<br>RX = 1:X-Filter enabled   |    |   |       |   |  |

| RR  | Restore R-         | Filter      |    | R = 0:R-<br>R = 1:R-                                  |    |   |       |   |  |

| RG  | Restore G          | (-GR-Filter |    | G = 0:GX<br>G = 1:GX                                  |    |   |       |   |  |

| ТМ1 |   |   | TESTMODES                                                   |

|-----|---|---|-------------------------------------------------------------|

| 0   | 0 | 0 | No test mode                                                |

| 0   | 0 | 1 | Analog loop back via Z-filter (H (Z) = 1) <sup>1)</sup>     |

| 0   | 1 | 0 | Disable highpass filter (part of bandpass BP)               |

| 0   | 1 | 1 | Cut off receive path                                        |

| 1   | 0 | 0 | Initialize data ram                                         |

| 1   | 1 | 0 | Digital loop back via B-filter (H (B) = $1$ ) <sup>2)</sup> |

| 1   | 1 | 1 | Digital loop back via PCM-register <sup>3)</sup>            |

<sup>&</sup>lt;sup>1)</sup> Output of the interpolation filter 1 I1 is set to 0. Value of transfer function of the Z-filter is 1 (not programmable).

<sup>&</sup>lt;sup>2)</sup> Output of the low pass decimation filter 2 D2 is set to 0.

Value of transfer function of the B-filter is 1 (not programmable).

<sup>&</sup>lt;sup>3)</sup> PCM in = PCM out. This testmode is also available in standby mode.

| CR2 | Configuration Register 2 |   |   |   |    |    |     |     |  |  |

|-----|--------------------------|---|---|---|----|----|-----|-----|--|--|

| BIT | 7                        | 6 | 5 | 4 | 3  | 2  | 1   | 0   |  |  |

|     | D                        | С | В | А | EL | AM | μ/Α | PCS |  |  |

The first four bits D...A in this register, program the four bidirectional signaling pins SD...SA. With two SICOFIs on one SLD port only pin SD can be used, pin SA is always input in this case and indicates the address of the SICOFI.

SA = 0: A-SICOFI, SA = 1: B-SICOFI (see also bit AD in SOP-command).

| D  | Signaling Pin SD          | D = 0<br>D = 1   | SD is output<br>SD is input                    |

|----|---------------------------|------------------|------------------------------------------------|

| С  | Signaling Pin SC          | C = 0<br>C = 1   | SC is output<br>SC is input                    |

| В  | Signaling Pin SB          | B = 0<br>B = 1   | SB is output<br>SB is input                    |

| А  | Signaling Pin SA          | A = 0<br>A = 1   | SA is output<br>SA is input                    |

| EL | Signaling Expansion Logic | EL = 0<br>EL = 1 | No expansion logic<br>Expansion logic provided |

signaling expansion logic is only possible with one SICOFI on port (see also Signaling Byte)

| AM | Address Mode | AM = 0 | Two SICOFIs on SLD port |  |

|----|--------------|--------|-------------------------|--|

|    |              | AM = 1 | One SICOFI on SLD port  |  |

|    |              |        |                         |  |

The SICOFI access to the SLD-Bus voice channel is controlled by AM and TR.

|    |    | Receive (SLD-               | Bus → SICOFI) | Transmit (SICOFI→SLD-Bus)  |           |  |

|----|----|-----------------------------|---------------|----------------------------|-----------|--|

| AM | TR | SICOFI A                    | SICOFI B      | SICOFI A                   | SICOFI B  |  |

| 0  | 0  | channel A                   | channel B     | channel A                  | channel B |  |

| 0  | 1  | channel B                   | channel A     | channel B                  | channel A |  |

| 1  | 0  | channel A                   | _             | channel A, B <sup>1)</sup> | -         |  |

| 1  | 1  | channel A + B <sup>2)</sup> | _             | channel A, B <sup>1)</sup> | _         |  |

| PCM-Law                      | μ/A = 0<br>μ/A = 1 | A-Law<br>μ-Law (μ255 PCM)                                 |

|------------------------------|--------------------|-----------------------------------------------------------|

| Programmed B-Filter Coeffici |                    |                                                           |

|                              | PCS = 0            | Programmed coefficients                                   |

|                              | PCS = 1            | Fixed coefficients                                        |

|                              |                    | $\mu/A = 1$<br>Programmed B-Filter Coefficient<br>PCS = 0 |

<sup>&</sup>lt;sup>1)</sup> The SICOFI transmits the same byte in channel A and B.

<sup>2)</sup> Three Party Conference.

| CR3 | Config    | uration            | Register   | 3               |                       |                    |                      |     |   |  |

|-----|-----------|--------------------|------------|-----------------|-----------------------|--------------------|----------------------|-----|---|--|

| BIT | 7         |                    | 6          | 5               | 4                     | 3                  | 2                    | 1   | 0 |  |

|     |           | A G X              |            | AC              | G R                   | PU                 | TR                   | LIO |   |  |

|     |           |                    |            |                 |                       |                    |                      |     |   |  |

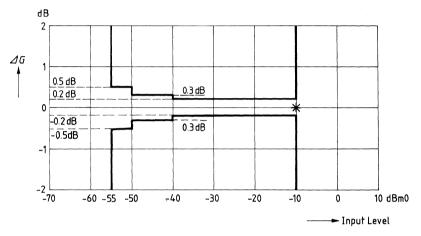

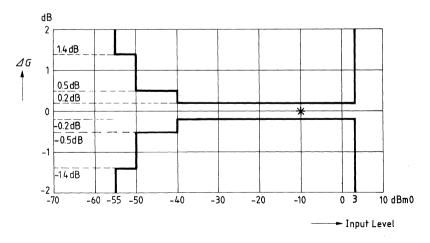

| AGX | Analo     | g Gain (           | Control Tr | ansmit-P        | ath                   |                    | <b>n</b> ,           |     |   |  |

|     | AGX       | = 0                | 0          | 0 dE            | 3                     |                    |                      |     |   |  |

|     | AGX       | = 0                | 1          | 6 dE            | 3 amplifica           | tion               |                      |     |   |  |

|     | AGX       | = 1                | 0          | 12 dE           | 3 amplifica           | tion               |                      |     |   |  |

|     | AGX       | = 1                | 1          | 14 dE           | 3 amplifica           | tion               |                      |     |   |  |

| AGR | Analo     | g Gain (           | Control Re | eceive-Pa       | ath                   |                    |                      |     |   |  |

|     | AGR       | = 0                | 0          | 0 dE            | 3                     |                    |                      |     |   |  |

|     | AGR = 0 1 |                    |            |                 | 3 attenuatio          | on                 |                      |     |   |  |

|     | AGR       | = 1                | 0          | 12 dE           | 3 attenuatio          | on                 |                      |     |   |  |

|     | AGR       | = 1                | 1          | 14 dE           | 3 attenuatio          | on                 |                      |     |   |  |

| PU  | Power     | Up/Po              | wer Dowi   | 1 <sup>1)</sup> | - W                   |                    |                      |     |   |  |

|     | PU        | = 0                |            | Powe            | er Down (st           | andby)             |                      |     |   |  |

|     | PU        | = 1                |            | Powe            | r Up (oper            | ating)             |                      |     |   |  |

| TR  | Three     | Party C            | onferenc   | e/Revers        | e Operatin            | g Mode <b>(s</b> e | e CR2) <sup>1)</sup> |     |   |  |

| LIO | Linear    | <sup>r</sup> Opera | ting Mode  | e (see sei      | rial interfac         | ce)                |                      |     |   |  |

|     | LIO       | = 0                | 0          | PCM             | mode                  |                    |                      |     |   |  |

|     | LIO       | = 0                | 1          | Linea           | r mode 1 <sup>2</sup> | )                  |                      |     |   |  |

|     | LIO       | = 1                | 0          | Linea           | r mode 2              |                    |                      |     |   |  |

|     | (Chan     | ge of li           | near mod   | e becom         | es valid in           | the next D         | IR-cycle).           |     |   |  |

<sup>1)</sup> The bits PU and TR may also be overwritten by a SOP command with LSEL = 0 1 (PU and TR are part of the SOP command).

With LSEL = 0 1, the bits PU and TR in the SOP command are ignored. <sup>2)</sup> Subsequent to a SOP/COP-read command the control and signaling information is transmitted instead of linear voice.

|     |    |     |   | U U |                                                            |                                                           |                   |                          |                 |   |  |

|-----|----|-----|---|-----|------------------------------------------------------------|-----------------------------------------------------------|-------------------|--------------------------|-----------------|---|--|

| BIT |    | 7   |   | 6   | 5                                                          | 4                                                         | 3                 | 2                        | 1               | 0 |  |

|     |    |     | 1 | ТМЗ |                                                            | 0                                                         | 0                 |                          | T M 4           |   |  |

|     |    |     |   |     | •                                                          |                                                           |                   |                          |                 |   |  |

|     | T  | N 3 |   |     | TES                                                        | TMODE                                                     | 5                 |                          |                 |   |  |

|     | 0  | 0   | 0 |     | No te                                                      | st mode                                                   |                   |                          |                 |   |  |

|     | 0  | 0   | 1 |     | Additi                                                     | Additional + 6 dB digital gain in transmit direction (GX) |                   |                          |                 |   |  |

|     | 0  | 1   | 1 |     | Additional + 12 dB digital gain in transmit direction (GX) |                                                           |                   |                          |                 |   |  |

|     | 1  | 0   | 0 |     | Enabl                                                      | le on chip s                                              | sine wave g       | generatior               | ן <sup>1)</sup> |   |  |

|     | 1  | 1   | 0 |     | Far ai                                                     | nalog loop                                                | back <sup>2</sup> |                          |                 |   |  |

|     |    |     |   |     |                                                            |                                                           |                   |                          |                 |   |  |

|     | TN | 4   |   |     | TES                                                        | TMODE                                                     | 5                 |                          |                 |   |  |

|     | 0  | 0   | 0 |     | No te                                                      | st mode                                                   |                   |                          |                 |   |  |

|     | 1  | 0   | 0 |     | Digita                                                     | l loop bac                                                | k via analc       | og port (V <sub>IN</sub> | $V = V_{OUT}$   |   |  |

## CR4 Configuration Register 4

#### **COP** Command

With a COP command coefficients for the programmable filters can be written to the SICOFI coefficient ram or transmitted on the SLD-bus for verification.

| BIT | 7  | 6   | 5 | 4 | 3    | 2 | 1 | 0 |

|-----|----|-----|---|---|------|---|---|---|

|     | AD | R/W |   |   | CODE |   |   |   |

AD Address Information

A-SICOFI addressed B-SICOFI addressed

AD = 1 B-SICOFI address This bit is evaluated with two SICOFIs on one SLD-port only.

AD = 0

With two SICOFIs on port, a SICOFI is identified, if AD is consistent with the level at pin SA (see Signaling Byte, Programming Procedure).

R/W Read/Write Information R/W = 0

Write to SICOFI

R/W = 1 Read from SICOFI

This bit indicates whether filter coefficients are written to the SICOFI or read from the SICOFI.

<sup>2)</sup> The output of the X-Filter is fed to the input of the R-Filter (8 kHz, 16 bit linear).

<sup>&</sup>lt;sup>1)</sup> With the R-Filter disabled a 2 kHz, 0 dBm0 sine wave signal is fed to the input of the receive Lowpass Filter LP (other frequencies see Appendix B).

# CODE

| 0 | 0 | 0 | 0 | 1 | 1 | B-Filter coefficients part 1   | (followed by 8 bytes of data) |

|---|---|---|---|---|---|--------------------------------|-------------------------------|

| 0 | 0 | 1 | 0 | 1 | 1 | B-Filter coefficients part 2   | (followed by 8 bytes of data) |

| 0 | 1 | 0 | 0 | 1 | 1 | Z-Filter coefficients          | (followed by 8 bytes of data) |

| 0 | 1 | 1 | 0 | 0 | 0 | B-Filter delay coefficients    | (followed by 4 bytes of data) |

| 1 | 0 | 0 | 0 | 1 | 1 | X-Filter coefficients          | (followed by 8 bytes of data) |

| 1 | 0 | 1 | 0 | 1 | 1 | R-Filter coefficients          | (followed by 8 bytes of data) |

| 1 | 1 | 0 | 0 | 0 | 0 | GX- and GR-Filter coefficients | (followed by 4 bytes of data) |

Other codes are reserved for future use.

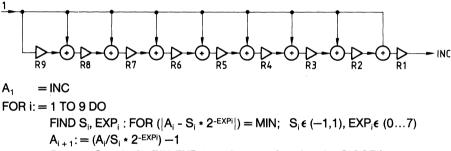

#### **Data Byte Format**

| BIT | 7    | 6       | 5        | 4 | 3    | 2       | 1        | 0 |

|-----|------|---------|----------|---|------|---------|----------|---|

|     | SIGN | 1       | EXPONENT | _ | SIGN |         | EXPONENT | - |

|     | L    | COEFFIC | CIENT 1  |   |      | COEFFIC | CIENT 2  |   |

Each four bit coefficient represents a factor of SIGN x 2-EXPONENT

Subsequent to reading the filter coefficients form the SICOFI CR2 and CR1 are transmitted additionally!!

# Signaling Byte

The signaling interface of the SICOFI consists of 10 pins.

- 3 transmit signaling inputs: SI1, SI2 and SI3

- 3 receive signaling outputs: SO1, SO2 and SO3

- 4 bidirectional programmable signaling pins: SA, SB, SC and SD

Data present at SI1..SI3 and possibly at some or all of SA..SD (if programmed as inputs) are sampled and transfered serially on SIP onto the SLD-bus. Data received serially on SIP from the SLD-Bus are latched and fed to SO1..SO3 and possibly to some of SA..SD if programmed as output.

The signaling field format is generally:

# In Receive Direction:

| BIT      | 7           | 6    | 5   | 4  | 3  | 2  | 1  | 0   |

|----------|-------------|------|-----|----|----|----|----|-----|

|          | SO1         | SO2  | SO3 | SD | SC | SB | SA | SEL |

| In Trans | smit Direct | ion: |     |    |    |    |    |     |

| BIT      | 7           | 6    | 5   | 4  | 3  | 2  | 1  | 0   |

|          | SI1         | SI2  | SI3 | SD | SC | SB | SA | SEL |

where SEL is the signaling expansion bit if EL = 1 in CR2.

|         |     |     | Recei | ve Si | gnalin | g Byte | 9   |    |     | Tra | nsm | it Si | gnali | ng B | yte |    |

|---------|-----|-----|-------|-------|--------|--------|-----|----|-----|-----|-----|-------|-------|------|-----|----|

| Bit     | 7   | 6   | 5     | 4     | 3      | 2      | 1   | 0  | 7   | 6   | 5   | 4     | 3     | 2    | 1   | 0  |

| 1 Case  | SO1 | SO2 | SO3   | Х     | х      | х      | х   | х  | SI1 | SI2 | SI3 | SD    | SC    | SB   | SA  | 0  |

| 2       | SO1 | SO2 | SO3   | Х     | х      | х      | х   | х  | SI1 | SI2 | SI3 | SD    | sc    | SB   | SA  | Z  |

| 3       | SO1 | SO2 | SO3   | SD    | SC     | SB     | SA  | х  | SI1 | SI2 | SI3 | 0     | 0     | 0    | 0   | 0  |

| 4       | SO1 | SO2 | SO3   | SD    | SC     | SB     | SA  | х  | SI1 | SI2 | SI3 | Z     | Z     | Z    | Z   | Z  |

| 5 A-SIC | SO1 | SO2 | SO3   | Х     | х      | х      | х   | х  | SI1 | SI2 | SI3 | SD    | Z     | Z    | Z   | Z  |

| B-SIC   | х   | х   | х     | Х     | SO1    | SO2    | SO3 | х  | Z   | Z   | Z   | Z     | SI1   | SI2  | SI3 | SD |

| 6 A-SIC | SO1 | SO2 | SO3   | SD    | Х      | X      | х   | х  | SI1 | SI2 | SI3 | 0     | Z     | Z    | Z   | Z  |

| B-SIC   | Х   | х   | х     | Х     | SO1    | SO2    | SO3 | SD | Z   | Z   | Z   | Z     | SI1   | SI2  | SI3 | 0  |

## For the different cases possible, the signaling byte format at SIP is

Z...high impedance, X...don't care

# Signaling Byte

## Cases

- 1 One SICOFI is connected to one SLD port, EL = 0 (no signaling expansion logic provided); SA..SD are programmed as transmit signaling inputs.

- 2 One SICOFI connected to one SLD port, EL = 1 (signaling expansion logic provided); SA..SD are programmed as transmit signaling inputs.

- 3 One SICOFI is connected to one SLD port; EL = 0 (no signaling expansion logic provided); SA..SD are programmed as receive signaling outputs.

- 4 One SICOFI is connected to one SLD port; EL = 1 (signaling expansion logic provided); SA..SD are programmed as receive signaling outputs.

If a signaling expansion logic is provided (see case 2 and 4), the signaling bits SA..SD which are programmed as signaling inputs or outputs can be used as additional expansion bits in receive or transmit direction, respectively. As far as SICOFI is concerned, SIP is in a high-impedance (Z) state or "don't care" (Y) state while these bits are transfered.

- 5 Two SICOFIs are connected to one SLD port; SD is programmed as transmit signaling input.

- 6 Two SICOFIs are connected to one SLD port; SD is programmed as receive signaling output.

If two SICOFIs are connected to one SLD port, no signaling expansion logic is possible. SA is programmed as input automatically, and defines the addressed SICOFI:

$$SA = 0:A-SICOFI$$

$SA = 1:B-SICOFI.$

SB and SC are not usable with two SICOFIs on one SLD port.

## **Programming Procedure**

The following table shows some control byte sequences. If the SICOFI has to be configured completly during initialization, up to 60 bytes will be transfered.

| DIR Receiv                                                           | e Transr                 | nit Receiv               | ve Transm         | nit Receiv        | e Transm   | nit Receiv | e Transm | it Receiv  | e Transm   | it Receive | 1   |

|----------------------------------------------------------------------|--------------------------|--------------------------|-------------------|-------------------|------------|------------|----------|------------|------------|------------|-----|

| No Opera                                                             |                          | NOP                      | NOP               | NOP               | NOP        | NOP        | NOP      | NOP        | NOP        | NOP        | NOP |

| <b>SOP Write</b><br>LSEL = 00<br>LSEL = 11<br>LSEL = 10<br>LSEL = 01 | SOP<br>SOP<br>SOP<br>SOP | NOP<br>NOP<br>NOP<br>NOP | CR1<br>CR2<br>CR4 | NOP<br>NOP<br>NOP | CR1<br>CR3 | NOP<br>NOP | CR2      | NOP        | CR1        | NOP        |     |

| <b>SOP Read</b><br>LSEL = 00<br>LSEL = 11<br>LSEL = 10<br>LSEL = 01  | SOP<br>SOP<br>SOP<br>SOP | NOP<br>CR1<br>CR2<br>CR4 | X<br>X            | CR1<br>CR3        | ×          | CR2        | x        | CR1        |            |            |     |

| COP Write<br>4 Bytes<br>8 Bytes                                      | e<br>COP<br>COP          | NOP<br>NOP               | DB4<br>DB8        | NOP<br>NOP        | DB3<br>DB7 | NOP        | DB2      | NOP<br>NOP | DB1<br>DB1 | NOP<br>NOP |     |

| COP Read<br>4 Bytes<br>8 Bytes                                       | d<br>COP<br>COP          | DB4<br>DB8               | x<br>x            | DB3<br>DB7        |            | DB1<br>DB1 | X<br>X   | CR2<br>CR2 | x<br>x     | CR1<br>CR1 |     |

X .... don't care

DB1, DB2...DB8...coefficient Data Byte 1..8

## **Operating Modes**

#### **Basic Setting**

Upon initial application of  $V_{DD}$  or reseting pin RS to "1" while operating, the SICOFI enters a basic setting mode. Basic setting means, that the SICOFI configuration registers CR1...CR4 are initialized. All CR1 bits are set to "0" (all programmable filters are disabled except the B-Filter where fixed coefficients are used, no test mode); CR2 is set to "1" (SA...SD are inputs, signaling expansion logic is provided, one SICOFI on SLD-port, µ-law chosen and fixed B-Filter coefficients used). All CR3 and CR4 bits are reset to "0" (no additional amplification or attenuation, no linear mode, power down, no test mode). Receive signaling registers are cleared. SIP is in high-impedance state, the analog output  $V_{OUT}$  and the receive signaling outputs SO1...SO3 are forced to ground.

The serial interface is active to receive commands starting with the next 8-kHz SLD-bus frame. The serial interface port SIP remains tristate until CR2 has been defined.

If two SICOFIs are connected to one SLD port, both SICOFIs get the same SOP and CR2 information during initialization. The subsequent CR1 byte is assigned to the addressed SICOFI only. If the two SICOFIs need different CR2 information, the SOP-CR2 sequence has to be provided once again (each SICOFI knows its address now).

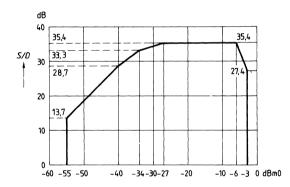

#### Standby Mode