| V |   |     |     |     |   |   |   |   |   |   |                               |

|---|---|-----|-----|-----|---|---|---|---|---|---|-------------------------------|

|   | T | ech | nol | ogy |   |   |   |   |   |   | <b>Communication Products</b> |

|   | • | ۲   |     | •   | • | • | • | • | • | • | Group                         |

|   | • | ۲   | •   | •   | • | • | • | • | • | • |                               |

|   | • | ۲   |     | •   | • | • | • | • | • | • | Data Sheet                    |

|   | • | ۲   |     | •   | • | • | • | • | • | • |                               |

|   | • | ۲   | •   | •   | • | • | • | • | • | • |                               |

|   | • | ۲   | •   | •   | • | • | • | • | • | • |                               |

|   | • | ۲   |     | •   | • | • | • | • | • | • |                               |

|   | • | ۲   |     | •   | • | • | • | • | • | • |                               |

|   | • | ۲   | •   | •   | • | • | • | • | • | • | ISDN                          |

|   | • | ۲   | •   | •   | • | • | • | • | • | • | VLSI's ISDN Processor         |

|   | • | ۲   |     | •   | • | • | • | • | • |   | (VIPem) VNS80000B             |

|   | • | •   |     | •   | • | • | • | • | • |   |                               |

|   | • | •   | •   | •   | • | • | • | • | • |   |                               |

|   | • | •   | •   | •   | • | • | • | • | • |   |                               |

|   | • |     |     | •   | • | • | • | • | • | • |                               |

|   |   | •   |     | •   | • | • | • | • | • |   |                               |

|   | • | •   |     |     |   |   |   |   |   |   | Version 2.5                   |

|   | • | •   |     | •   |   | • | • |   | • |   | Date: Sept. 97                |

|   | • | •   |     | •   | • | • | • | • | • | • |                               |

|   | • | ۲   |     | •   | • | • | • | • | • |   |                               |

|   | • | ۲   | •   | •   | • | • | • | • | • | • |                               |

|   | • | ۲   | •   | •   | • | • | • | • | • | • | VLSI                          |

|   | • | ٠   | •   | •   | ٠ | ٠ | ٠ | ٠ | • | • | VLSI<br>Proprietary           |

# **Table of Contents**

| 1. OVERVIEW                                             | 1  |

|---------------------------------------------------------|----|

| 1.1 Application                                         | 1  |

| 1.2 Key Features and Benefits                           |    |

| 2. FUNCTIONAL DESCRIPTION                               | 4  |

| 2.1 Function                                            | 4  |

| 2.2 Pin List                                            |    |

| 3. SUB-MODULE DESCRIPTION                               |    |

| 3.1 ARM CPU and SRAM                                    |    |

| 3.1.1 ARM                                               |    |

| 3.1.1.1 Thumb Concept                                   |    |

| 3.1.1.2 EmbeddedICE                                     |    |

| 3.1.2 SRAM                                              |    |

| 3.1.3 On Chip Boot Volume                               |    |

| 3.2 Memory Interface                                    |    |

| 3.3 Interrupt Controller                                |    |

| 3.4 S0 Interface                                        |    |

| 3.4.1 S0 Framer                                         |    |

| 3.4.2 D-Channel Controller                              |    |

| 3.4.2.1 Data flow of the outgoing D-channel information |    |

| 3.4.2.2 Data flow of the incoming D-channel information | 20 |

| 3.4.3 S0 Transmitter                                    |    |

| 3.4.4 S0 Receiver                                       |    |

| 3.4.5 Decoupling Inputs                                 |    |

| 3.5 Analogue Front End                                  |    |

| 3.5.1 Transmit Analogue Front End                       |    |

| 3.5.2 Receive Analogue Front End                        |    |

| 3.5.3 Reference Voltage                                 |    |

| 3.5.4 Data flow of the B-channel audio samples          |    |

| 3.6 Analogue Digital Converter                          | 26 |

| 3.7 UART                                                |    |

| 3.8 Serial DSP/CODEC Interface (SDCI)                   | 28 |

| 3.8.1 SDCI Master Mode                                  | 28 |

| 3.8.2 SDCI Slave Mode                                   | 29 |

| 3.8.3 SDO Pin                                           | 30 |

| 3.9 Key Pad                                             | 31 |

| 3.10 I/O Ports                                          | 32 |

| 3.11 Clock Oscillators and Watchdog                     | 33 |

| 3.12 LCD-Contrast Control                               |    |

| 3.13 Hardware Configuration                             | 34 |

| 4. REGISTER DESCRIPTION                                 | 35 |

| 4.1 Register Map                                        | 35 |

| 4.2 Register Description                                |    |

| 4.2.1 Memory Control Register (mcrReg)                  |    |

| 4.2.2 Watchdog Retrigger Register (wdogReg)             |    |

| 4.2.3 Timer and Interrupt Control Register (ticReg)     |    |

| 4.2.4 Fast Interrupt Acknowledge Register (fiarReg)     |    |

| 4.2.5 Normal Interrupt Acknowledge Register (niarReg)   |    |

This document contains information on a new product. Specifications and information herein are subjet to change without notice. © Copyright 1997 All trademarks referred in this document are the property of their respective owners

|                                                                                                       | 41 |

|-------------------------------------------------------------------------------------------------------|----|

| 4.2.6 XIN Oscillator Switch Control Register (xinocReg)                                               |    |

| 4.2.7 S0 DPLL Config. Reg. (configS0_Reg)                                                             |    |

| 4.2.7.1 S0 DPLL Config. Reg. (configS0_Reg) write<br>4.2.7.2 S0 DPLL Config. Reg. (configS0_Reg) read |    |

| 4.2.7.2 So DFLL Config. Reg. (configSo_Reg) read<br>4.2.8 SO Interrupt Register (intSo_Reg)           |    |

| 4.2.8 S0 Interrupt Register (intS0_Reg) Read                                                          |    |

| 4.2.8.2 S0 Interrupt Register (intS0_Reg) Write                                                       |    |

| 4.2.9 S0 DPLL Reset Register (resetS0_Reg) Write                                                      |    |

| 4.2.9 S0 DFLL Reset Register (TesetS0_Reg) write                                                      |    |

| 4.2.10 UART KATAData Register (UART_Reg)                                                              |    |

| 4.2.11 OANT Status Register (OART_statteg)                                                            |    |

| 4.2.12 D-channel TxData Register (D_TxReg)                                                            |    |

| 4.2.13 D-channel TxData Register (D_TXReg)                                                            |    |

| 4.2.14 S0 TxData Register (S0_TxReg)                                                                  |    |

| 4.2.16 ISDN Control Register (idcReg)                                                                 |    |

| 4.2.17 SDCI LSWord Rx/TxData Register (sdci_lswReg)                                                   |    |

| 4.2.17 SDCI LSWord Rx/TxData Register (sdci_nswReg)                                                   |    |

| 4.2.19 SDCI VijSWold KX/ TAData Register (sdci_niswReg)                                               |    |

| 4.2.19 SDC1 Control Register (suct_charleg)<br>4.2.20 VBAFE - Rx/TxData Reg. #1 (VBAFEpcm1Reg)        |    |

| 4.2.21 VBAFE Control Register (VBAFEReg)                                                              |    |

| 4.2.22 PIO1 Status Register (pio1_statReg)                                                            |    |

| 4.2.23 PIO1 Data1 Register (pio1_statteg)                                                             |    |

| 4.2.24 PIO1 Data0 Register (pio1_set0Reg)                                                             |    |

| 4.2.25 PIO2 Status Register (pio2_statReg)                                                            |    |

| 4.2.26 PIO2 Data1 Register (pio2_set1Reg)                                                             |    |

| 4.2.27 PIO2 Data1 Register (pio2_set0Reg)                                                             |    |

| 4.2.28 Key Pad Data Register (keypadReg)                                                              |    |

| 4.2.29 Clock Control Register (sysClockReg)                                                           |    |

| 4.2.29.1 Clock Control Register (sysClockReg) Write                                                   |    |

| 4.2.30 LCD Contrast Control Register (DAC_Reg)                                                        | 67 |

| 4.2.31 VBAFE - RxData Reg. #2 (VBAFEpcm2Reg)                                                          |    |

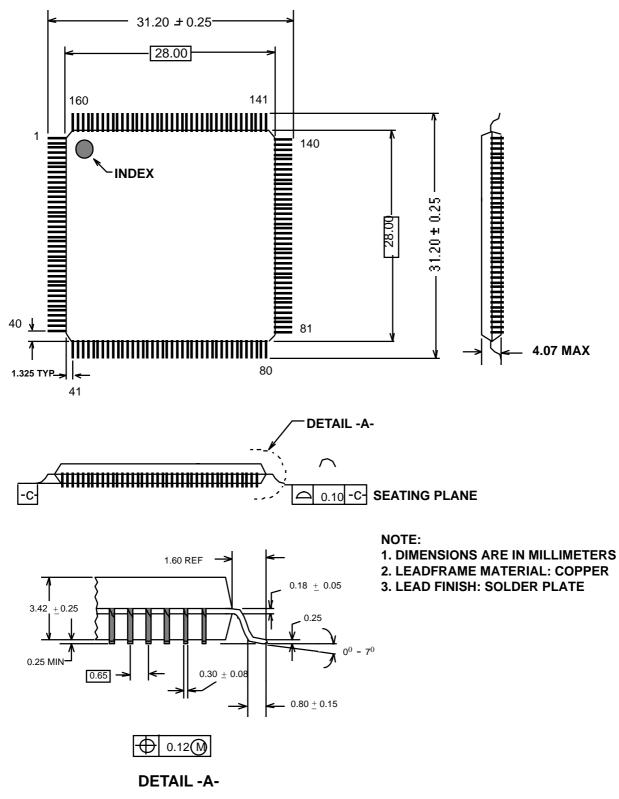

| 5. PHYSICAL PARAMETER                                                                                 |    |

|                                                                                                       |    |

| 5.1 Maximum Ratings                                                                                   |    |

| 5.2 Absolute Maximum Ratings                                                                          |    |

| 5.3 Operating Temperature Range                                                                       |    |

| 5.4 Package                                                                                           |    |

| 5.4.1 Package Outline                                                                                 |    |

| 5.5 Power Specification                                                                               |    |

| 5.6 S0 Interface                                                                                      |    |

| 5.6.1 SO Transmitter                                                                                  |    |

| 5.6.2 SO Receiver                                                                                     |    |

| 5.6.3 SO PLL                                                                                          |    |

| 5.7 VBAFE                                                                                             |    |

| 5.8 Ports                                                                                             |    |

| 5.8.1 DC Characteristic of the Digital I/O's                                                          |    |

| 5.8.2 AC Characteristic of the Digital I/O's                                                          |    |

| 5.8.3 Characteristic of the Analogue to Digital Converters                                            |    |

| 5.8.4 Characteristic of the Oscillators                                                               |    |

| 5.8.5 Characteristic of the Power-On Reset                                                            |    |

| 5.8.6 Characteristic of the LCD Contrast Control                                                      |    |

| 5.9 Memory Interface                                                                                  |    |

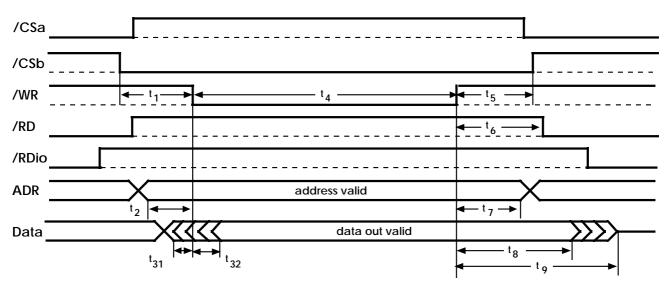

| 5.9.1 ROM/RAM Memory Single Write                                                                     |    |

This document contains information on a new product. Specifications and information herein are subjet to change without notice.© Copyright 1997 All trademarks referred in this document are the property of their respective owners VLSI PROPRIETARY

## VNS80000B - ISDN VIPem - VLSI's ISDN Processor Data Sheet

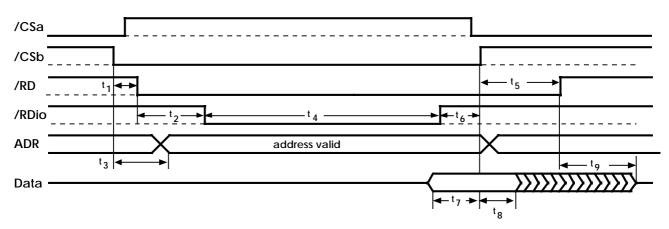

| 5.9.2 ROM/RAM Memory Single Read                     |    |

|------------------------------------------------------|----|

| 5.9.3 DRAM Write                                     |    |

| 5.9.4 DRAM Read                                      | 80 |

| 5.10 SDCI                                            | 81 |

| 6. DEVELOPMENT ENVIRONMENT                           | 82 |

| 6.1 Software Development Tools                       | 82 |

| 6.1.1 JumpStart                                      | 82 |

| 6.1.1.1 Contribution Software                        | 82 |

| 6.1.2 Operating Systems                              | 83 |

| 6.1.2.1 uC/OS                                        | 83 |

| 6.1.2.2 Accelerated Technology Nucleus/ Nucleus PLUS | 83 |

| 6.1.2.3 Helios Realtime Operating System             | 83 |

| 6.2 Development Platforms                            | 84 |

| 6.2.1 Evaluation System                              | 84 |

| 6.2.1.1 Documents                                    | 85 |

| 6.2.2 PID - Board                                    | 86 |

| 6.2.3 PIE - Board                                    | 86 |

| 6.3 On-Chip Debug                                    |    |

| 6.4 ISDN Software                                    | 89 |

| 7. TABLES AND FIGURES INDEX                          |    |

Version 2.5 Page iii

# Version History VIP P2 / VIPem

| Document<br>Version | Date | Changes                                                                                                                           |

|---------------------|------|-----------------------------------------------------------------------------------------------------------------------------------|

| 2.0                 |      | Specification of the VIP (P2) revised hardware.                                                                                   |

| 2.1                 |      | 1. Modified pin-out.                                                                                                              |

|                     |      | 2. Updated boot procedure.                                                                                                        |

|                     |      | 3. Minor editorial changes.                                                                                                       |

|                     |      | 4. Modified Power-On reset threshold.                                                                                             |

|                     |      | 5. Updated specification of the LCD contrast control driver.                                                                      |

| 2.2                 |      | 1. Updated registers map & register bit usage.                                                                                    |

|                     |      | 2. Updated I/O port multifunctional use.                                                                                          |

|                     |      | 3. Minor editorial changes.                                                                                                       |

|                     |      | For detailed description of the changes see the 'VIP Delta List $2.1 \rightarrow 2.2$ '.                                          |

| 2.21                |      | 1. Ported document to PC Word 7.0.                                                                                                |

|                     |      | 2. Corrected page numbers in register map.                                                                                        |

| 2.3                 |      | 1. Corrected description of PIO pins.                                                                                             |

|                     |      | 2. Added description of bit length variation.                                                                                     |

|                     |      | 3. Corrected the values for the capacitor of the decoupling inputs.                                                               |

|                     |      | 4. Changed table for ConfTest pins (just the style).                                                                              |

|                     |      | 5. Changed intS0_Reg bits [14:12].                                                                                                |

|                     |      | 6. Changed ConfigS0_Reg bits [23:22].                                                                                             |

|                     |      | 7. Changed resetS0_Reg bits [5,1].                                                                                                |

|                     |      | 8. Updated SDCI timing picture.                                                                                                   |

|                     |      | 9. Updated Errata List.                                                                                                           |

|                     |      | 10. Minor editorial changes.                                                                                                      |

| 2.4                 |      | 1. Added values for power specification.                                                                                          |

|                     |      | 2. Added 'Data flow of the incoming D-channel information'.                                                                       |

|                     |      | 3. Added 'Data flow of the outgoing D-channel information.                                                                        |

|                     |      | 4. Added 'Data flow of the B-channel audio samples'.                                                                              |

|                     |      | 5. Added table for DRAM configurations.                                                                                           |

|                     |      | <ol> <li>Added description for SDO pin.</li> <li>Changed G.711 (codec) to the correct expression 'VBAFE'.</li> </ol>              |

|                     |      | <ol> <li>Changed G.711 (codec) to the correct expression 'VBAFE'.</li> <li>Corrected t<sub>4</sub> for ROM/RAM timing.</li> </ol> |

|                     |      | <ol> <li>9. Corrected values for caps connected to CREF and REF</li> </ol>                                                        |

|                     |      | 10. Updated SDCI timing diagram, Removed 256 kHz and 4096 kHz SDCI                                                                |

|                     |      | frequencies.                                                                                                                      |

|                     |      | 11. Updated DRAM timing.                                                                                                          |

|                     |      | 12. Removed 'Transmitted bit length' from intS0Reg.                                                                               |

|                     |      | 13. Removed chapter 7 'VNS80000 Errata List'.                                                                                     |

|                     |      | 14. Removed chapter 8.1 'Specification History P1.                                                                                |

|                     |      | 15. Removed chapter 8.3 'Delta Specification P1-P2'.                                                                              |

|                     |      | 16. Minor editorial changes (incl. update of pictures for better reading).                                                        |

|                     |      |                                                                                                                                   |

2.5

1. Added text for start up in Hardware Configuration

This document contains information on a new product. Specifications and information herein are subjet to change without notice.® Copyright 1997 All trademarks referred in this document are the property of their respective owners

| Document<br>Version | Date | Changes                                                                                        |  |  |  |

|---------------------|------|------------------------------------------------------------------------------------------------|--|--|--|

|                     |      | <ol> <li>Added clock switch bit in VBAFEReg</li> <li>Added clock switch in features</li> </ol> |  |  |  |

|                     |      | <ol> <li>Added clock switch in chapter 'clock oscillators and watchdog'</li> </ol>             |  |  |  |

|                     |      | 5. Corrected values for S0 Receiver Ref and Cref                                               |  |  |  |

|                     |      | 6. Removed testS0_Reg                                                                          |  |  |  |

7. Minor editorial changes (incl. update of pictures for better reading).

# **1. OVERVIEW**

# 1.1 Application

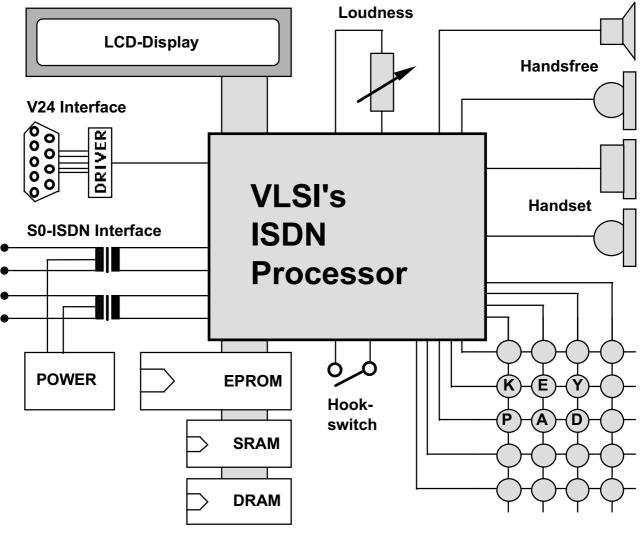

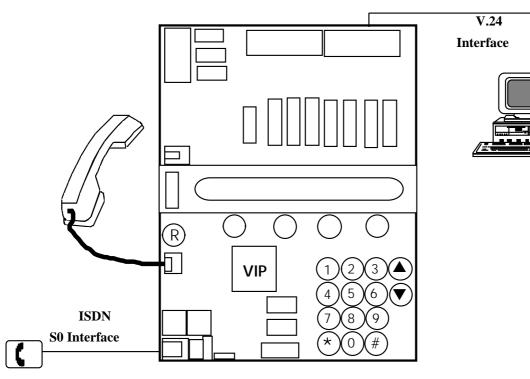

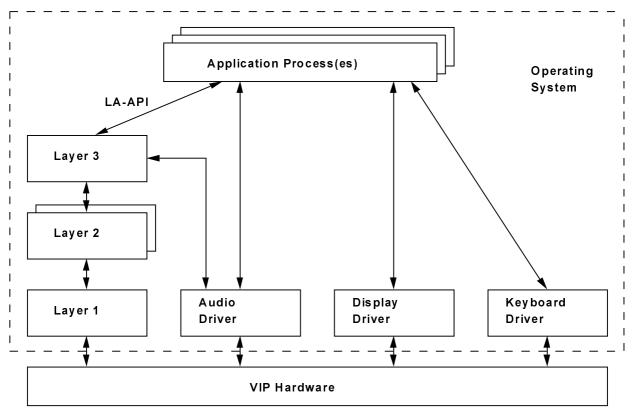

The VLSI's ISDN Processor (VIP) is a single chip ISDN subscriber circuit which includes most of the circuitry required to implement an ISDN terminal conforming to the Euro - ISDN standards (ETS 300 012, ETS 300 0125, ETS 300 102-1). A typical system configuration is shown below.

Figure 1-1: ISDN Telephone

Figure 1-1 shows the VIP in a typical terminal application. The S0 interface is active and in addition to the internal VBAFE (voice band analogue front end) an external CODEC is connected through the SDCI interface (Serial DSP/CODEC Interface). In this configuration the VIP is the master for the external CODEC.

This document contains information on a new product. Specifications and information herein are subjet to change without notice.© Copyright 1997 All trademarks referred in this document are the property of their respective owners VLSI PROPRIETARY VERSION 2.5 PAGE 1

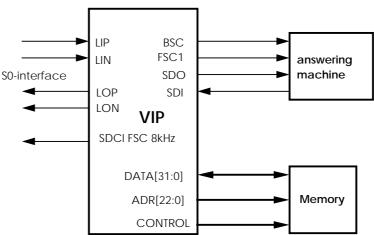

Figure 1-2: ISDN Terminal Application

Figure 1-2 shows the VIP in a PABX application. The timing for the SDCI interface is provide by the frame sync of the PCB highway. The S0 interface is also available.

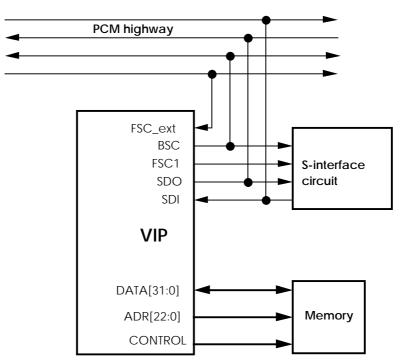

Figure 1-3: ISDN PABX Application

# 1.2 Key Features and Benefits

| Features                                                                                                                                                                                                                         | Benefits                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • Static 32-bit RISC controller with a 32-bit address-space running at 36.8 or 12.2 MHz (software controlled). Includes sophisticated debug features, instruction length 32- or 16-bit in a flexible memory-mapped architecture. | • Improves reliability, reduces system size and cost, very high performance, code efficiency, low power. Development tools available include C compiler, simulator and debugger. |

| <ul> <li>Internal 3k byte fast access general purpose<br/>SRAM (cache memory).</li> </ul>                                                                                                                                        | • Optimised execution of critical code.                                                                                                                                          |

| <ul><li>Internally programmable clock speed.</li><li>Programmable power-down feature with event</li></ul>                                                                                                                        | <ul><li>Power conservation, improved reliability.</li><li>Power conservation, improved reliability.</li></ul>                                                                    |

| <ul> <li>wake up.</li> <li>Supports 8/16/32-bit external SRAM/ ROM</li> </ul>                                                                                                                                                    | Maximises memory system performance and                                                                                                                                          |

| and 16/32-bit DRAM.                                                                                                                                                                                                              | utilisation.                                                                                                                                                                     |

| • Supports a range of memory speeds from 54 ns<br>- 1.2 us, with software programmable waitstate<br>generation.                                                                                                                  | • Maximises memory system performance and utilisation, minimises cost.                                                                                                           |

| • Interrupt controller, fully maskable for all peripherals.                                                                                                                                                                      | • Flexibility and efficiency interrupt processing.                                                                                                                               |

| • S0 interface containing analogue transceiver, data-clock recovery and framing.                                                                                                                                                 | • Direct connection to S0 bus via transformer.                                                                                                                                   |

| • D-channel data link controller with basic layer 2 function in hardware.                                                                                                                                                        | • Flexible system solution allowing easy implementation of either standard or proprietary protocols.                                                                             |

| • VBAFE complete with programmable analogue front end, additional input and output and power down modes capable of driving directly the ringer- and loudhearing speaker.                                                         | <ul> <li>Direct connection to telephone hand-set and<br/>provision for hands-free or speaker phone,<br/>reduced system component count.</li> </ul>                               |

| <ul> <li>Standard 64-bit serial DSP/CODEC interface.</li> </ul>                                                                                                                                                                  | • Allowing direct connection of up to three external devices like CODEC's, DSP's, etc.                                                                                           |

| On-Chip boot volume                                                                                                                                                                                                              | • Support of simple and effective program loading during production.                                                                                                             |

| Internal PCM format 14-bit linear.                                                                                                                                                                                               | Low distortion.                                                                                                                                                                  |

| • Two analogue to digital converters for volume control etc                                                                                                                                                                      | Reduced system component count.                                                                                                                                                  |

| • n x 6 keypad scanner which generates interrupts on key press.                                                                                                                                                                  | Reduced processor overhead.                                                                                                                                                      |

| <ul> <li>Buffered parallel LCD controller interface and<br/>LED drive via bi-directional programmable I/O<br/>ports.</li> </ul>                                                                                                  | Reduced system component count.                                                                                                                                                  |

| <ul> <li>Serial UART interface with baud rates from 1.2<br/>kBaud to 230.4 kBaud.</li> </ul>                                                                                                                                     | • Flexible product architecture through industry standard interface.                                                                                                             |

| • 2.5 ms timer.                                                                                                                                                                                                                  | Operating system clock and event timing.                                                                                                                                         |

| <ul><li>Powerful test architecture.</li><li>Packaged in 160 pin MQFP.</li></ul>                                                                                                                                                  | <ul> <li>High fault coverage.</li> <li>Easy to manufacture, inexpensive.</li> </ul>                                                                                              |

# 2. FUNCTIONAL DESCRIPTION

#### 2.1 Function

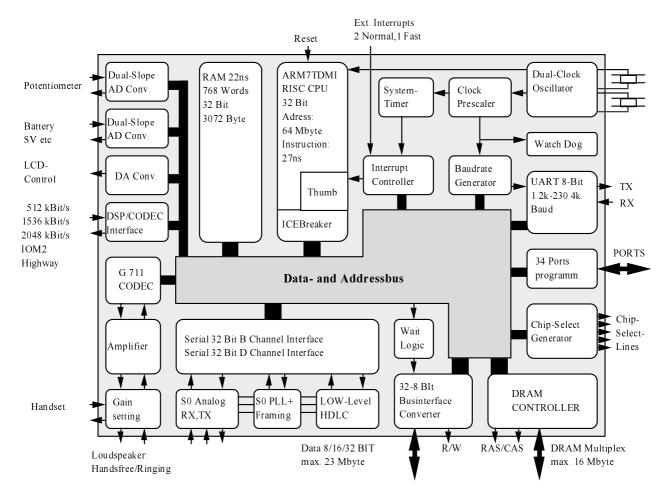

VLSI's ISDN Processor (VIP) provides a powerful programmable engine for ISDN subscriber communications. It combines a static 32-bit ARM7 RISC processor with a 16- or 32-bit instruction set including the embeddedICE (a on-chip debug facilities), a on-chip high speed memory, a S0 interface transceiver, a D-channel data link controller, a VBAFE, an industry standard serial interface (UART), a standard serial DSP/CODEC interface (SDCI), a keypad interface, interrupt controller and watchdog timer and power management features.

Figure 2-1: VIP Block Diagram

The on-chip S0 interface transceiver allows direct connection via a transformer and surge protection to the S0 bus. It contains all the basic Layer 1 functions such as data respectively clock recovery and framing. The D-channel data link controller provides most of the Layer 1 function and the basic Layer 2 frame formatting including zero-insertion/deletion, alarm condition detection, start-stop flag generation and detection. The remaining functions are easily performed by the powerful CPU.

The VBAFE contains an analogue front end that allows direct connection to the telephone hand-set. An additional input and output is provided for use in hands-free operation. This output is able to directly drive

This document contains information on a new product. Specifications and information herein are subjet to change without notice.<sup>©</sup> Copyright 1997 All trademarks referred in this document are the property of their respective owners

| VLSI PROPRIETARY |

|------------------|

| VERSION 2.5      |

| PAGE 4           |

the loudspeaker in hands-free mode operation or for ringing. Both inputs and outputs have independently programmable gains. All amplification stages have a programmable power-down mode.

A flexible power management controller enables to vary the programmable system clock speed. This allows optimised processor performance and power consumption minimisation. Both features are fully software configurable.

In addition to the above the VIP also contains 2 ADC (integrating, single slope) as well as a number of ports (bi-directional programmable) and a DAC e.g. to be used for LCD contrast control.

| VERSION 2.5 |

|-------------|

| PAGE 5      |

## 2.2 Pin List

| Pin # | Signal Name | Туре    | Function             |

|-------|-------------|---------|----------------------|

| 1     | VDD         | Supply  | Digital power supply |

| 2     | VSS         | Ground  | Digital ground       |

| 3     | ADR[15]     | Output  | Address [15]         |

| 4     | ADR[14]     | Output  | Address [14]         |

| 5     | ADR[12]     | Output  | Address [12]         |

| 6     | ADR[13]     | Output  | Address [13]         |

| 7     | ADR[7]      | Output  | Address [7]          |

| 8     | ADR[8]      | Output  | Address [8]          |

| 9     | ADR[6]      | Output  | Address [6]          |

| 10    | ADR[9]      | Output  | Address [9]          |

| 11    | VDD         | Supply  | Digital power supply |

| 12    | VSS         | Ground  | Digital ground       |

| 13    | ADR[5]      | Output  | Address [5]          |

| 14    | ADR[11]     | Output  | Address [11]         |

| 15    | ADR[4]      | Output  | Address [4]          |

| 16    | ADR[3]      | Output  | Address [3]          |

| 17    | ADR[10]     | Output  | Address [10]         |

| 18    | ADR[2]      | Output  | Address [2]          |

| 19    | ADR[1]      | Output  | Address [1]          |

| 20    | ADR[0]      | Output  | Address [0]          |

| 21    | VDD         | Supply  | Digital power supply |

| 22    | VSS         | Ground  | Digital ground       |

| 23    | D[7]        | Bidirec | Data[7]              |

| 24    | D[6]        | Bidirec | Data[6]              |

| 25    | D[0]        | Bidirec | Data[0]              |

| 26    | D[5]        | Bidirec | Data[5]              |

| 27    | D[1]        | Bidirec | Data[1]              |

| 28    | D[4]        | Bidirec | Data[4]              |

| 29    | D[2]        | Bidirec | Data[2]              |

| 30    | D[3]        | Bidirec | Data[3]              |

| 31    | VDD         | Supply  | Digital power supply |

| 32    | VSS         | Ground  | Digital ground       |

| 33    | D[8]        | Bidirec | Data[8]              |

| 34    | D[9]        | Bidirec | Data[9]              |

| 35    | D[10]       | Bidirec | Data[10]             |

| 36    | D[11]       | Bidirec | Data[11]             |

| 37    | D[12]       | Bidirec | Data[12]             |

| 38    | D[13]       | Bidirec | Data[13]             |

| 39    | D[14]       | Bidirec | Data[14]             |

| 40    | D[15]       | Bidirec | Data[15]             |

This document contains information on a new product. Specifications and information herein are subjet to change without notice.© Copyright 1997 All trademarks referred in this document are the property of their respective owners VLSI PROPRIETARY

VLSI PROPRIETARY VERSION 2.5 PAGE 6

| Pin # | Signal Name | Туре     | Function                             |

|-------|-------------|----------|--------------------------------------|

| 41    | VDD         | Supply   | Digital power supply                 |

| 42    | VSS         | Ground   | Digital ground                       |

| 43    | Xin         | Analogue | Quartz for the 36.864 MHz oscillator |

| 44    | Xout        | Analogue | Quartz for the 36.864 MHz oscillator |

| 45    | VDD         | Supply   | Digital power supply                 |

| 46    | VSS         | Ground   | Digital ground                       |

| 47    | XinLP       | Analogue | Quartz for the 460 kHz oscillator    |

| 48    | XoutLP      | Analogue | Quartz for the 460 kHz oscillator    |

| 49    | UART_SIN    | Input    | Serial data in of the UART           |

| 50    | UART_SOUT   | Output   | Serial data out of the UART          |

| 51    | PIO2[7]     | Bidirec  | I/O port2 [7]                        |

| 52    | PIO2[6]     | Bidirec  | I/O port2 [6]                        |

| 53    | PIO2[5]     | Bidirec  | I/O port2 [5]                        |

| 54    | PIO2[4]     | Bidirec  | I/O port2 [4]                        |

| 55    | PIO2[3]     | Bidirec  | I/O port2 [3]                        |

| 56    | PIO2[2]     | Bidirec  | I/O port2 [2]                        |

| 57    | PIO2[1]     | Bidirec  | I/O port2 [1]                        |

| 58    | PIO2[0]     | Bidirec  | I/O port2 [0]                        |

| 59    | VDD         | Supply   | Digital power supply                 |

| 60    | VSS         | Ground   | Digital ground                       |

| 61    | PIO1[22]    | Bidirec  | I/O port1 [22]                       |

| 62    | PIO1[21]    | Bidirec  | I/O port1 [21]                       |

| 63    | PIO1[20]    | Bidirec  | I/O port1 [20]                       |

| 64    | PIO1[19]    | Bidirec  | I/O port1 [19]                       |

| 65    | PIO1[18]    | Bidirec  | I/O port1 [18]                       |

| 66    | PIO1[17]    | Bidirec  | I/O Port1 [17]                       |

| 67    | PIO1[16]    | Bidirec  | I/O port1 [16]                       |

| 68    | VDD         | Supply   | Digital power supply                 |

| 69    | VSS         | Ground   | Digital ground                       |

| 70    | PIO1[15]    | Bidirec  | I/O port1 [15]                       |

| 71    | PIO1[14]    | Bidirec  | I/O port1 [14]                       |

| 72    | PIO1[13]    | Bidirec  | I/O port1 [13]                       |

| 73    | PIO1[12]    | Bidirec  | I/O port1 [12]                       |

| 74    | PIO1[11]    | Bidirec  | I/O port1 [11]                       |

| 75    | PIO1[10]    | Bidirec  | I/O port1 [10]                       |

| 76    | PIO1[9]     | Bidirec  | I/O port1 [9]                        |

| 77    | PIO1[8]     | Bidirec  | I/O port1 [8]                        |

| 78    | VDD         | Supply   | Digital power supply                 |

| 79    | VSS         | Ground   | Digital ground                       |

| 80    | PIO1[7]     | Bidirec  | I/O port1 [7]                        |

| Pin # | Signal Name | Туре     | Function                                                              |

|-------|-------------|----------|-----------------------------------------------------------------------|

| 81    | PIO1[6]     | Bidirec  | I/O port1 [6]                                                         |

| 82    | PIO1[5]     | Bidirec  | I/O port1 [5]                                                         |

| 83    | PIO1[4]     | Bidirec  | I/O port1 [4]                                                         |

| 84    | PIO1[3]     | Bidirec  | I/O port1 [3]                                                         |

| 85    | PIO1[2]     | Bidirec  | I/O port1 [2]                                                         |

| 86    | PIO1[1]     | Bidirec  | I/O Port1 [1]                                                         |

| 87    | PIO1[0]     | Bidirec  | I/O port1 [0]                                                         |

| 88    | VDD         | Supply   | Digital power supply                                                  |

| 89    | VSS         | Ground   | Digital ground                                                        |

| 90    | VSS_AMP_LS  | Ground   | Ground for the analogue front end                                     |

| 91    | PwoLSn      | Analogue | Loudspeaker output                                                    |

| 92    | VDD_AMP_LS  | Supply   | Supply for the analogue front end                                     |

| 93    | PwoLSp      | Analogue | Loudspeaker output                                                    |

| 94    | VSS_AMP_HS  | Ground   | Ground for the analogue front end                                     |

| 95    | PwoHSn      | Analogue | Handset earpiece output                                               |

| 96    | VDD_AMP_HS  | Analogue | Supply for the analogue front end                                     |

| 97    | PwoHSp      | Analogue | Handset earpiece output                                               |

| 98    | PIO2[8]     | Bidirec  | I/O port2 [8]                                                         |

| 99    | PIO2[9]     | Bidirec  | I/O port2 [9]                                                         |

| 100   | PIO2[10]    | Output   | LCD contrast control                                                  |

| 101   | VDD         | Supply   | Digital power supply                                                  |

| 102   | VSS         | Ground   | Digital ground                                                        |

| 103   | KEYin[6]    | Input    | Keypad column line[6]                                                 |

| 104   | KEYin[5]    | Input    | Keypad column line[5]                                                 |

| 105   | KEYin[4]    | Input    | Keypad column line[4]                                                 |

| 106   | KEYin[3]    | Input    | Keypad column line[3]                                                 |

| 107   | KEYin[2]    | Input    | Keypad column line[2]                                                 |

| 108   | KEYin[1]    | Input    | Keypad column line[1]                                                 |

| 109   | ConfTest[1] | Input    | hardware configuration signal[1]                                      |

| 110   | ConfTest[2] | Input    | hardware configuration signal[2]                                      |

| 111   | ConfTest[3] | Input    | hardware configuration signal[3]                                      |

| 112   | ConfTest[4] | Input    | hardware configuration signal[4]                                      |

| 113   | ConfTest[5] | Input    | hardware configuration signal[5]                                      |

| 114   | Vrefn       | Analogue | Test and de-coupling PIN for the AFE analogue front<br>end            |

| 115   | Vrefp       | Analogue | Test and de-coupling PIN for the analogue front end reference voltage |

| 116   | Auxin       | Analogue | Hands-free microphone input                                           |

| 117   | Auxip       | Analogue | Hands-free microphone input                                           |

| 118   | Vxin        | Analogue | Hand-set microphone input                                             |

| 119   | Vxip        | Analogue | Hand-set microphone input                                             |

| 120   | VDD_AVD     | Supply   | Supply for the analogue front end                                     |

| Pin # | Signal Name | Туре     | Function                              |

|-------|-------------|----------|---------------------------------------|

| 121   | VSS_AVS     | Ground   | Ground for the analogue front end     |

| 122   | ADC1in      | Analogue | Analogue digital converter #1 input   |

| 123   | ADC2in      | Analogue | Analogue digital converter #2 input   |

| 124   | VSS_AVS     | Ground   | Ground for the analogue front end     |

| 125   | LIP         | Analogue | S0 positive input signal              |

| 126   | LIN         | Analogue | S0 negative input signal              |

| 127   | Cref        | Analogue | Decoupling capacitor #1               |

| 128   | Ref         | Analogue | Decoupling capacitor #2               |

| 129   | VSS_AVS_S0  | Ground   | Ground for the S0 receiver            |

| 130   | VDD_AVD_S0  | Supply   | Power supply for the S0 receiver      |

| 131   | GND         | NC       | Not connected                         |

| 132   | GND         | NC       | Not connected                         |

| 133   | VSS         | Ground   | Digital ground                        |

| 134   | LON         | Output   | SO negative output signal, open drain |

| 135   | LOP         | Output   | SO positive output signal, open drain |

| 136   | GND         | NC       | Not connected                         |

| 137   | GND         | NC       | Not connected                         |

| 138   | VDD         | Supply   | Digital power supply                  |

| 139   | VSS         | Ground   | Digital ground                        |

| 140   | Reset       | Input    | Reset, active low                     |

| 141   | FSC1        | Output   | Frames Sync 1 of the SDCI interface   |

| 142   | BSCK        | Bidirec  | Bit clock of the SDCI interface       |

| 143   | SDO         | Output   | Serial data out of the SDCI interface |

| 144   | SDI         | Input    | Serial data in of the SDCI interface  |

| 145   | VDD         | Supply   | Digital power supply                  |

| 146   | VSS         | Ground   | Digital ground                        |

| 147   | /WR0        | Output   | Memory write #0                       |

| 148   | /WR1        | Output   | Memory write #1                       |

| 149   | /RDio       | Output   | I/O read spike free                   |

| 150   | /RD         | Output   | Memory read                           |

| 151   | /CS16boot   | Output   | Chip select for 16-bit boot-EPROM     |

| 152   | /CS8        | Output   | Chip select for 8-bit EPROM           |

| 153   | /CS8boot    | Output   | Chip select for 8-bit boot-EPROM      |

| 154   | VDD         | Supply   | Digital power supply                  |

| 155   | VSS         | Ground   | Digital ground                        |

| 156   | ADR[20]     | Output   | Address [20]                          |

| 157   | ADR[19]     | Output   | Address [19]                          |

| 158   | ADR[18]     | Output   | Address [18]                          |

| 159   | ADR[17]     | Output   | Address [17]                          |

| 160   | ADR[16]     | Output   | Address [16]                          |

Table 2-1: PIN List

# 3. SUB-MODULE DESCRIPTION

### 3.1 ARM CPU and SRAM

#### 3.1.1 ARM

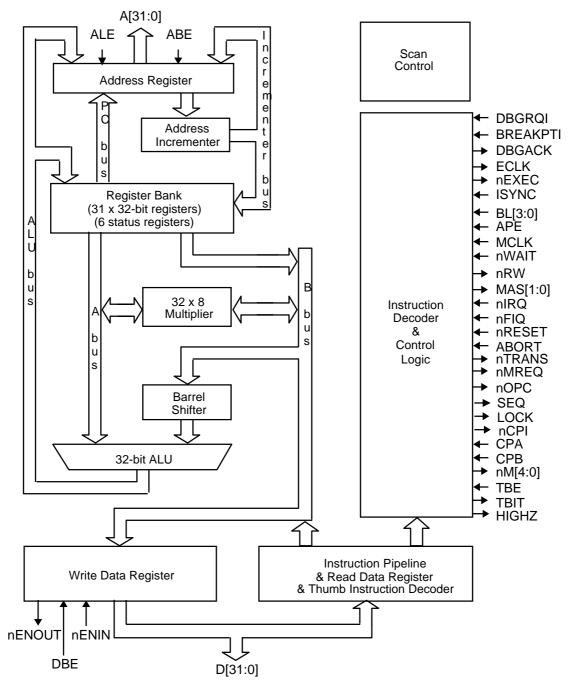

The ARM7TDMI is a member of the Advanced RISC Machines (ARM) family of general purpose 32-bit microprocessors, which offer high performance for very low power consumption and size.

The ARM architecture is based on Reduced Instruction Set Computer (RISC) principles, and the instruction set and related decode mechanism are much simpler than those of microprogrammed Complex Instruction Set Computers (CISC). This simplicity results in a high instruction throughput and impressive real-time interrupt response from a small and cost-effective chip.

Pipelining is employed so that all parts of the processing and memory systems can operate continuously. Typically, while one instruction is being executed, its successor is being decoded, and a third instruction is being fetched from memory.

The memory interface has been designed to allow the performance potential to be realised without incurring high costs in the memory system. Speed-critical control signals are pipelined to allow system control functions to be implemented in standard low-power logic, and these control signals facilitate the exploitation of the fast local access modes offered by industry standard dynamic RAMs.

PAGE 10

Figure 3-1: ARM Block Diagram

## 3.1.1.1 Thumb Concept

The ARM7TDMI processor employs a unique architectural strategy known as THUMB, which makes it ideally suited to high-volume applications with memory restrictions, or applications where code density is an issue. The key idea behind THUMB is that of a super-reduced instruction set. Essentially, the ARM7TDMI processor has two instruction sets:

- the standard 32-bit ARM set

- a 16-bit THUMB set

The THUMB set's 16-bit instruction length allows it to approach twice the density of standard ARM code while retaining most of the ARM's performance advantage over a traditional 16-bit processor using 16-bit registers. This is possible because THUMB code operates on the same 32-bit register set as ARM code.

THUMB code is able to provide up to 65% of the code size of ARM, and 160% of the performance of an equivalent ARM processor connected to a 16-bit memory system.

THUMB instructions operate with the standard ARM register configuration, allowing excellent interoperability between ARM and THUMB states. Each 16-bit THUMB instruction has a corresponding 32-bit ARM instruction with the same effect on the processor model.

The major advantage of a 32-bit (ARM) architecture over a 16-bit architecture is its ability to manipulate 32bit integers with single instructions, and to address a large address space efficiently. When processing 32-bit data, a 16-bit architecture will take at least two instructions to perform the same task as a single ARM instruction.

However, not all the code in a program will process 32-bit data (for example, code that performs character string handling), and some instructions, like branches, do not process any data at all.

If a 16-bit architecture only has 16-bit instructions, and a 32-bit architecture only has 32-bit instructions, then overall the 16-bit architecture will have better code density, and better than one half the performance of the 32-bit architecture. Clearly 32-bit performance comes at the cost of code density.

THUMB breaks this constraint by implementing a 16-bit instruction length on a 32-bit architecture, making the processing of 32-bit data efficient with a compact instruction coding. This provides far better performance than a 16-bit architecture, with better code density than a 32-bit architecture.

THUMB also has a major advantage over other 32-bit architectures with 16-bit instructions. This is the ability to switch back to full ARM code and execute at full speed. Thus critical loops for applications such as

- fast interrupts

- DSP algorithms

can be coded using the full ARM instruction set, and linked with THUMB code. The overhead of switching from THUMB code to ARM code is folded into sub-routine entry time. Various portions of a system can be optimised for speed or for code density by switching between THUMB and ARM execution as appropriate.

## 3.1.1.2 EmbeddedICE

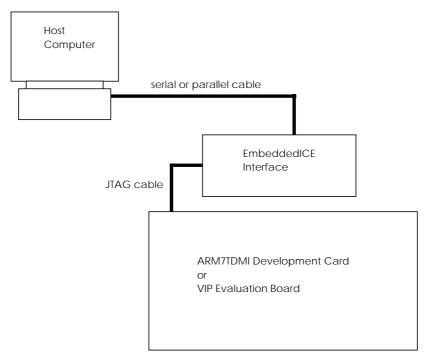

ARM7TDMI contains hardware extensions for advanced debugging features. These are intended to ease the user's development of application software, operating systems, and the hardware itself.

The debug extensions allow the core to be stopped either on a given instruction fetch (breakpoint) or data access (watchpoint), or asynchronously by a debug-request. When this happens, ARM7TDMI is said to be in debug state. At this point, the core's internal state and the system's external state may be examined. Once examination is complete, the core and system state may be restored and program execution resumed.

ARM7TDMI is forced into debug state either by a request on one of the external debug interface signals, or by an internal functional unit known as embeddedICE. Once in debug state, the core isolates itself from the memory system. The core can then be examined while all other system activity continues as normal.

ARM7TDMI's internal state is examined via a JTAG-style serial interface, which allows instructions to be serially inserted into the core's pipeline without using the external data bus. Thus, when in debug state, a store-multiple (STM) could be inserted into the instruction pipeline and this would dump the contents of ARM7TDMI's registers. This data can be serially shifted out without affecting the rest of the system.

The ARM7TDMI-ICEbreaker module, provides integrated on-chip debug support for the ARM7TDMI core. ICEbreaker is programmed in a serial fashion using the ARM7TDMI TAP (Test Access Port) controller. It consists of two real-time watchpoint units, together with a control and status register. One or both of the watchpoint units can be programmed to halt the execution of instructions by the ARM7TDMI core via its BREAKPT signal. Execution is halted when a match occurs between the values programmed into ICEbreaker and the values currently appearing on the address bus, data bus and various control signals. Any bit can be masked so that its value does not affect the comparison.

Either watchpoint unit can be configured to be a watchpoint (monitoring data accesses) or a breakpoint (monitoring instruction fetches). Watchpoints and breakpoints can be made to be data-dependent.

PAGE 13

## 3.1.2 SRAM

The integrated high speed static RAM with a capacity of 3 kBytes is organised as 768 32-bit words. Read operations are executed without any wait states. Write operations on the other hand require a wait state; the access time is 27 ns. This memory is used for time- or performance-critical code only (e.g. fast interrupt execution or DSP like operations).

#### 3.1.3 On Chip Boot Volume

To simplify the production process of VIP based products an on chip boot volume has been implemented. This boot volume supports the individualisation of Flash-EPROM's during the production process. After a watch dog retrigger the boot volume procedure expect data to be loaded via the UART. These bytes get stored into the internal SRAM starting at address 0x100. After receiving 1796 (0x704) bytes the code at address 0x100 will be executed.

On activation of the on chip boot volume procedure by the hardware configuration pins ConfTest[5:1] the following process get started:

- Power up reset / watch-dog retrigger

- ♦ UART send '@'

- UART expect line feed character (0x0A)

- UART expect data

- Data from the UART will be loaded into the internal SRAM starting at address 100 hex

- After receiving of 1796 (0x704) bytes address 256 (0x100) will be executed

For the communication between the VIP and the host the following settings are used:

- 9600 baud

- 8 bit, no parity, 1 stop bit, no protocol or handshake

The watchdog is set to 2.56 sec. To send the 0x704 bytes at 9600 baud will take at least 1.9s.

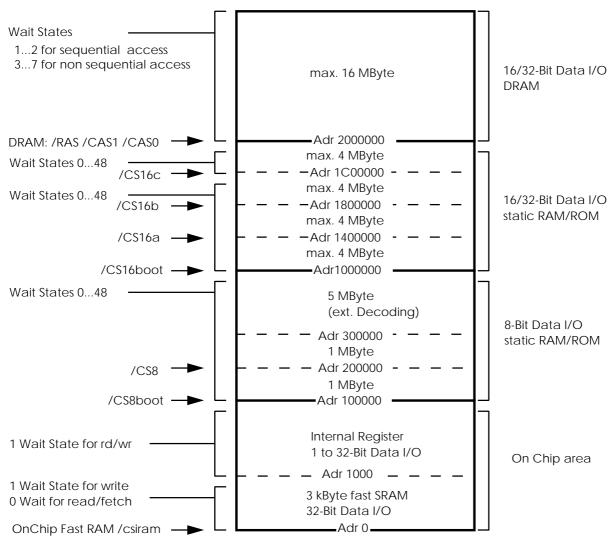

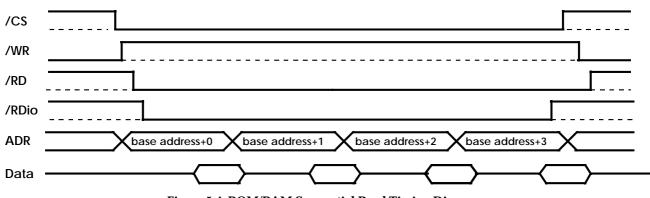

#### 3.2 Memory Interface

The memory interface allows the connection of 8-, 16- or 32-bit static RAM/ROM and 16-bit or 32-bit DRAMs. There is always a 8-bit memory area (starting 0x100000). For the upper memory area (starting 0x1000000) it can be selected by the ConfTest pins weather 16- or 32-bit access is used.

Write access to the internal memory and the registers is only 32 bit wide possible.

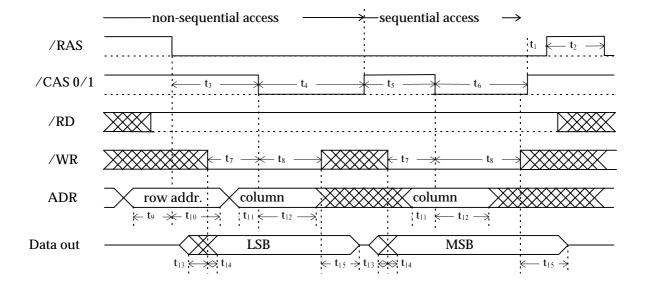

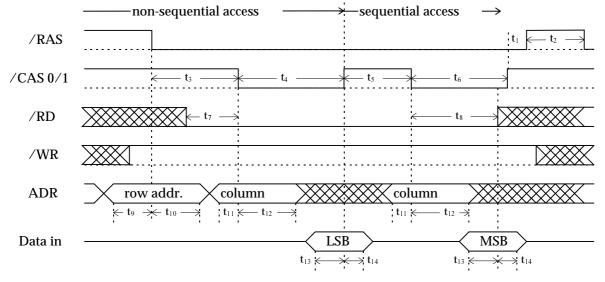

23 Mbytes static RAM/ROM and 16 Mbytes dynamic RAM are accessible. In each of the four ranges, the wait states are programmable in sixteen steps, ranging from one to 48 wait states. After reset the wait state count ten respectively 298.3 ns is used. The DRAM timing controller supports both non sequential and fast page mode DRAM access.

The addressing range associated with the CS lines is fixed.

| Name      | Function                              | Comment                           |

|-----------|---------------------------------------|-----------------------------------|

| A[20:0]   | Address lines                         | Output                            |

| A[21]     | Address line                          | Output or programmable I/O port   |

| A[22]     | Address line                          | Output or programmable I/O port   |

| D[15:0]   | Data lines                            | Bidirec.                          |

| D[31:16]  | Data lines                            | Bidirec. or programmable I/O port |

| /RAS      | DRAM row address select               | Output or programmable I/O port   |

| /CAS0     | DRAM select #0                        | Output or programmable I/O port   |

| /CAS1     | DRAM select #1                        | Output or programmable I/O port   |

| /RD       | Memory read                           | Output                            |

| /RDio     | I/O read                              | Output, spike free I/O read       |

| /WR0      | Memory write # 0 select               | Output                            |

| /WR1      | Memory write # 1 select               | Output                            |

| /CS8boot  | Chip select for 8-bit boot-EPROM      | Output                            |

| /CS8      | Chip select for 8-bit EPROM/SRAM      | Output                            |

| /CS16boot | Chip select for 16/32-bit boot-EPROM  | Output                            |

| /CS16a    | Chip select for 16/32-bit ROM/SRAM *) | Output or programmable I/O port   |

| /CS16b    | Chip select for 16/32-bit ROM/SRAM *) | Output or programmable I/O port   |

| /CS16C    | Chip select for 16/32-bit ROM/SRAM*)  | Output or programmable I/O port   |

#### **Table 3-1: Memory Signals**

\*) Using 2(4) 8-bit RAMs for the 16(32)-bit memory area:

This configuration allows 32-bit (STR), 16-bit (STRH) or 8-bit (STRB) write accesses to the memory. As it cannot determined which type of access is used by the C-compiler (e.g. to write variables of type 'char'), this seems to be the safest approach to build RAM, which can be byte-wide accessed. WR0 is used to strobe data in the even addresses of the memory, WR1 for odd addresses.

For 32-bit wide memory, build of 8 bit RAMs, external logic is necessary.

Using 16(32)-bit RAM in the 16(32)-bit memory area:

In this configuration, no byte write accesses is supported, unless special RAMs employed with several special chip select signals for byte access are used. For 32-bit memory, it is even not possible to write 16-bit words only. During such an accesses, always the full word is written determined by the strobe signal WR0. The content of the memory which should be retained (e.g. 24-bit in case of an 8-bit write access to 32-bit memory) is destroyed.

The boot location is selectable by pin strapping for further details see chapter 'Hardware Configuration'. A write enable decoder separates byte from word writing. 9 chip select signals together with fully decoded address ranges for RAM, ROM and I/O usage provide high flexibility.

RAS and CAS signals are generated. The address multiplexed minimal system has a software refresh. DRAM's with 256 k to 4 M address organisation are supported. Square ROW/CAS-Address from nine to eleven bits are supported. For further details see chapter 'DRAM Write' at page 79.

Figure 3-2 shows the resulting memory map.

Figure 3-2: Memory Map

|                     | used addresses | 16 bit wide access | 32 bit wide access  |

|---------------------|----------------|--------------------|---------------------|

| 2* 9 address lines  | 256 k          | 512 kByte = 4 MBit | 1 MByte = 8 MBit    |

| 2* 10 address lines | 1 M            | 2 MByte = 16 MBit  | 4 MByte = 32 MBit   |

| 2* 11 address lines | 4 M            | 8 Mbyte = 64 MBit  | 16 MByte = 128 MBit |

Table 3-2 : Possible DRAM configurations

This document contains information on a new product. Specifications and information herein are subjet to change without notice.<sup>©</sup> Copyright 1997 All trademarks referred in this document are the property of their respective owners

V

| LSI PROPRIETARY        |

|------------------------|

| VERSION 2.5            |

| <b>P</b> AGE <b>16</b> |

## 3.3 Interrupt Controller

External and internal interrupt signals are detected and can be read from the internal status register of the interrupt controller. The interrupt controller has two independent interrupt levels. One interrupt level is for the ARM7 fast interrupt and the other interrupt level is for the ARM7 normal interrupt.

The fast interrupt controller has seven interrupt sources. The latency time for these interrupts is about 1 us. All fast interrupts are maskable. The fast interrupts are latched.

The normal interrupt controller has fourteen interrupt sources which are all maskable. The normal interrupts are latched. The latency of the normal interrupts depend on the size of the fast interrupt routine (i.e. the time that this routine uses).

## 3.4 S0 Interface

#### 3.4.1 S0 Framer

Two 26-bit parallel full duplex data register are the interface between the internal data bus and the analogue S0 front end. All bits in the S0 frame are accessible. Automatic frame generation and detection including insertion and deletion of the DC balancing bits is performed.

The DPLL driven by the zero crossing detector of the receiver generates the bit and frame clocks, with low output jitter and a search mode for quick synchronisation.

#### 3.4.2 D-Channel Controller

The D-channel controller performs the D1-, D2- and Echo bit processing (see S0 Data Register). A low level HDLC processor does the Layer2 frame generation for the D-channel including start- and stop flag generation and detection, zero insertion and deletion.

Using the powerful ARM CPU, all processing and generation of the data octets between the start- and stop flags- including the frame check sequence - can be performed in software. The data transfer between CPU and D-channel controller is done via a full duplex 4-byte deep FIFO.

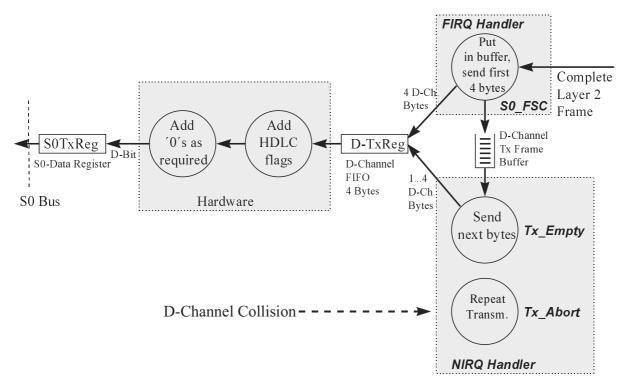

3.4.2.1 Data flow of the outgoing D-channel information

The following description assumes a software structure that is based on the OSI layer model, where layer 1 is the physical layer and layer 2 is the data link layer. The D-channel controller is activated in the idcReg.

Layer 2 of the software requests a D-channel frame to be sent. This request has to be handled in the Fast Interrupt (FIRQ) Handler. The FIRQ handler has to check the number of consecutive 1 received in the D-channel. This number can be read from the configS0\_Reg [23:20]. If the D-channel is available the FIRQ handler can write the first 4 bytes to the D\_TxReg and store the remaining bytes in a software fifo. To start the D-channel transmission the idcReg has to be set accordingly.

The data in the D\_TxReg will then be processed by the hardware. The opening and closing flag are added and the '0' insertion is done as required in the LAP-D protocol. Then these bits are placed in the D-channel bits in the S0\_TxDataReg. Then this half frame is automatically transmitted.

When the first 4 bytes are transmitted the normal interrupt 'D-channel TxEmpty' is issued and the next bytes from the software fifo can be written to the D\_TxReg. If the last bytes of the message are to be send the number of bytes has to be set accordingly in the idcReg. The closing flag will be generated by the hardware.

A normal interrupt 'D-channel TxCompl' indicates that the last byte of the layer 2 frame has been sent.

If a collision occurs on the D-channel the normal interrupt 'D-channel TxAbort' is issued by the VIP and the D-channel transmission is stopped immediately by the hardware. The retransmission of the frame has to be handled by the software.

### Figure 3-3 : D-channel Tx flow

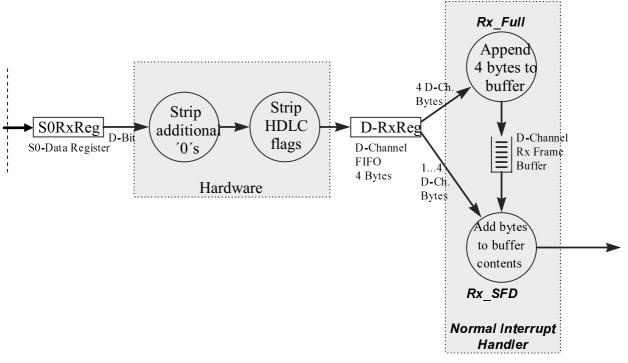

3.4.2.2 Data flow of the incoming D-channel information

If the D-channel controller is activated in the idcReg the D-channel bits received in the S0 frame are extracted automatically. The '0' deletion is done and the flags are stripped. The received bytes are then stored in the D\_RxReg. When 4 complete bytes were received a 'D-channel RxFull' interrupt is generated and the D-channel bytes can be read from the D\_RxReg.

When a closing flag was detected by the hardware a 'D-channel RxSFD' interrupt is issued. The remaining data bytes are stored in the D\_RxReg. The number of valid bits can be read from the idcReg. The D-channel frame has been received completely and can be sent to the layer 2 software.

Figure 3-4 D-channel Rx flow

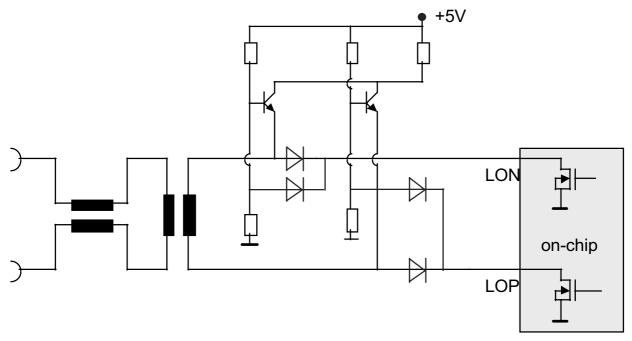

# 3.4.3 S0 Transmitter

Features

- Pulse shaping to fit template with nominal loading (200  $\Omega$  on the driver side)

- Pulse shaping to fit template with 400 W load (or 1600 W on the driver side)

- The line driver is coupled to a standard (2:2):(1:1) transformer

- Meets I.430 layer 1 specification

- Current limiting capability

- Supports short passive bus, extended passive bus and point-to-point systems

The line driver in conjunction with the transformer and the external components (see Figure 3-5) generates controlled positive and negative pulses. A 12.288 MHz clock \*) is used for pulse shaping. When driving a pulse, the driver can be modelled as a current source. The nominal value of current is 7.5 mA. Therefore the pulse amplitude is precisely controlled and the nominal level at the line driver output is  $\pm 1.5$  V and  $\pm 750$  mV at the transformer outputs with a 50  $\Omega$  load.

\*) this frequency is derived from the 36.864 MHz oscillator.

Special care has been taken to minimise the influence of the driver on the zero-crossing detector. The receiver can attain zero crossing sensitivity better than  $\pm 10$  mV whilst the driver is driving a +/1.5 V pulse. This requires a decoupling of nearly 40 dB, and is accomplished by careful layout isolation, use of pseudo-differential structures and by using separate supply pads.

Figure 3-5: S0 Transmitter

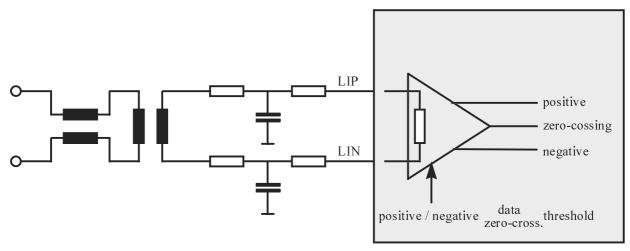

#### 3.4.4 S0 Receiver

#### Features

- Zero-crossing detection with hysteresis selectable in four step between  $\pm$  6.7% to  $\pm$  26.7 % of the programmable input threshold.

- positive/negative pulse detection selectable in four step between  $\pm$  33% to  $\pm$  100% of the nominal pulse amplitude.

- Power-down mode leaves only the zero-crossing detector powered up in order to save power.

On the chip the signals from the secondary side of the 1:2 receive transformer - LIN and LIP - are connected to current input stage followed by a zero crossing and a data detection comparator. The nominal threshold of the zero crossing detection and the data detection are relative to the input current and are set by the external serial resistors.

The hysteresis of the zero crossing detector can be set in four steps between  $\pm 6.7\%$  and  $\pm 26.7\%$  of the nominal threshold to get the best compromise between high frequency noise rejection and input sensitivity. Respectively the threshold for the input data can set in four steps between  $\pm 33\%$  and  $\pm 100\%$  of the nominal threshold.

Wakeup mode is initialised by the zero-crossing detector upon detection of activity on the line during sleep mode.

Figure 3-6: S0 Receiver

### 3.4.5 Decoupling Inputs

The S0 interface has two inputs for decoupling capacitors. For normal operation of the S0 interface capacitors have to be connected between Ref (220nF) / Cref (10nF, can be reduced up to 1 nF if necessary) and GND.

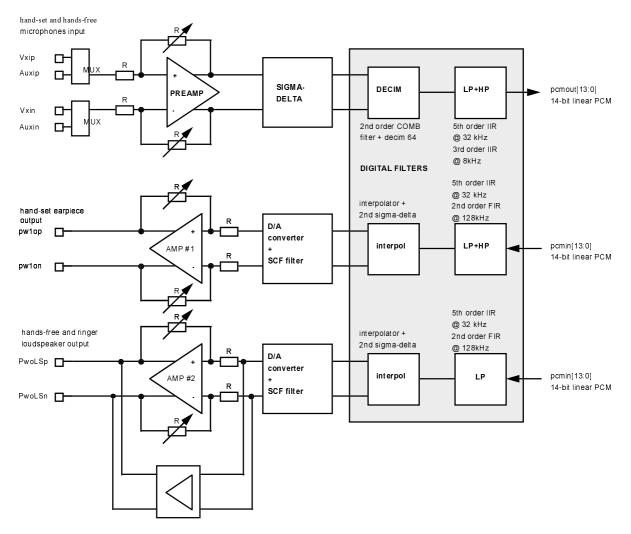

## 3.5 Analogue Front End

#### The ISDN has an analogue front end (see

Figure 3-7 below) that connects directly to a handset, a hands-free microphone and a loudspeaker. The VBAFE includes D/A- and A/D conversion and filtering. To adapt to transducer tolerances the microphone preamplifier, the earpiece amplifier and the loudspeaker amplifier have programmable gain.

Figure 3-7: Analogue Front End

### 3.5.1 Transmit Analogue Front End

The transmit path converts a signal from the analogue low level microphone input to 8 kHz digital samples according to ITU G.714/715. The microphone signal is amplified by a dedicated low-noise preamplifier whose gain is programmable. The frequency response may be adjusted at this point using appropriate external components.

Following the preamplifier is the encoder section, which uses a second-order oversampled converter operating at 2.048 MHz. The data coming out of the sigma-delta are digitally processed through a decimation filter for sampling rate reduction before subsequent low-pass and high-pass filtering.

The low noise microphone preamplifier is capable of directly interfacing with one of two microphones. The preamplifier gain is programmable in 64 steps.

## 3.5.2 Receive Analogue Front End

The G. 714/715 receive path decoder is basically the same in the opposite direction. The 8 kHz 14 bit linear data samples at the input are low-pass filtered and interpolated in two successive steps in order to limit the presence of high-frequency components outside the voice band. The data are further processed by a second-order digital modulator and are then converted into analogue signals which are filtered to further remove high frequencies before going into one of the two push-pull differential amplifiers. Most of the analogue circuitry uses differential design. This allows processing of signals with twice as much amplitude as in a single-ended design and virtually eliminates injected noise from supplies and substrate. The gain of the output amplifier is adjustable.

The side tone - calculated by the CPU - can be injected into the hand-set path if required.

There are two speaker interfaces; one to drive the earpiece transducer and one for the loudspeaker and / or ringer. The linear amplifier in the loudspeaker path can drive loads with a transconductance as low as 50  $\Omega$ . Instead of the linear amplifier a high current/voltage driver can be activated in the loudspeaker path to generate the ringing signal.

### 3.5.3 **Reference Voltage**

The reference voltage for the A/D and D/A conversion is generated internally, only an external decoupling capacitor has to be connected between Vrefn and Vrefp. The value required is 47 nF.

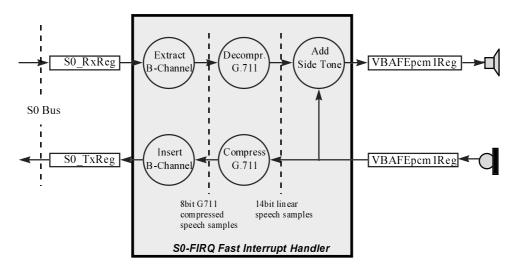

## 3.5.4 Data flow of the B-channel audio samples

The audio samples that are received by the B-channel can be read from the S0\_RxReg. To transfer the data to the VBAFEpcm1Reg / VBAFEpcm2Reg three actions have to be done in the fast interrupt handler:

- extract the B-channel from the S0\_RxReg

- decompress the A-law or  $\mu$ -law coded 8 bit data to linear 14 bit PCM values

- add side tone for user comfort (not for open listening / handsfree operation)

After this the 14 bit value can be written into the VBAFEpcmXReg.

In the other direction the 14 bit linear PCM data are read from the VBAFEpcm1Reg. There are also three actions that have to be done in the fast interrupt handler:

- generate value for side tone (not for open listening / handsfree operation)

- compress 14 bit linear to A-law or μ-law

- align data for writing to S0\_TxReg

After this the 8 bit value can be written

Figure 3-8 B-channel audio handling

## 3.6 Analogue Digital Converter

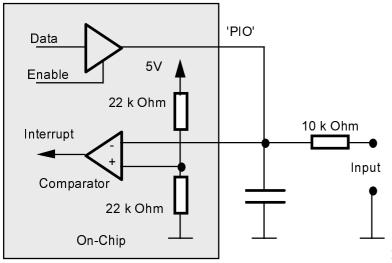

The VIP includes two simple single slope general purpose analogue digital converters (refer to Fig. 10). These ADCs are built with a simple comparator, an internally generated reference and a bi-directional output port. The comparator output is connected to an internal interrupt input of the interrupt controller.

Under CPU control it is possible to measure voltages or resistor values. After the capacitor is charged by the port, the port changes to input and a program can measure the time between start and the occurrence of the comparator interrupt.

The interrupt is issued at the falling edge.

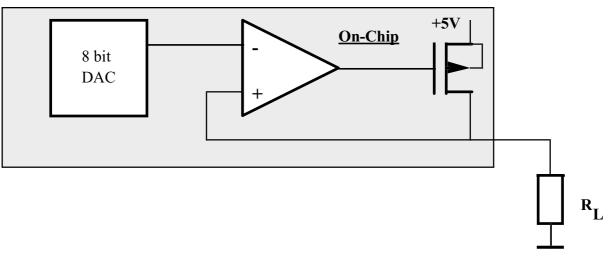

Figure 3-9: Analogue Digital Converter

### **3.7 UART**

The simple full-duplex serial interface with an interrupt driven 1 byte buffer for each direction. The start bit is active low and the LSB is transmitted first. The even or odd parity generation is done by software. The transmission formats that can be used are 8N1, 7N2, 7E1 or 7O1.

The maskable UART interrupt will be generated on UART transmit buffer empty or UART receive buffer full. UART transmission flags will be generated on UART transmit buffer busy, UART transmit buffer empty, UART receive buffer full or stop bit failure. The start bit can be read back. The a standard request to send signal (/RTS) is generated by the UART.

The baud rates are programmable in 8 steps from 1.2 kBaud to 230.4 kBaud. The baud rate clock depends on the clock used for the ARM core, either the 36,864 MHz or 460 kHz clock. Also a sleep mode (UART and baud rate clocks stopped) for power down is implemented.

The names of the UART signals correspond to the DTE definitions.

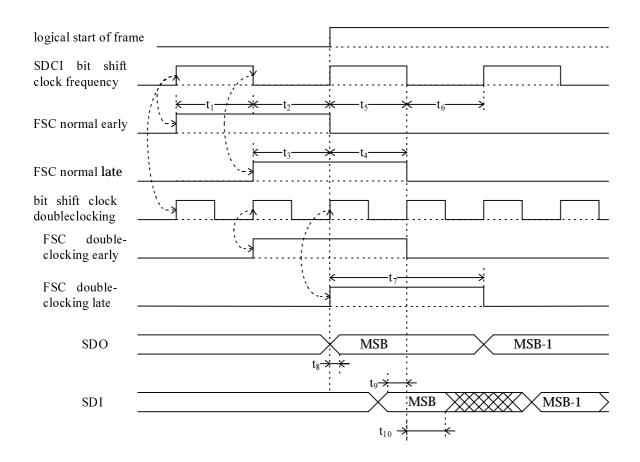

#### 3.8 Serial DSP/CODEC Interface (SDCI)

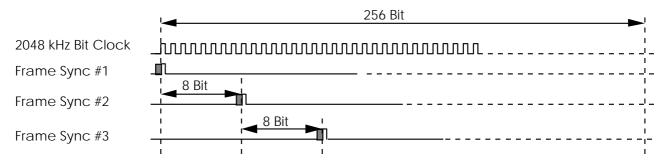

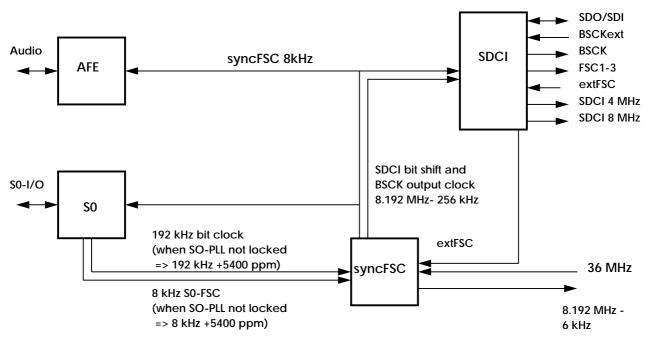

For communication with other serial devices like CODEC's, DSP's or peripherals, the VIP incorporates a full duplex serial port with a 64 bit serial - parallel converter to drive standard 8 bit telecom or 14 bit linear CODEC's. To achieve greater flexibility several functions of this port are software selectable, like frame sync on the rising or falling edge etc. (see Fig. 11).

The frequency of the clock can be set in eight steps between 512 kHz and 4096 kHz and the data rate respectively between 512 kbit/s and 2048 kbit/s.

The SDCI interface of the VIP can be used in master or in slave mode. In master mode the clocks for the interface are generated inside the VIP and control the other SDCI devices. In slave mode the SDCI interface of the VIP is clocked by an other device.

#### 3.8.1 SDCI Master Mode

In the SDCI master mode the VIP will generate all clocks that are necessary to use the SDCI interface. Additionally two further FSCs can be generated.

In the master mode the VIP can access the first 64 bit of the SDCI frame via the sdci\_lswReg and sdci\_mswReg. Only at 2048 kHz bit shift clock 4\* 64 bit can be accessed.

There are four dedicated pins to transfer data via this interface:

- BSCK --> Bit Clock output

- FSC1 --> Frame Sync1 output

SDI --> Serial Data input

SDO --> Serial Data output

- SDO --> Serial Data output

Figure 3-10: sample SDCI Interface Timing in Master Mode at 2048 kHz

Two other I/O pins may be programmed as additional frame sync signals in addition to the four pins mentioned above:

- FSC2 --> additional time slot output

- FSC3 --> additional time slot output.

FSC1 to FSC3 are used to assign one signal channel in order to directly connect up to three devices to the VIP.

In the master mode the timing source for the frame sync signals and for the bit shift clock can be selected out of three VIP internal and one VIP external timing references:

- SO PLL FSC (8 kHz if S0 is locked, else 8 kHz +5400ppm)

- SO PLL bit clock (8 kHz if S0 is locked, else 8 kHz +5400ppm)

- external high power oscillator of the VIP

- external FSC signal

#### Figure 3-11: SDCI Timing Sources

In master mode the repetitionrate of the FSC1 to FSC3 is always 8 kHz. The distance between FSC1 - FSC2 - FSC3 is always 8 bit. Therefore the number of bytes of the SDCI frame varies with the selected bit rate e.g. Figure 3-11 shows a configuration with a clock of 2048 kHz and a bit rate of 2048 kbit/s. The 'fast IR phase1 of the FSC1' will be issued at the beginning of the frame. The other 'fast IR phaseX of the FSC1' are issued but can only be used when 2048 kHz bit shift clock is used.

If the VIP accesses only the first 64 bit, the SDCI output will be tristate for the remaining frame.

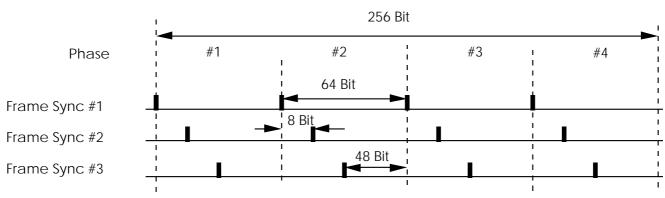

#### 3.8.2 SDCI Slave Mode

In slave mode operation the repetition rate of the external frame sync signal FSC\_EXT has to be 32 kHz. Each 32 kHz FSC\_EXT frame sync signal generates a fast interrupt. There is no timing relation between the SDCI interface and the S0-interface in slave mode operation.

In the slave mode the SDCI interface is clocked externally. For this mode four pins are used to set up the SDCI interface:

| • BSCK                      | > Bit Clock   | input  |

|-----------------------------|---------------|--------|

| <ul> <li>FSC_EXT</li> </ul> | > Frame Sync1 | input  |

| • SDI                       | > Serial Data | input  |

| • SDO                       | > Serial Data | output |

FSC\_EXT is an I/O pin that has to be programmed as frame sync input.

Each of the four 32 kHz sub-frames of the FSC1 generates a fast interrupt.

### VNS80000B - ISDN VIPem - VLSI's ISDN Processor Data Sheet

Figure 3-12: SDCI Interface Timing in Slave Mode

## 3.8.3 SDO Pin

The SDO pin is the serial output of the SDCI data. This pin is an output if the VIP writes data to the output, otherwise it is tristate.

To avoid a floating pin, a pull-up / pull-down resistor should be connected to SDO.

# 3.9 Key Pad

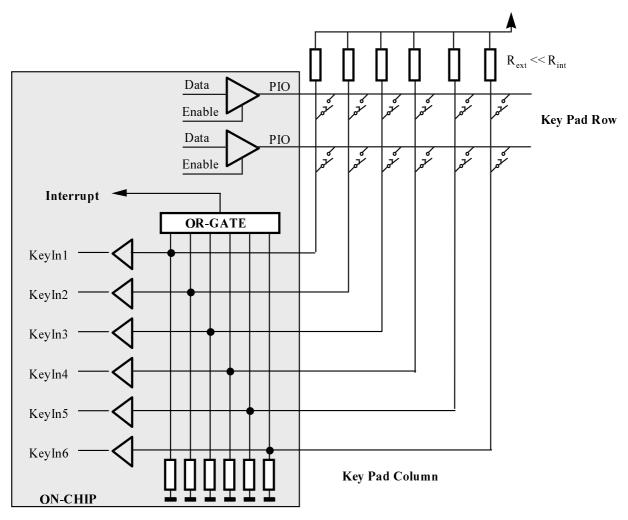

The keypad interface consists of 6 inputs with internal pull-down resistors (acting as column lines) that generate an interrupt via an or-gate. The row lines are provided by ports. A key push can generate a maskable interrupt.