## **Contents**

| ı                                    | Page     |                                  | Page |

|--------------------------------------|----------|----------------------------------|------|

| Introduction                         | 3        | Package Information              | 208  |

| Quality Assurance                    | 4        | Summary of Types                 |      |

| Mobile Communication ICs             | 9        | in Alphanumerical Order          | 209  |

| GSM/PCN                              | 11       | Microelectronics Training Center | 215  |

| DECT RF-Building Blocks              | 26<br>35 | Information on Literature        | 219  |

| Digital Terminal ICs                 | 55       | Semiconductor Group – Addresses  | 232  |

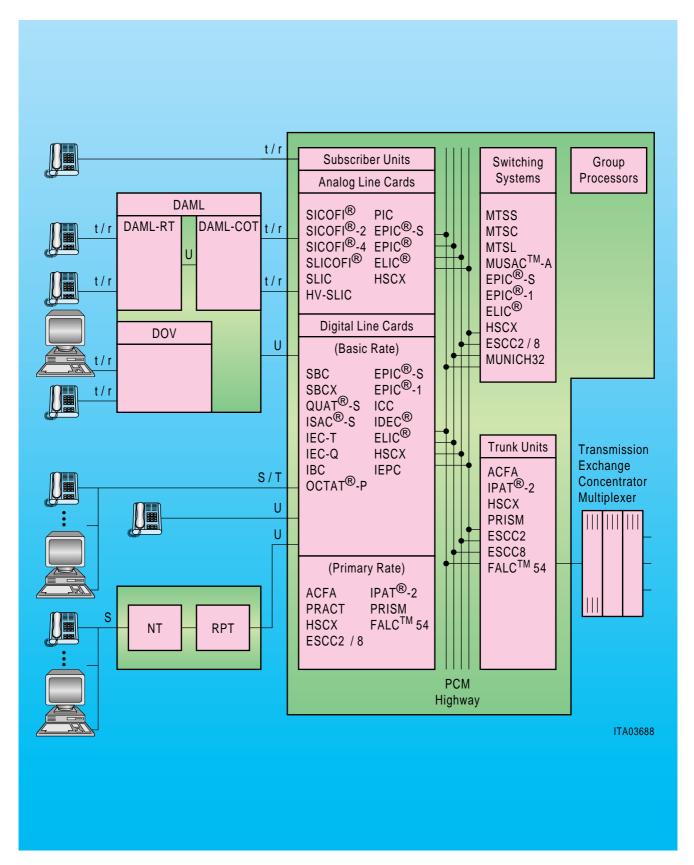

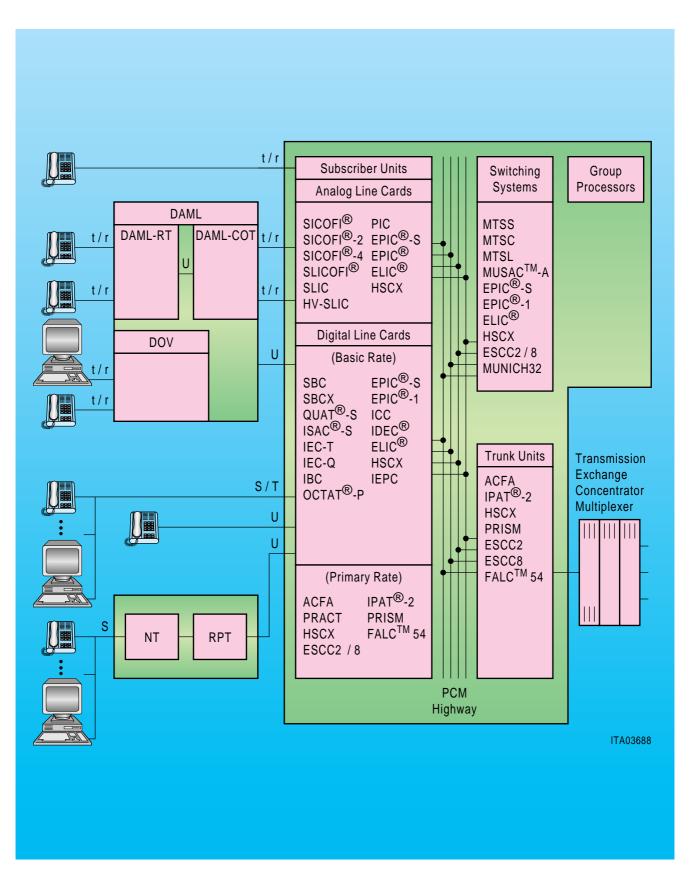

| Digital Exchange System ICs          | 79       |                                  |      |

| Analog Line Cards                    | 82       |                                  |      |

| Digital Line Cards                   | 103      |                                  |      |

| Primary Rate Interface (PRI) ICs     | 125      |                                  |      |

| Switching, Attenuation               |          |                                  |      |

| and Conferencing Family ICs          | 141      |                                  |      |

| Communication Network ICs            | 157      |                                  |      |

| Asynchronous Transfer Mode (ATM) ICs | 171      |                                  |      |

| Development Systems                  |          |                                  |      |

| for Information Technology           | 185      |                                  |      |

IOM®, IOM®-1, IOM®-2, SICOFI®, SICOFI®-2, SICOFI®-4, SICOFI®-4 $\mu$ C, SLICOFI®, ARCOFI®, ARCOFI®-BA, ARCOFI®-SP, EPIC®-1, EPIC®-S, ELIC®, IPAT®-2, ITAC®, ISAC®-S, ISAC®-S TE, ISAC®-P, ISAC®-P TE, IDEC®, SICAT®, OCTAT®-P, QUAT®-S are registered trademarks of Siemens AG.

Purchase of Siemens  $I^2C$  components conveys a license under the Philips'  $I^2C$  patent to use the components in the  $I^2C$ -system provided the system conforms to the  $I^2C$  specifications defined by Philips. Copyright Philips 1983.

$<sup>\</sup>mathsf{MUSAC}^{^{\top}}\mathsf{-A},\,\mathsf{FALC}^{^{\top}}\mathsf{54},\,\mathsf{IWE}^{^{\top}},\,\mathsf{SARE}^{^{\top}},\,\mathsf{UTPT}^{^{\top}},\,\mathsf{ASM}^{^{\top}},\,\mathsf{ASP}^{^{\top}},\,\mathsf{are}\,\,\mathsf{trademarks}\,\,\mathsf{of}\,\,\mathsf{Siemens}\,\,\mathsf{AG}.$

## Introduction

Siemens is THE allround-supplier of Communication ICs. Siemens offers ICs for Digital Exchange Systems, Digital Terminals, Data Transmission Analog and Networks, Mobile Communications and Analog Telephone Sets.

Communication ICs from Siemens – that means innovative and wide ranging problem solving. Siemens Semiconductor Division has integrated system know-how verified by wide field experience and excellent chip technology.

A short look to the product segment ISDN, demonstrates: For the development of ISDN equipment from terminals to PBX and public switching systems Siemens offers the broadest range of ISDN chips available on the merchant market. Siemens is the worldwide market leader for ISDN ICs, due to their high level of functionality resulting in greatly simplified system design.

In addition, the industry standard IOM-2 interface supports flexible system architecture with compatible devices.

Siemens represents technology leadership, offers powerful software and application tools.

Siemens is your partner for Communication ICs:

- · Innovative complete system solutions

- · Highly optimized devices

- Reliable volume production lines and advanced technology innovation

- Technical support all over the world

- · Long term experience and skilled expert teams

- · Long term customer relationships

- Excellent quality

- · Basic success factors for further innovations

- Experienced R+D team

- Device macros

- Design tools

- Technology

Due to the fact that Siemens offers a broad range of Communication ICs the overview of the spectrum is presented in this brochure.

If you have further questions or if you need application support, please contact your local Siemens office. Addresses you will find in this brochure.

Call Siemens - your partner for Communication ICs!

## **Quality Assurance**

## Quality Assurance

The high quality and reliability of integrated circuits from Siemens are the result of carefully managed design and production which is systematically checked and controlled at each stage.

The procedures are subject to a quality assurance system; full details are given in the brochure "Quality Assurance Integrated Circuits".

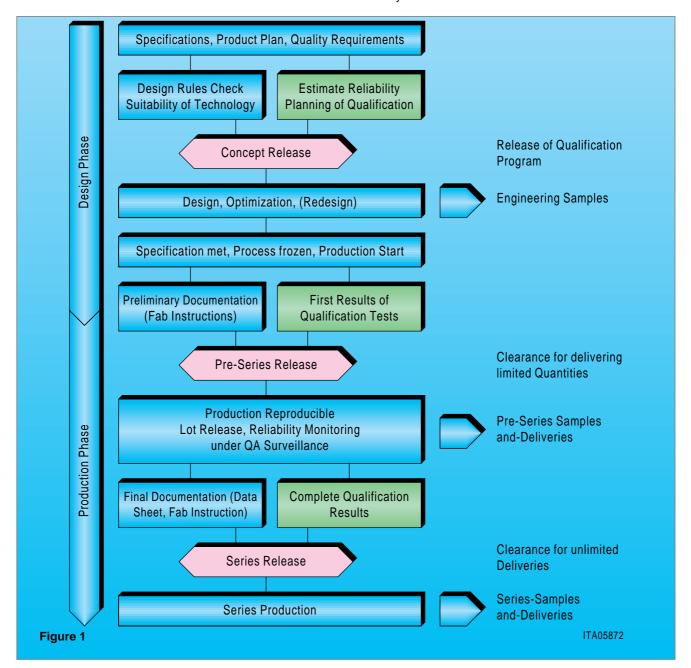

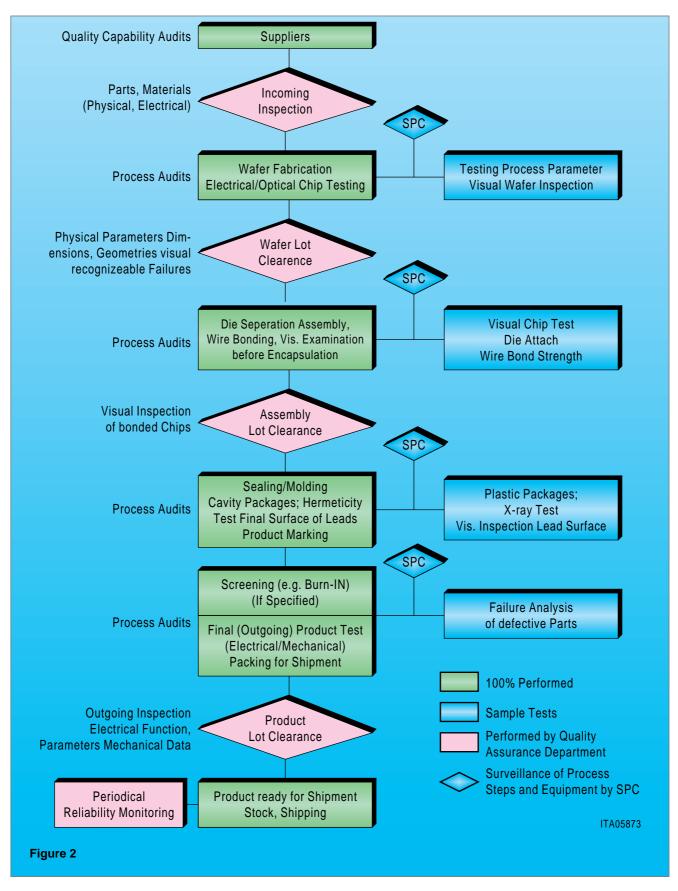

Figure 1 and 2 show the most important stages of the QA system. Quality assurance (QA) departments, independent of production and development, are responsible for the selected measures, acceptance procedures and information feedback loops. Operating QA departments have state-of-the-art test and measuring equipment at their disposal, work according to approved methods of statistical quality control, and are provided with facilities for accelerated life and environmental tests used for both qualification and routine monitoring tests.

The latest methods and equipment for preparation and analysis are employed to achieve continuity of quality and reliability.

# **Quality Assurance**

## 2 Conformance

Each integrated circuit is subjected to a final test at the end of the production process. These tests are carried out by computer-controlled, automatic test systems as hundreds of thousands of operating conditions as well as a large number of static and dynamic parameters have to be considered. Moreover, the test systems are extremely reliable and reproducible. The quality assurance department carries out a final check in the form of a lot-by-lot sampling inspection to additionally ensure the minimum percent defectives to ensure statistically that the PDA of released lots is less than the AQL agreed. Sampling inspection is performed in accordance with the inspection plans of DIN 40080, as well as of the identical MIL-STD-105 or IEC 410.

## 3 Reliability

## 3.1 Measures taken during development

The reliability of ICs is already considerably influenced at the development stage. Siemens has, therefore, fixed certain design standards for the development of circuits and layout, e.g. specifying minimum width and spacing of conductive layers on a chip, dimensions and electrical parameters of protective circuits for electrostatic charge, etc. An examination with the aid of carefully arranged programs operated on large-scale computers guarantees the immediate identification and elimination of unintentional violations of these design standards.

## 3.2 In-process control during production

The manufacturing of integrated circuits comprises several hundred production steps. As each step is to be executed with utmost accuracy, the in-process control is of outstanding importance. Some processes require more than a hundred different test measurements. The tests have been arranged such that the individual process steps can be reproduced continuously.

The decreasing failure rates reflect the never ending effort in this direction; in the course of the years they have been reduced considerably despite an immense increase in IC complexity.

### 3.3 Reliability monitoring

The general course of IC failure rate versus time is shown by a so-called "bathtub" curve. The failure rate has its peak during the first few operating hours (early failure period). After the early failure period has ended, the "constant" failure rate period starts during which the failures may occur at an approximately uniform rate. This period ends with a repeated rise of the curve during the wear-out failure period. For ICs, however, the latter period usually lies far beyond the service life specified for the individual equipment. Reliability tests for ICs are usually destructive examinations. They are, therefore, carried out with samples. Most failure mechanisms can be accelerated by means of higher temperatures. Due to the temperature dependence of the failure mechanisms, it is possible to simulate future operational behavior within a short time by applying high temperatures; this is called life test. The acceleration factor F for the life test can be obtained from Arrhenius's equation

$$F = \exp\left(\frac{E_{A}}{k}\left(\frac{1}{T_{1}} - \frac{1}{T_{2}}\right)\right)$$

where  $T_2$  is the temperature at which the life test is performed,  $T_1$  is the assumed operating temperature and k is Boltzmann's constant.

Important for factor F is the activation energy  $E_{\rm A}$ . It lies between 0.3 and 1.3 eV and differs considerably for individual failure mechanisms.

For all Siemens ICs the reliability data from life tests is converted to an operating temperature of  $T_{\rm A} = 55~^{\circ}{\rm C}$ , assuming an average activation energy of 0.5 eV. The acceleration factor for life tests at 125  $^{\circ}{\rm C}$  is thus 22, compared with operational behavior. This method considers also failure mechanisms with low activation energy, i.e. which are only slightly accelerated by the temperature effect.

Various reliability tests are periodically performed with IC types that are representative of a certain production line this is described in the brochure "Quality Assurance Integrated Circuits". Such tests are e.g. humidity test at 85 °C and 85 % relative humidity, pressure cooker test, as well as life tests up to 1000 hours and more. Test results are available in the form of summary reports.

| Quality Assurance System Quality Assurance Manual                                                                                                                                                                                             |                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Quality principles, organization, responsibility and competence for quality assurance procedures and measures during design and production of ICs are summarized in the Semiconductor Group Quality Assurance System. This system also covers | ISO 9000/EN 29000 requirements. It is documented in a Quality Assurance Manual. This manual is a guideline mandatory for all Semiconductor Group departments. Suppliers are also tied into the QA system. |

|                                                                                                                                                                                                                                               |                                                                                                                                                                                                           |

| CECC certification for the independent test and trials cent which the Villach Plant also profits from.                                                                                                                                        | ter of Semiconductor Group,                                                                                                                                                                               |

|                                                                                                                                                                                                                                               |                                                                                                                                                                                                           |

| The Villach Plant was certified to the internationally recog                                                                                                                                                                                  | nized standard ISO 9002 in 1991.                                                                                                                                                                          |

# Mobile Communication ICs

GSM One-Chip Logic Device GOLD PMB 2705

## **GSM/PCN**

## Introduction

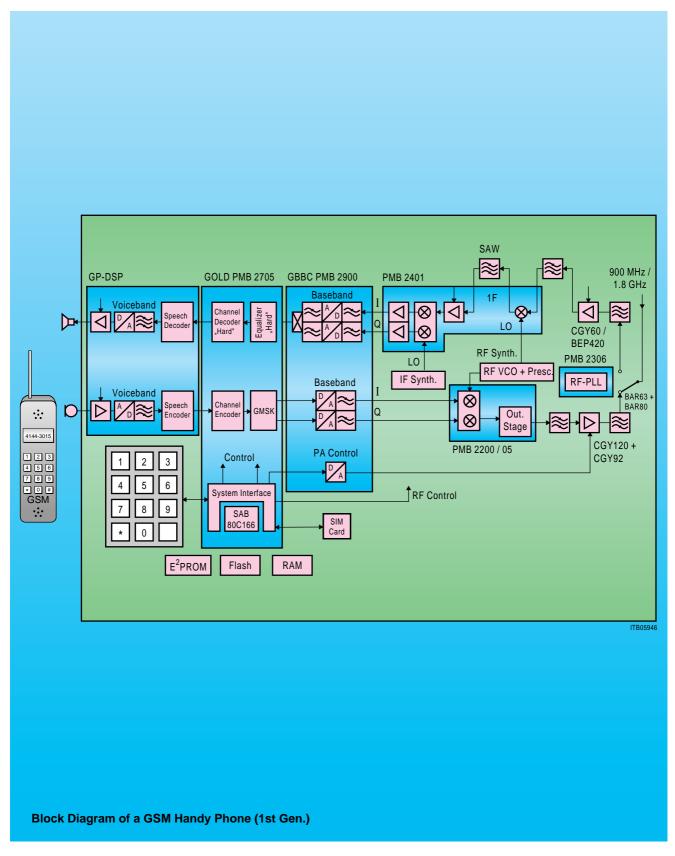

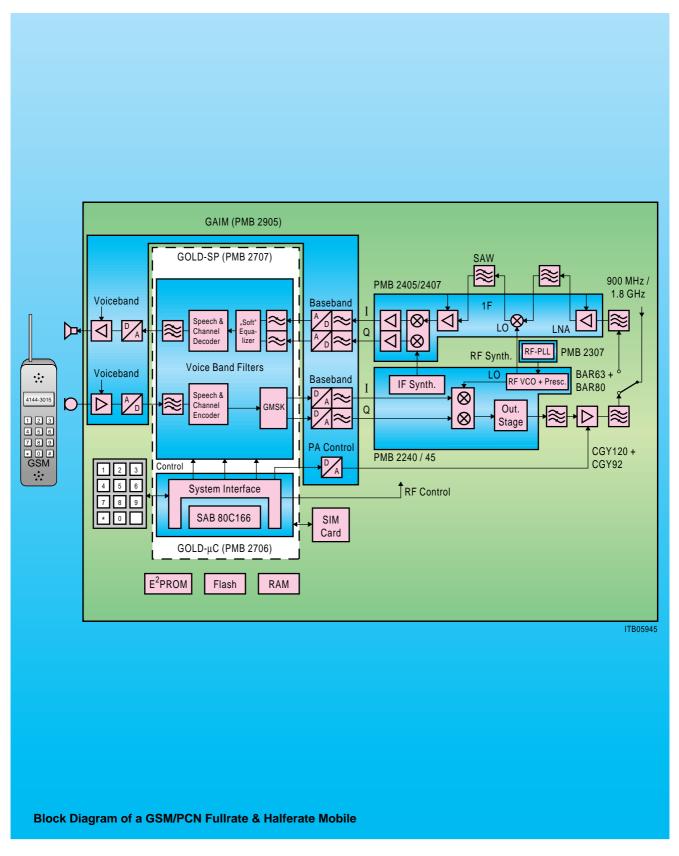

GSM and PCN have evolved in the last few years from pan-european into global standards for digital cellular mobile radio systems. The radios are small, easy-to-use and very competitively priced with the older analog systems as the explosive growth in subscribers clearly testifies.

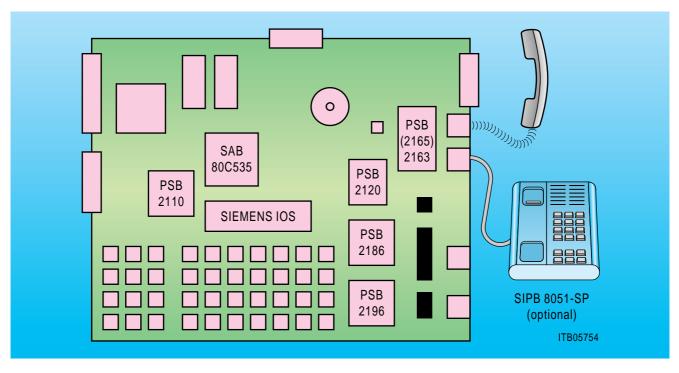

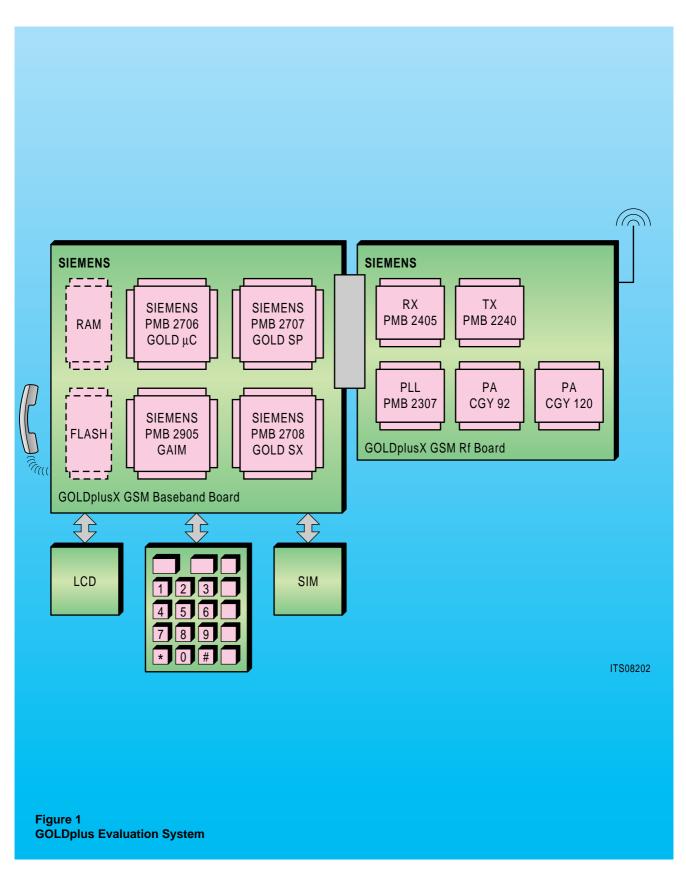

Siemens Semiconductor has played a leading role in this growth as the first supplier of commercially available standard GSM/PCN chip sets. Now after production optimizations of the GOLD chip set, Siemens is offering an evolutionary step forward in intergration level to provide a complate 3-V generation with a 6 chip solution, GOLD plus.

## **Product Overview**

| Туре      | Short Title | Description                            | Applications                                                                                     | Page |

|-----------|-------------|----------------------------------------|--------------------------------------------------------------------------------------------------|------|

| GSM Basek | and         |                                        |                                                                                                  |      |

| PMB 2705  | GOLD        | GSM One-Chip Logic Device              | GSM, PCN, PCS-1900                                                                               | 14   |

| PMB 2706  | GOLD μC     | GSM System Controller                  | GSM, PCN, PCS-1900                                                                               | 16   |

| PMB 2707  | GOLD-SP     | GSM Signal Processor                   | GSM, PCN, PCS-1900                                                                               | 18   |

| PMB 2708  | GOLD-SX     | GSM Co-Processor for Advanced Features | GSM, PCN, PCS-1900                                                                               | 18   |

| PMB 2900  | GBBC        | GSM Baseband Codec                     | GSM, PCN, PCS-1900                                                                               | 19   |

| PMB 2905  | GAIM        | GSM Analog Interface Module            | GSM, PCN, PCS-1900                                                                               | 20   |

| GSM RF    |             |                                        |                                                                                                  |      |

| PMB 2200  |             | Direct Vector Modulator                | Cellular (GSM, PDC, DAMPS, CDMA),<br>WLAN, QPSK/QAM modulation up to 1 GHz)                      | 37   |

| PMB 2205  |             | Direct Vector Modulator                | Cellular (GSM, PCN, PCS, PDC, DAMPS, CDMA), Cordless (PHS), WCPE, WLL, WLAN, QPSK/QAM modulation | 41   |

| PMB 2240  |             | GSM Transmitter, 2.7 V                 | Cellular (GSM, PDC); QPSK/QAM modulation 0.8 GHz to 1.0 GHz                                      | 21   |

| PMB 2245  |             | PCN Transmitter, 2.7 V                 | Cellular (PCN, PCS), Cordless (PHS);<br>QPSK/QAM modulation 1.65 GHz to<br>1.85 GHz              | 21   |

| PMB 2247  |             | PCS Transmitter, 2.7 V                 | Cellular (PCN, PCS), Cordless (PHS);<br>QPSK/QAM modulation 1.8 GHz to 1.95 GHz                  | 21   |

| PMB 2306  |             | PLL                                    | All analog and digital systems as RF- and IF-<br>synthesizer up to 220 MHz                       | 47   |

| PMB 2401  |             | Receiver/Demodulator Circuit           | Cellular (GSM, PDC, DAMPS, CDMA),<br>WLAN, QPSK/QAM modulation up to 0.9 GHz                     | 43   |

| PMB 2405  |             | GSM Receiver, 2.7 V                    | Cellular (GSM, PDC, DAMPS), WLAN,<br>QPSK/QAM modulation up to 2.5 GHz                           | 23   |

| PMB 2407  |             | PCN/PCS Receiver, 2.7 V                | Cellular (PCN, PCS) WLAN, QPSK/QAM modulation up to 2.5 GHz                                      | 23   |

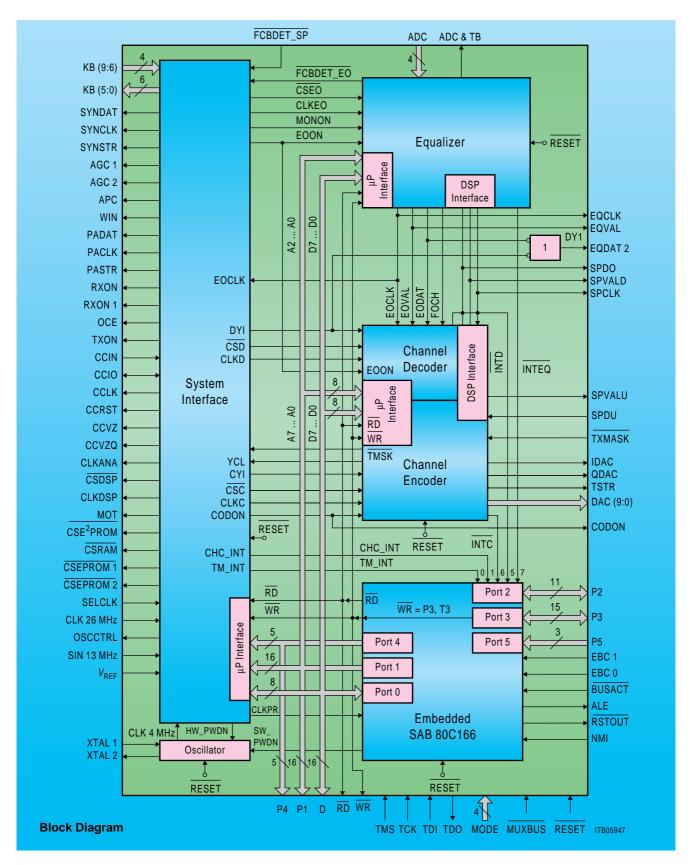

The GSM One-Chip Logic Device (GOLD) PMB 2705 performs the tasks of bit error protection, ciphering, radio channel equalization, bit error detection and correction, synchronization etc., and above all the microcontroller core controls all the RF- and baseband functions of a GSM-mobile terminal.

| Туре       | Package            |

|------------|--------------------|

| PMB 2705-F | P-TQFP-176-1 (SMD) |

- · Four function modules integrated on one chip

- 16-bit microcontroller

- Channel codec

- Equalizer

- System interface

- One special external-channel-codec mode selectable by software

- · Four operational modes selectable via pins:

- Normal mode

- External-controller mode

- External-channel-codec mode (different from special mode!)

- External-equalizer mode

- · Four single modes selectable via pins

- Controller test mode

- System interface test mode

- Channel-codec test mode

- Equalizer test mode

- Two sizes of address spaces covered by chip-select signals selectable via pin:

- 256 Kbyte

- 2 Mbyte

- · Programmable power saving modes

- JTAG-boundary scan (acc. to IEEE Std. 11491)

- Single supply voltage (+ 5 V)

- Low power consumption

- Temperature range 25 °C to 85 °C

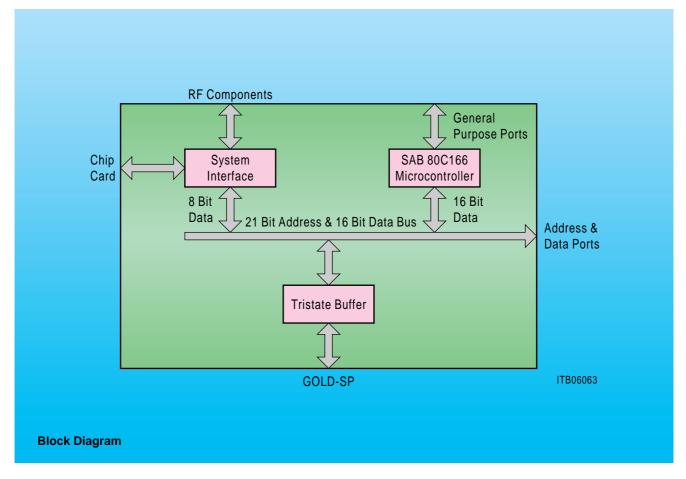

The GOLD System Controller (GOLD- $\mu$ C) is part of a chip set, which covers all functions of a mobile radio provided for the **G**lobal **S**ystem for **M**obile communications, GSM. A mobile terminal which contains this chip set will meet all performance requirements set down in the GSM recommendations for speech and data services.

GOLD- $\mu$ C contains a 16-bit microcontroller type 80C166 with an address space being extended from 256 Kbyte to 2 Mbyte and a system interface block which comprises a series of GSM-specific interfaces and control functions.

| Туре       | Package            |

|------------|--------------------|

| PMB 2706-F | P-TQFP-144-2 (SMD) |

- Integrated 16-bit microcontroller (SAB 80C166) with 2-Mbyte linear address space Complete development tooling available

- System interface with synthesizer, AGC, AFC and PA control, chip card interfacing, timing signal generation, clock generation

- Bidirectional tristate buffer GOLD-SP can access to controller memory

- Package P-TQFP-144, 20 × 20 mm, 0.50 mm pitch

- 3-V supply voltage (± 10 %)

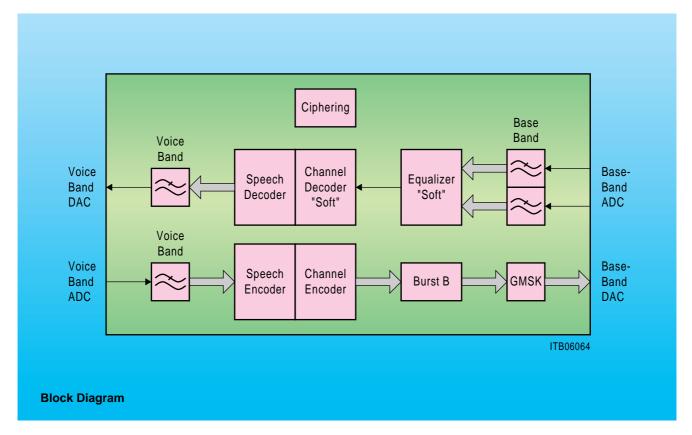

The GOLD Signal Processor (GOLD-SP) is part of a chip set, which covers all functions of a mobile radio provided for the **G**lobal **S**ystem for **M**obile communications, GSM. A mobile terminal which contains this chip set will meet all performance requirements set down in the GSM recommendations speech and data services.

GOLD-SP contains a fullrate speech codec, a channel codec with soft-decision decoding and a complex Viterbi equalizer, all as DSP firmware. Moreover all digital filtering needed for baseband and voiceband processing, and also GMSK modulation is performed on this chip.

| Туре       | Package            |

|------------|--------------------|

| PMB 2707-F | P-TQFP-100-1 (SMD) |

- Two parallel DSP cores type SPC each with high performance (26 MIPS @ 2.7 V), low current consumption (< 1 mA/MIPS), all memory needed for fullrate operation on chip, shared access to complete controller memory

- GSM functions realized as DSP firmware

- Complex soft-output equalizer

- Frequency correction burst handling

- Full duplex handsfree

- Channel coding

- Soft-decision decoding (bit-by-bit)

- Speech coding and decoding (RPE-LTP)

- Digital baseband filter

Automatic amplitude calculation

Automatic amplitude offset measurement

- Ciphering with A51/A52

- Digital voiceband filters (receive, transmit)

- GMSK modulator

- · PLL-based system clock generation

- Package: P-TQFP-100, 14 × 14 mm, 0.50 mm pitch

- 3-V supply voltage (± 10 %)

The GOLD-SX is part of a complete chip set which covers all functions of a mobile radio for the Global System for Mobile communications, GSM. A mobile terminal which contains this chip set can meet all performance requirements set down in the Technical Specifications for GSM, PCN and PCS-1900.

GOLD-SX is used for advanced features. The function of the GOLD-SX is dependent on its firmware.

The first version of the GOLD-SX performs Half-Rate speech encoding including Voice Activity Detection (VAD) and Discontinuous Transmission (DTX), as well as Half-Rate speech decoding including Discontinuous Reception (DRX, Comfort Noise).

A planned version will perform: Enhanced Full-Rate speech coding including all the DTX functions as in Half-Rate speech coding.

#### **Features**

#### Firmware:

The GOLD-SX is available in versions with different mask programmed ROM code:

- · Half-Rate Codec

- GSM Half-Rate Speech Codec (GSM 6.02, 6.06, 6.07, 6.20)

- Voice activity detection, VAD (GSM 6.42)

- Discontinuous transmission, DTX (GSM 6.41)

| Туре       | Package           |

|------------|-------------------|

| PMB 2708-F | P-TQFP-64-1 (SMD) |

- Comfort noise generation, DRX (GSM 6.22)

- Serial data exchange with Half-Rate Channel Codec and voiceband unit on GOLD-SP

- Serial data exchange with system simulator interfacing box

- · Enhanced Full-Rate Codec

- GSM Enhanced Full-Rate Codec

- Voice activity detection, VAD

- Discontinuous transmission, DTX

- Comfort noise generation, DRX

- Serial data exchange with Enhanced Full-Rate Channel Codec and voiceband unit on GOLD-SP

- Serial data exchange with system simulator interfacing box

#### Hardware:

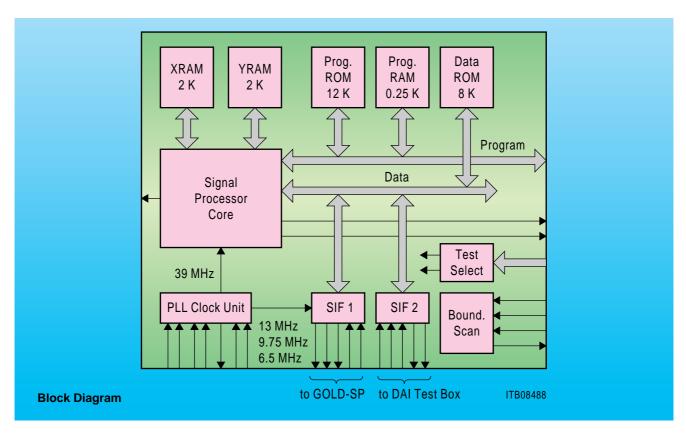

- DSP core of type SPCE (Siemens Signal Processor Core Enhanced) offering high performance (39 MIPS @ 39 MHz, 2.7 V) and current consumption (approx. 0.6 mA/MIPS)

- 12 K Program ROM and 0.25 K RAM, 8 K Data ROM on-chip

- PLL-based clock generation (13-MHz input)

- Package: P-TQFP-64, 10 × 10 mm², 0.50 mm pitch

- 3-V supply voltage (± 10 %)

## **Preliminary Data**

## Overview

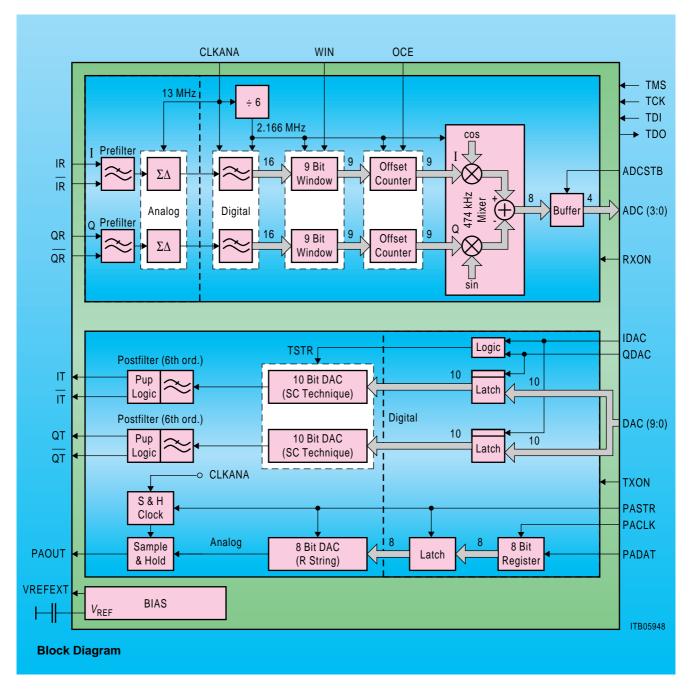

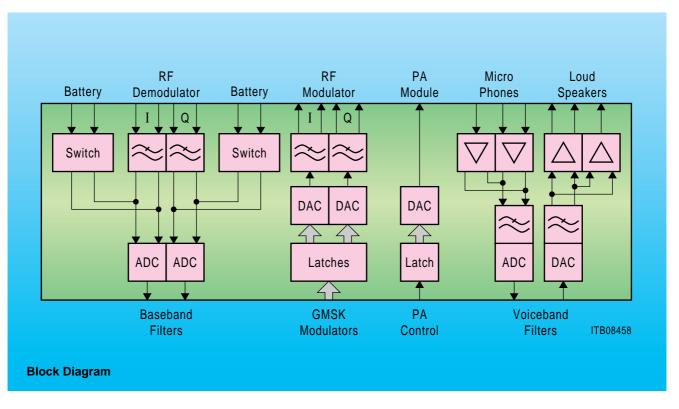

The GSM Baseband Codec (GBBC) performs the analog-todigital and the digital-to-analog conversion of the baseband signals and additionally the digital-to-analog conversion of the control signal provided for the RF power amplifier.

GBBC is part of a chip set, which covers the functions of a mobile radio provided for the Global System for Mobile communications, GSM. A mobile terminal which contains this chip set will meet all performance requirements set down in the GSM recommendations.

| Туре       | Package           |

|------------|-------------------|

| PMB 2900-H | P-MQFP-64-1 (SMD) |

#### **General Features**

- JTAG-boundary scan (acc. to IEEE Std. 1149.1)

- Single supply voltage (+ 5 V)

- Ambient temperature range 25 °C to 85 °C

The **G**SM **A**nalog **I**nterfacing **M**odule (GAIM) is part of a chip set, which covers all functions of a mobile radio provided for the **G**lobal **S**ystem for **M**obile communications, GSM. A mobile terminal which contains this chip set will meet all performance requirements set down in the GSM recommendations for speech and data services.

GAIM is provided for analog-to-digital and digital-to-analog conversion of baseband and voiceband signals as well. Moreover digital-to-analog conversion of an RF power control signal can be performed by this circuit.

| Туре       | Package           |

|------------|-------------------|

| PMB 2905-F | P-TQFP-64-1 (SMD) |

- Baseband receive A-to-D converter analog antialiasing filter (2nd order Bessel)

2nd order sigma-delta modulators for baseband receive and battery measurements

- Baseband transmit D-to-A converter 10 bit switched-capacitor-type DAC analog postfilter (6 th order Bessel)

- Power ramping control D-to-A converter 8-bit resistor-string-type DAC

- Voiceband receive D-to-A converter low pass filter following digital Σ-Δ-modulator on GOLD-SP two programmable earpiece gain stages

- Voiceband transmit A-to-D converter 2nd order sigma-delta modulator analog antialiasing filter two programmable microphone gain stages

- Package P-TQFP-64-1, 10 × 10 mm, 0.5 pitch

- 3-V supply voltage (± 10 %)

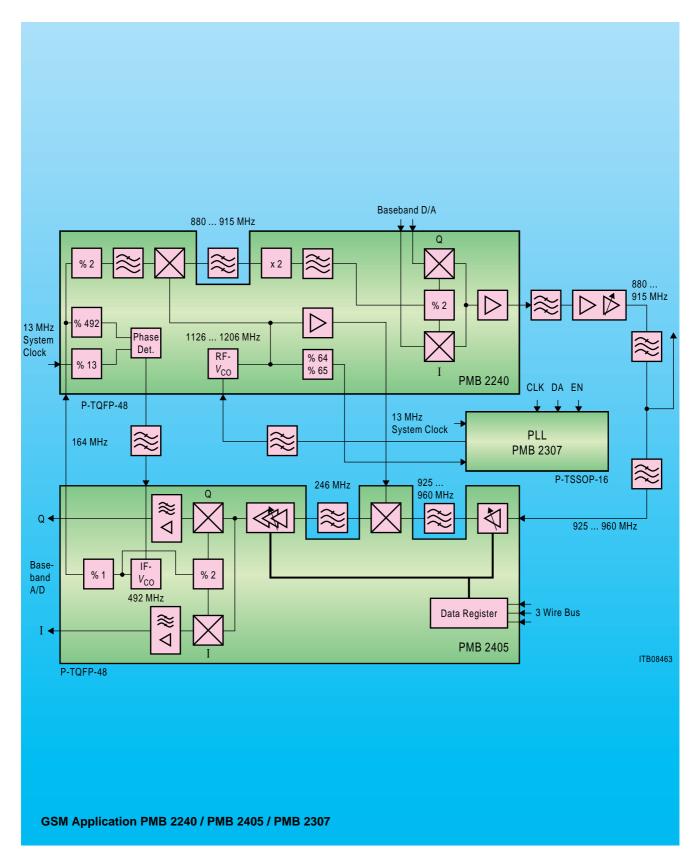

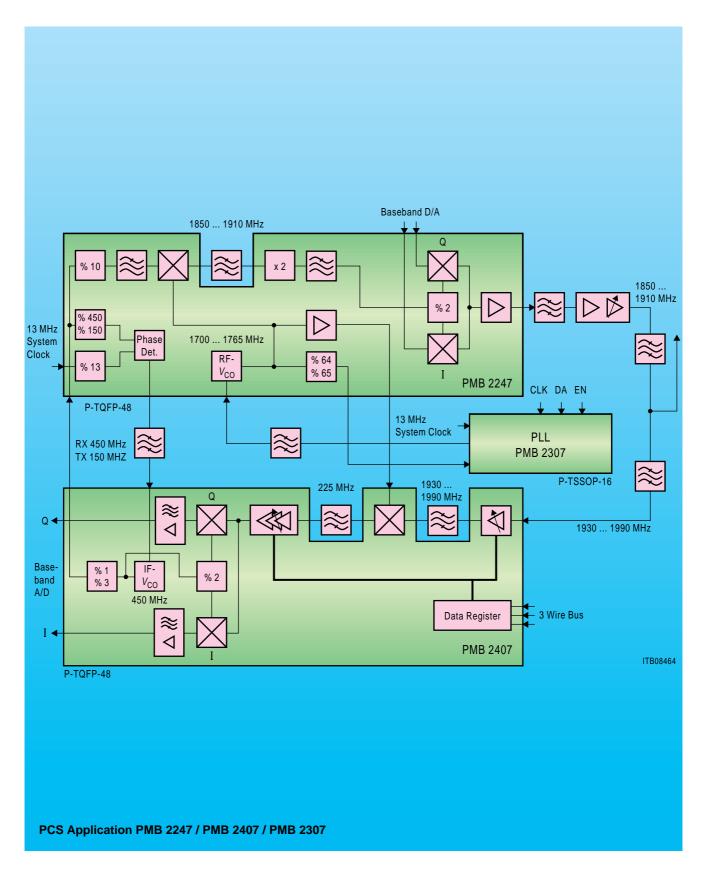

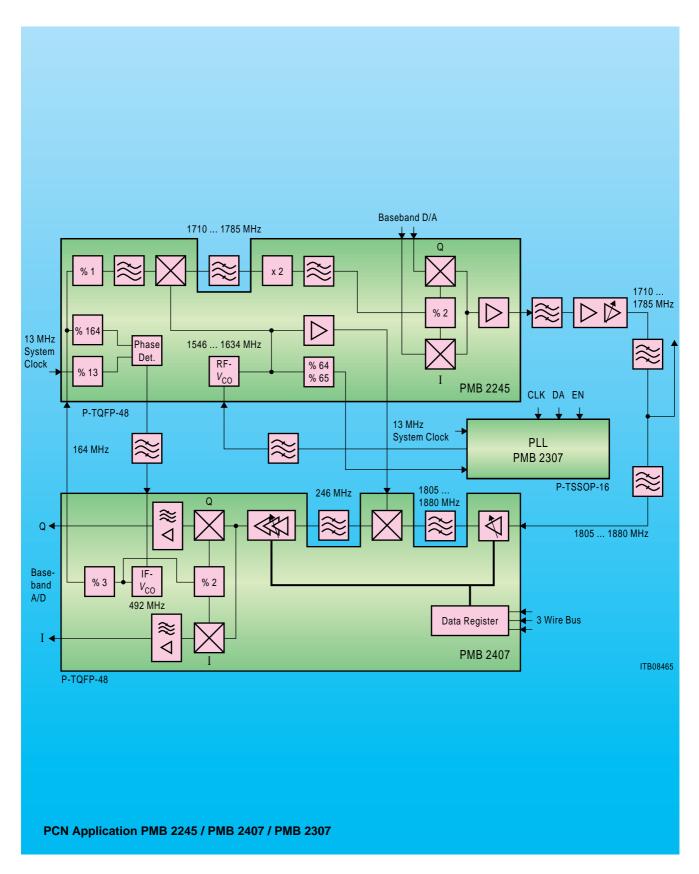

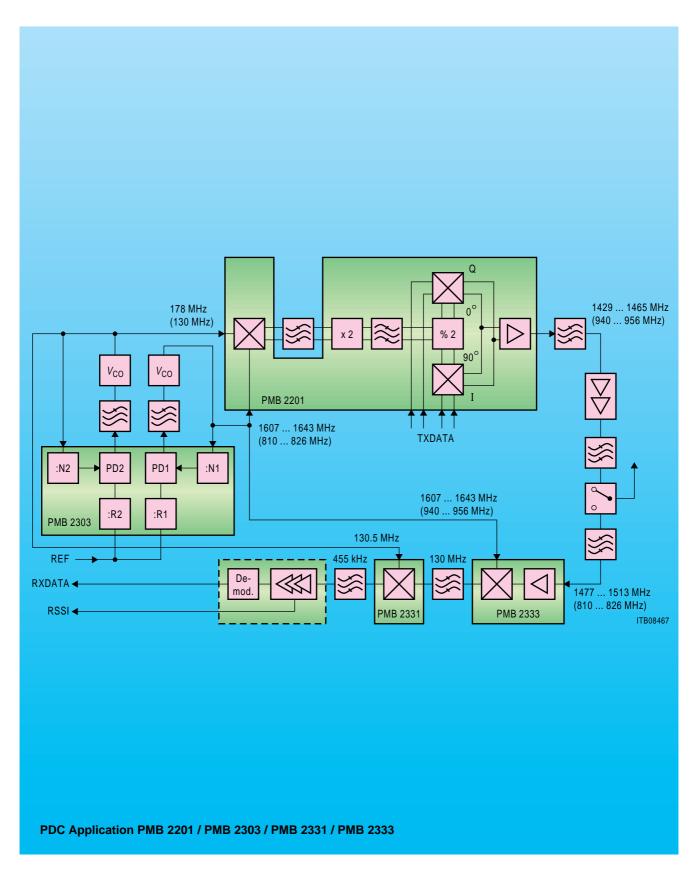

PMB 2240  $^{\rm B6HF}$  PMB 2245  $^{\rm B6HF}$  PMB 2247  $^{\rm B6HF}$

## **General Description**

The PMB 2240, 2245, 2247 family are single-chip transmitters which include a prescaler for the RF-oscillator signal and a fixed PLL for the IF-oscillator signal. The transmitter family is designed for use in combination with the single-chip receiver family PMB 2405, 2407 and the PLL PMB 2307 for mobile telephones according to the GSM, PCN and PCS standards and other vector modulated digital systems. It is fabricated using Siemens B6HF silicon process:

| GSM Chipset | PCN Chipset | PCS Chipset |     |

|-------------|-------------|-------------|-----|

| PMB 2240    | PMB 2245    | PMB 2247    | TX  |

| PMB 2405    | PMB 2407    | PMB 2407    | RX  |

| PMB 2307    | PMB 2307    | PMB 2307    | PLL |

The PMB 2240/45/47 transmitters include the active structures for the main oscillator circuit. Alternatively the oscillator signal can be supplied from an external source. The oscillator signal is buffered for off-chip use.

There is a prescaler by 64/65 for the RF-oscillator signal on chip, which can be used to implement the PMB 2307 PLL circuit.

The on-chip FIX-PLL consists of the system clock divider, the IF-oscillator signal divider, the phase detector and the charge pump. The IF-oscillator signal divider is driven by the oscillator on the PMB 2405/07 or by an external discrete VCO. The IF-oscillator signal divider ratio of PMB 2240 and PMB 2245 is fixed. It can be selected either divided by 1 or by 3 using PMB 2247 and PMB 2407 to drive the FIX-PLL with two IF frequencies (450 MHz or 150 MHz) to avoid spurious problems for PCS application.

The two oscillator signals (IF and RF) are combined in the transmit mixer, and the image sideband and other mixing products are to be suppressed by an external interstage filter. The filtered signal reenters the chip at the modulator inputs. The modulator generates two orthogonal carriers which are mixed with the I- and Q modulation signals by two multipliers. The phase between the two carriers can be fine-adjusted to 90° (orthogonality) by two external resistors for maximum SSB suppression. The outputs of the multipliers are added and amplified by a linear output stage.

| Туре       | Package           |

|------------|-------------------|

| PMB 2240-F | P-TQFP-48-1 (SMD) |

| PMB 2245-F | P-TQFP-48-1 (SMD) |

| PMB 2247-F | P-TQFP-48-1 (SMD) |

## **Application**

- Vector modulated cellular and cordless systems:

- PMB 2240: GSM, PDC, DAMPS

- PMB 2245: PCN, PCS, PHS

- PMB 2247: PCN, PCS, etc.

- Various modulation schemes, such as PM, PSK, FSK, QAM, QPSK, GMSK etc.

- Analog systems with FM- and AM modulation

- Space and power saving optimizations of existing discrete transmitter circuits

- Transmitter with I/Q modulator

- Direct I/Q modulation

- Generation of orthogonal carriers with possibility of phase adjust with external resistors

- · 30-dB carrier rejection, 40-dB SSB rejection

- 48-dB rejection of third order products with 500-mVpp I/Q-drive level

- High output power with appropriate power matching network at 500-mVpp I/Q-drive level

PMB 2240: – 3 dBm, PMB 2245: – 6 dBm

PMB 2247: – 8 dBm

- · Integrated active part of RF oscillator

- · Possibility to use external RF-oscillator signal

- The RF-oscillator signal is buffered for off-chip use, especially for receiver PMB 2405/07

- Prescaler for the RF-oscillator signal

- Possibility to use the IF oscillator integrated on the PMB 2405/07

- Possibility to use external IF-oscillator signal

- Fixed IF frequency PLL (FIX-PLL) for IF-VCO (PMB 2240, 2245), switchable IF PLL working at 450-MHz or 150-MHz IF frequency (PMB 2247)

- Supply voltage range 2.7 to 5.5 V

- P-TQFP-48 package

- Temperature range 30 °C to 85 °C

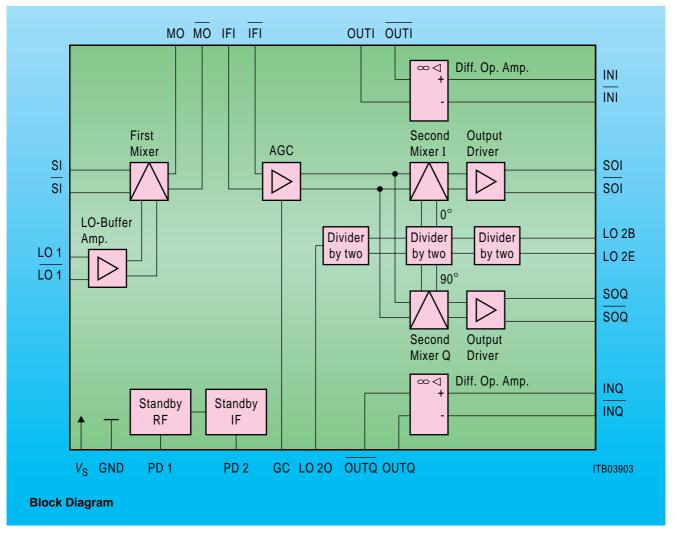

The PMB 2405, 2407 family are single-chip double-conversion heterodyne receivers with LO-phase shifting circuitry for the I/Q-phase demodulation on chip. It also includes a switchable low noise amplifier, the second local oscillator with a VCO output buffer, a programmable gain controlled IF amplifier, two differential operational amplifiers for base band signal filtering and a power-down circuitry.

The receiver family is designed for use in combination with the single chip transmitter family PMB 2240, 2245, 2247 and the PLL PMB 2307 for mobile telephones according to the GSM, PCN and PCS standards and other vector modulated digital systems. It is fabricated using Siemens B6HF silicon process.

| GSM Chipset | PCN Chipset | PCS Chipset |     |

|-------------|-------------|-------------|-----|

| PMB 2405    | PMB 2407    | PMB 2407    | RX  |

| PMB 2240    | PMB 2245    | PMB 2247    | TX  |

| PMB 2307    | PMB 2307    | PMB 2307    | PLL |

The input signal is amplified by the internal LNA and filtered by an external filter. The filtered signal and the first local oscillator signal LO1 are mixed down to an intermediate frequency (IF). The amplification of the IF signal is performed by a digitally programmable gain-controlled amplifier.

The second local oscillator signal LO2 is generated either by an on-chip oscillator or by an external VCO. The internal LO2 signal is fed to a divider (PMB 2405-by 1; 2407-by 1 or 3) and then to a buffered output and also to a divider, which generates orthogonal signals at half the VCO frequency. The filtered IF signal re-enters the chip at the IF input, where it is amplified and converted to the final output frequency with each of the orthogonal signals. The resulting in-phase and inquadrature signals pass through differential output drivers.

Two differential operational amplifiers can be used as active baseband filters. At both outputs the differential offset is sensed via the sample and hold circuitry. A feedback loop corrects the remaining offset error below the tolerable input value of the GAIM PMB 2905 or any other baseband A/D converter.

| Туре       | Package           |

|------------|-------------------|

| PMB 2405-F | P-TQFP-48-1 (SMD) |

| PMB 2407-F | P-TQFP-48-1 (SMD) |

## **Applications**

- Vector modulated cellular and cordless systems: PMB 2405: GSM, PDC, DAMPS, PMB 2407: PCN, PCS (DCS1900), WLAN etc.

- Various demodulation schemes, such as PM, PSK, FSK, QAM, QPSK, GMSK

- Space and power saving optimizations of existing discrete demodulator circuits

- · Heterodyne receiver with demodulator

- On-chip, low noise amplifier (LNA),

- Demodulation and generation of I/Q components

- · Low mixer noise 9 dB (SSB)

- High input intercept point + 2 dB

- Integrated phase shifter

- IF amplifier with 80 dB programmable gain control (PGC) in steps of 2 dB

- On-chip second LO oscillator with external tuning circuit or possibility to use it as amplifier

- Two differential operational amplifiers for use as base band filter or amplifier

- Low power consumption due to highly flexible power-down capability

- Wide input frequency range up to 2.5 GHz

- Wide IF range from 40 MHz to 300 MHz

- Supply voltage range 2.7 to 4.5 V

- P-TQFP-48 package

- Temperature range 30 °C to 85 °C

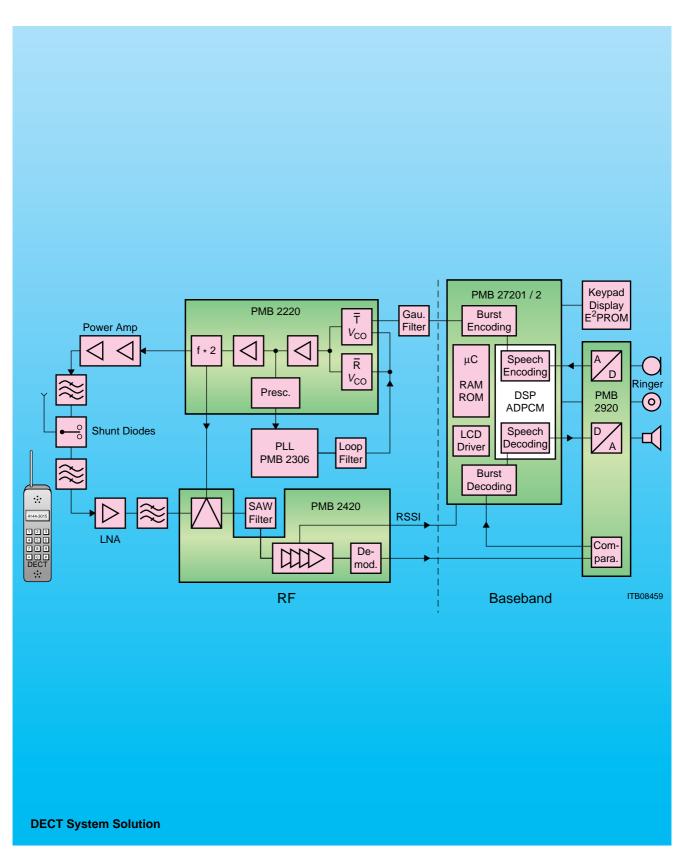

## **DECT (Digital European Cordless Telecommunication)**

## Introduction

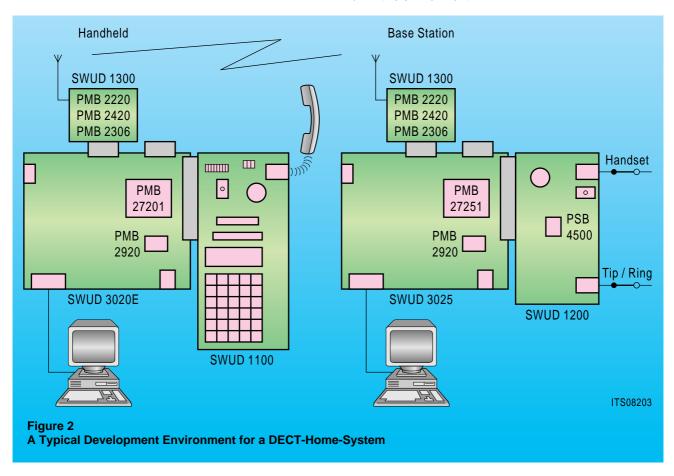

DECT is the coming **D**igital **E**uropean **C**ordless **T**elecommunication standard which has been defined for a wide range of different applications. It meets the requirements of cordless equipment users of home applications, of the office environment (e.g. cordless PBX) and of public use as wireless local loop.

DECT is the result of teamwork between industry, administration and service providers from all over Europe. It will be introduced in all EU countries and has high potential to be accepted as a standard also outside Europe.

As the first supplier worldwide, Siemens Semiconductor offers a complete highly integrated DECT system solution which covers baseband processing as well as the RF front end. The Siemens' solution for the DECT mobile station cuts down component count of first generation design from more than 500 parts to less than 200 components and saves cost, board space and power. Besides solutions for DECT home terminals and handheld systems, solutions are provided for cordless key systems, cordless PBX and wireless local loop applications, too.

#### **Product Overview**

| Туре        | Description                                                 | Applications                                                           | Page |

|-------------|-------------------------------------------------------------|------------------------------------------------------------------------|------|

| DECT Baseba | and                                                         |                                                                        |      |

| PMB 27201/2 | DECT Baseband Controller for Handhelds                      | DECT Baseband Controller for Handhelds                                 |      |

| PMB 27251/2 | DECT Baseband Controller for Basestation                    |                                                                        | 29   |

| PMB 2727    | DECT Burst Mode Controller for PBX                          |                                                                        | 30   |

| PMB 2728    | DECT Burst Mode Controller and ADPCM Codec for Keys Systems |                                                                        | 31   |

| PMB 2920    | DECT Baseband Analog IC                                     |                                                                        | 32   |

| DECT RF     |                                                             |                                                                        |      |

| PMB 2220    | DECT Transmitter, 3 V                                       | Cordless (DECT); FSK modulation                                        | 33   |

| PMB 2306    | PLL                                                         | All analog and digital systems as RF- and IF synthesizer up to 220 MHz | 47   |

| PMB 2420    | DECT Receiver, 3 V                                          | Cordless (DECT), FSK modulation                                        | 34   |

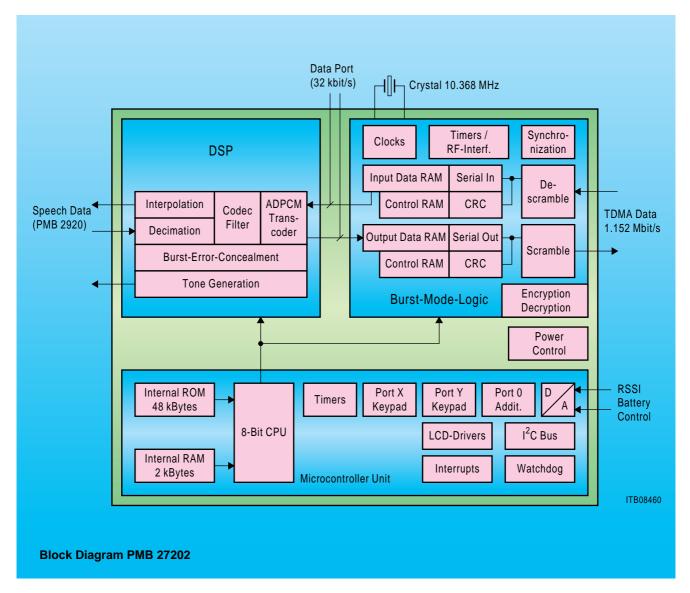

The DECT-Digital Circuit for Handhelds is one of the devices of the Siemens chip set for the digital cordless telephone specified by the DECT standard.

The device designed for cordless handhelds is a highly integrated circuit and realizes most of the system functions needed in such an equipment.

The circuit contains a digital signal processor, an 8-bit 80C51-compatible microcontroller and the burst mode controller. Furthermore the circuit handles the interfacing of the different components of the DECT chipset and feature LCD controller.

The device is fabricated using Siemens advanced CMOS technology and will be available in a 128 pin package.

Further baseband controllers are PMB 27221 (romless version with 4 K RAM).

| Туре        | Package            |

|-------------|--------------------|

| PMB 27201/2 | P-TQFP-128-1 (SMD) |

- 8-bit μC with integrated ROM/RAM

- Integrated LCD controller

- 32-kbit/s ADPCM-transcoder

- Digital filtering and gain stages

- Burst mode controller

- Power-down mode programmable

- · Low voltage detection

- Power supply 3.0 ... 5.1 V

- Low power consumption

- · Advanced low power CMOS technology

- Encryption

- PMB 27201: 64 K ROM, 4 K RAM

- PMB 27202: 48 K ROM, 2 K RAM

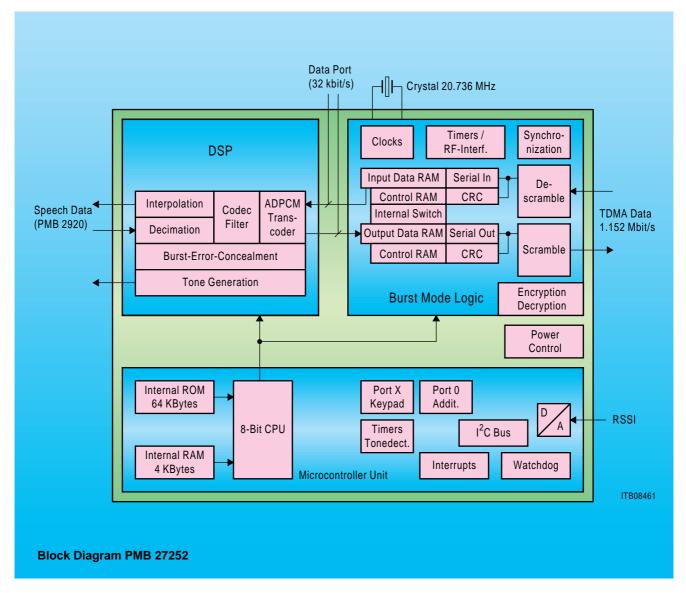

The DECT-Digital Circuit for Basestations is one of the devices of the Siemens chip set for the digital cordless telephone specified by the DECT standard.

The device designed for single cordless fixed stations is a highly integrated circuit and realizes most of the system functions needed in such an equipment. The circuit contains a digital signal processor, an 8-bit 80C51-compatible microcontroller and the burst mode controller. Furthermore the circuit handles the interfacing of the different components of the DECT chipset.

The device is fabricated using Siemens advanced CMOS technology and will be available in a 128 pin package.

| Туре        | Package            |

|-------------|--------------------|

| PMB 27251/2 | P-TQFP-128-1 (SMD) |

- 8-bit μC with integrated ROM/RAM

- 32 bit/s ADPCM-transcoder

- · Digital filtering and gain stages

- Echocancellation

- · Burst mode controller

- · Internal calls possible

- Power supply voltage: 5 V ± 5 %

- Low power consumption

- Advanced low power CMOS technology

- Encryption

- PMB 27251: 6 K RAM

- PMB 27252: 64 K ROM, 4 K RAM

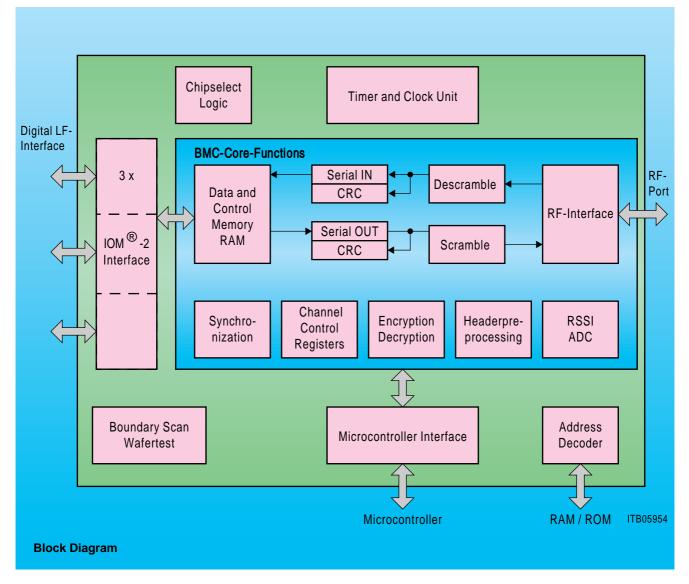

The DECT Multichannel Burst Mode Controller is one of the devices of the Siemens chip set designed cordless applications specified by the DECT standard.

The device can handle up to twelve DECT channels. It supports most of the Medium Access Control (MAC) layer and Physical layer (PHL) functions specified in the DECT standard. An interface to a standard 8-bit microcontroller (Motorola and Intel compatible) is implemented.

Furthermore 3 IOM-2 interfaces are integrated e.g. for direct connection of  $\rm U_{P0}$  transceivers (ISAC-P TE). The on-chip RF interface allows the control of the DECT-RF circuitry with a minimum of discrete components.

The circuit can be used in DECT basestations (Radio Fixed Parts RFPs). The device supports unprotected data transmission.

The device is fabricated using Siemens advanced CMOS technology and will be available in a 100 pin package.

| Туре       | Package            |

|------------|--------------------|

| PMB 2727-H | P-MQFP-100-2 (SMD) |

- Power-down mode programmable

- Power supply voltage: 5 V ± 5 %

- Low power consumption: 100 mW (5 V)

- Advanced low power CMOS technology

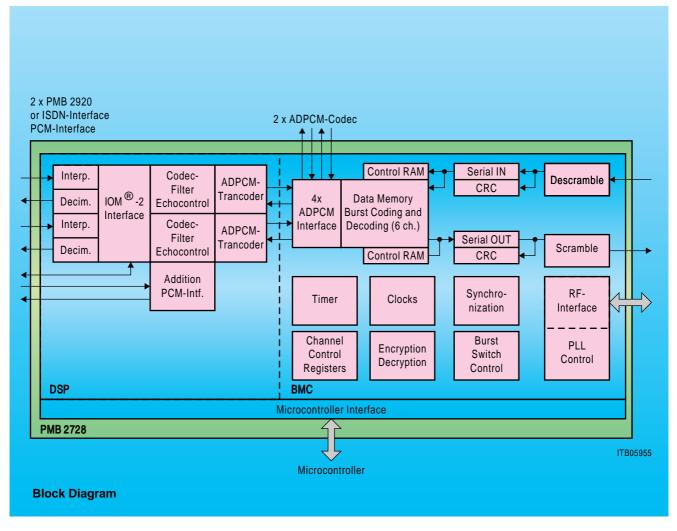

DECT PBX PMB 2728

## **General Description**

The DECT PBX circuit is one of the devices of the Siemens chip set designed for cordless basestations specified by the DECT standard.

The circuit consists of two main functional blocks, these are the Burst Mode Controller (BMC) and the Digital Signal Processor (DSP).

The BMC can handle up to six DECT channels. It supports the timecritical functions specified in the DECT standard. Either 6 internal connections between handheld or 2 internal and 2 external connections can be handled. An interface to a standard 8-bit microcontroller (Motorola/Mitsubishi and Intel compatible) is implemented. The on-chip RF interface allows the control of the DECT-RF circuitry with a minimum of discrete components.

The one-chip DSP can handle PCM/ADPCM

- transcording and echosupression due to the DECT

- standard for two channels.

| Туре       | Package            |

|------------|--------------------|

| PMB 2728-H | P-MQFP-100-2 (SMD) |

#### **Features**

- Power supply voltage: 5 V ± 5 %

- Low power consumption

- 100 pin P-MQFP packaging

- Advanced low power CMOS technology

Furthermore 1 IOM-2 interface is integrated e.r. for connection of an ISDN interface device (ISAC-S) or of a high feature codec device (ARCOFI, PSB 2163). For analog line interfaces two circuits PMB 2920 can be directly connected to the PMB 2728. Furthermore an additional PCM interface is implemented for connection of an answering machine.

The device is fabricated using Siemens advanced CMOS technology and will be available in a 100 pin package.

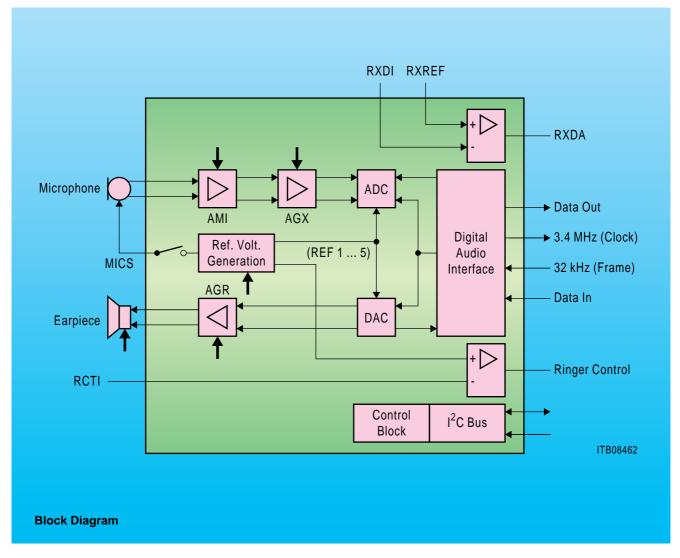

The DECT-Analog Circuit is one of the devices of the Siemens chip set for the digital cordless telephone specified by the DECT standard.

The device designed for cordless handhelds and cordless fixed stations is a highly integrated circuit and realizes the analog front end functions needed in such systems. The circuit contains an A/D- and a D/A converter and adjustable gain stages. Connection of microphone and earpiece is possible with a minimum of external components.

Furthermore the device generates the reference voltages for the A/D converter the TXDA output voltage stabilization and the LCD-display-driver modules integrated in the DECT-Digital Circuit.

The reference voltages can be used together with external components and the PMB 27201, 27202, 27221, 27251, 27252 and 2728 for volume control of the ringer.

The device is fabricated using Siemens advanced ACMOS technology and will be available in a 24 pin package.

| Туре       | Package                   |

|------------|---------------------------|

| PMB 2920-S | P-SSOP-24-1 (Shrink, SMD) |

- High performance A/D- and D/A conversion

- Adjustable analog amplifiers

- Analog front end for direct connection of a handset mouth and earpiece

- · On-chip microphone supply generation

- Power savings power-down and MUTE functions

- Comparator for preprocessing of the demodulated receive signal

- Reference voltage generation for on-chip A/D- and D/A converters and for the DECT-Digital Circuit

- Support of volume control of the tone ringer signal

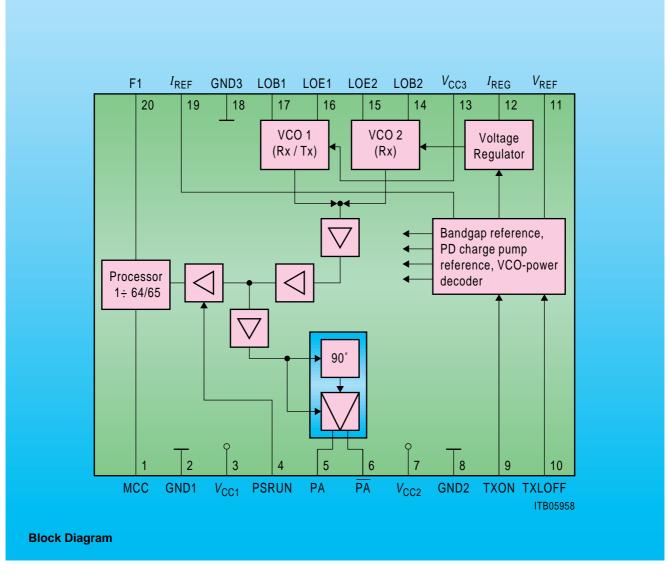

DECT Transmitter PMB 2220

## **General Description**

The PMB 2220 is a high speed analog bipolar IC and is one of the Siemens chipset for the Digital European Cordless Telephone. Combined with PLL (i.e. PMB 2306) and a power amplifier, the PMB 2220 device performs a complete DECT transmitter. Additionally the phase locked loop can be switched to receive mode and be used as a local oscillator for the receiver mixer of PMB 2420.

| Туре       | Package                   |

|------------|---------------------------|

| PMB 2220-S | P-SSOP-24-1 (Shrink, SMD) |

- Either single VCO operation (for receive and transmit) or dual VCO operation (one for receive and one for transmit) possible

- 64/65-prescaler on chip

- Frequency doubler for receive and transmit mode with balanced driver outputs

- Supply voltage regulator (with external pnp-transistor) for the two VCO's

- Power-down for the inactive VCO

- Current reference output for PLL charge pump to get constant lock-in time

- Wide power supple range 3.0 ... 5.5 V

DECT Receiver PMB 2420

## **General Description**

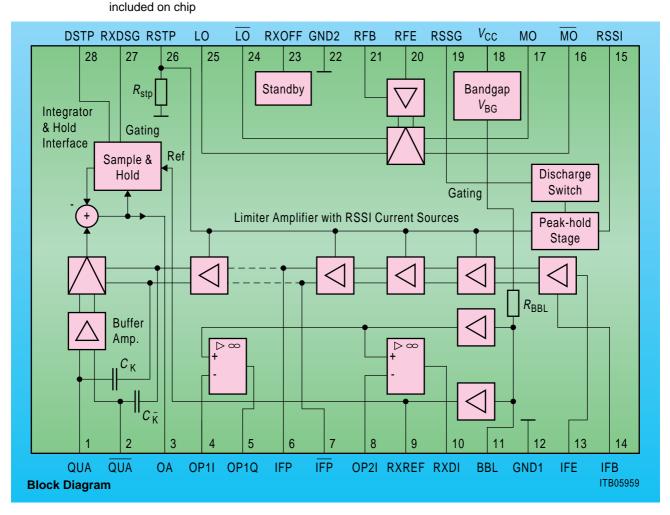

The PMB 2420 is a high speed analog bipolar IC and is one of the Siemens chipset for the Digital European Cordless Telephone specified by the DECT standard. All control inputs and the RSSI signal output match with the PMB 27201/2 and 27221 and 27251/2 and 2728 and 2727 digital circuits.

The IC operates as a heterodyne receiver using an intermediate frequency (IF) at 110 MHz. It consists of a mixer to downconvert the DECT-RF signal from 1.89 GHz to 110 MHz, a limiter amplifier, a field strength measurement unit (RSSI) with a peak-hold output, a coincidence demodulator, a sample-and-hold circuit for offset compensation and two operational amplifiers for basehand filtering.

#### **Features**

- Wide supply range 3.0 ... 5.5 V

- Single conversion solution;

advantages are: low supply current of total RF part no second IF image frequency and therefore insensitive to strong transmitters at FM radiofrequencies low total component count 1st mixer

| Туре       | Package                   |

|------------|---------------------------|

| PMB 2420-S | P-SSOP-28-1 (Shrink, SMD) |

- Single balanced RF mixer with current-saving open collector output on chip

- Limiter and RSSI dynamic range: 75 dB for IF between 40 MHz and 115 MHz

- RSSI output independent of supply voltage and temperature with 3 dB accuracy

- Peak-hold output for the RSSI signal, reset by the controller via RSSG

- Sample-and-hold control circuit for baseband threshold acquisition, loop opened and closed via RXDSG, offset compensation value is stored during standby mode

- Timing for RSSI and sample-and-hold determined by the controller

- Two operational amplifiers on chip for baseband filtering, included in sample and hold control loop

- Standby mode with reduced supply current

- · Balanced circuitry throughout the RF and IF

- · Parts to improve signal isolation

- Maybe applied as part of a complete DECT-chipset solution

# **RF-Building Blocks**

## Introduction

The era of the mobile communications has lead to an explosion in the variety of RF applications. Active for many years in this field with high performance IC solutions, Siemens RF ICs have found use in almost all wireless systems and are generally recognized for their high performance, functionality and cost-effectiveness.

Building upon the success of the PMB 2200 modulator family, the PMB 2401 receiver and Siemens PLLs (TBB 200/TBB 206/PMB 2306), the new B6HF 25 GHz bipolar technology will allow for a further increase in performance, 3-V lower current consumption as well as for higher frequencies. Starting with the new prescalers PMB 2313/2314, all the standard RF-building blocks will be gradually moved to B6HF.

#### **Product Overview**

| Туре          | Description                                    | Applications                                                                                     | Page |

|---------------|------------------------------------------------|--------------------------------------------------------------------------------------------------|------|

| Modulator/Tra | nsmitter ICs                                   |                                                                                                  |      |

| PMB 2200      | Direct Vector Modulator                        | Cellular (GSM, PDC, DAMPS, CDMA), WLAN, QPSK/QAM modulation up to 1 GHz                          | 37   |

| PMB 2201 B6HF | Direct Vector Modulator + Mixer, 2.7 V         | Cellular (GSM, PDC, DAMPS, CDMA), WLAN, QPSK/QAM modulation 0.8 GHz to 1.5 GHz                   | 38   |

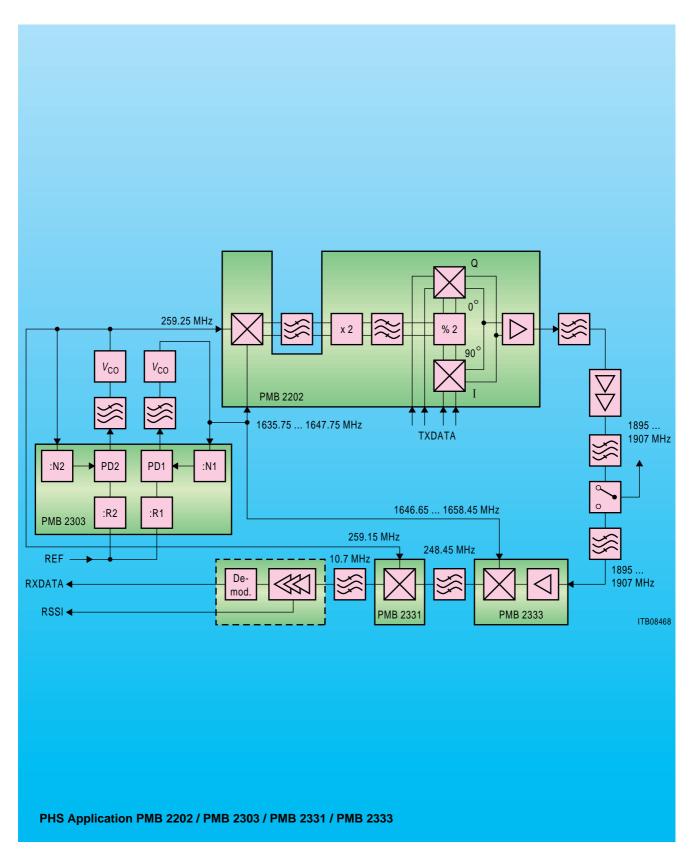

| PMB 2202 B6HF | Direct Vector Modulator + Mixer, 2.7 V         | Cellular (PCN, PCS, PDC), Cordless (PHS, WCPE) WLL, WLAN, QPSK/QAM modulation 1.5 GHz to 2.5 GHz | 38   |

| PMB 2205      | Direct Vector Modulator                        | Cellular (GSM, PCN, PCS, PDC, DAMPS, CDMA), Cordless (PHS, WCPE) WLL, WLAN, QPSK/QAM modulation  | 41   |

| PMB 2207 B6HF | Vector Modulator + Upconverter<br>Mixer, 2.7 V | Cellular (GSM, PCN, PCS, PDC, DAMPS, CDMA), Cordless (PHS) WCPE, WLL, WLAN, QPSK/QAM modulation  | 42   |

| PMB 2220      | DECT Transmitter, 3 V                          | Cordless (DECT), FSK modulation                                                                  | 33   |

| PMB 2240 B6HF | GSM Transmitter, 2.7 V                         | Cellular (GSM, PDC), QPSK/QAM modulation 0.8 GHz to 1.0 GHz                                      | 21   |

| PMB 2245 B6HF | PCN Transmitter, 2.7 V                         | Cellular (PCN, PCS), Cordless (PHS), QPSK/QAM modulation 1.65 GHz to 1.85 GHz                    | 21   |

| PMB 2247 B6HF | PCS Transmitter, 2.7 V                         | Cellular (PCN, PCS), Cordless (PHS), QPSK/QAM modulation 1.8 GHz to 1.95 GHz                     | 21   |

| Demodulator/l | Receiver ICs                                   |                                                                                                  |      |

| PMB 2401      | Receiver/Demodulator Circuit                   | Cellular (GSM, PDC, DAMPS, CDMA), WLAN, QPSK/QAM demodulation up to 0.9 GHz                      | 43   |

| PMB 2402      | Broadband Receiver/Vector<br>Demodulator       | CATV, Satellite (MSAT, VSAT), DS, WLL, WLAN                                                      | 44   |

| PMB 2405 B6HF | GSM Receiver, 2.7 V                            | Cellular (GSM, PDC, DAMPS), WLAN, QPSK/QAM demodulation up to 2.5 GHz                            | 23   |

| PMB 2407 B6HF | PCN/PCS Receiver, 2.7 V                        | Cellular (PCN, PCS), WLAN, QPSK/QAM demodulation up to 2.5 GHz                                   | 23   |

| PMB 2420      | DECT Receiver, 3 V                             | Cordless (DECT), FSK demodulation                                                                | 34   |

# RF-Building Blocks

## Product Overview (cont'd)

| Туре          | Description                                 | Applications                                                                                | Page |

|---------------|---------------------------------------------|---------------------------------------------------------------------------------------------|------|

| Frequency Sy  | nthesizer, Prescaler ICs                    |                                                                                             |      |

| PMB 2302 B6HF |                                             | All analog and digital systems as RF-, IF synthesizer up to 1.25 GHz                        | 45   |

| PMB 2303 B6HF | 2.5 GHz Dual PLL with Prescaler,<br>2.7 V   | All analog and digital systems as RF-, IF synthesizer up to 2.5 GHz                         | 45   |

| PMB 2306      | PLL Frequency Synthesizer                   | All analog and digital systems as RF-, IF synthesizer up to 220 MHz                         | 47   |

| PMB 2307      | PLL Frequency Synthesizer, 2.7 V            | All analog and digital systems as RF-, IF synthesizer up to 220 MHz                         | 47   |

| PMB 2308 B6HF | 1.25 GHz PLL with Prescaler, 2.7 V          | All analog and digital systems as RF-, IF synthesizer up to 1.25 GHz                        | 49   |

| PMB 2309 B6HF | 2.5 GHz PLL with Prescaler, 2.7 V           | All analog and digital systems as RF-, IF synthesizer up to 2.5 GHz                         | 49   |

| PMB 2313 B6HF | 1.1 GHz Prescaler :64/65 :128/129;<br>2.7 V | All analog and digital systems as part of RF- and IF synthesizer up to 1.1 GHz              | 51   |

| PMB 2314 B6HF | 2.1 GHz Prescaler :64/65 :128/129;<br>2.7 V | All analog and digital systems as part of RF- and IF synthesizer up to 2.1 GHz              | 51   |

| LNA/Mixer, Dr | iver/Mixer, Mixer ICs                       |                                                                                             |      |

| PMB 2330      | 2.0 GHz Mixer                               | All analog and digital systems as up- and downconversion mixer up to 2.0 GHz                | 52   |

| PMB 2331 B6HF | 2.0 GHz Mixer, 2.7 V                        | All analog and digital systems as up- and downconversion mixer up to 2.0 GHz                | 52   |

| PMB 2332 B6HF | 1.1 GHz LNA + Mixer, 2.7 V                  | All analog and digital systems as frontend-LNA and mixer up to 1.1 GHz                      | 53   |

| PMB 2333 B6HF | 3 GHz LNA/Driver + Mixer, 2.7 V             | All analog and digital systems as frontend-LNA or preamplifier-driver and mixer up to 3 GHz | 54   |

Direct Vector Modulator PMB 2200

## **General Description**

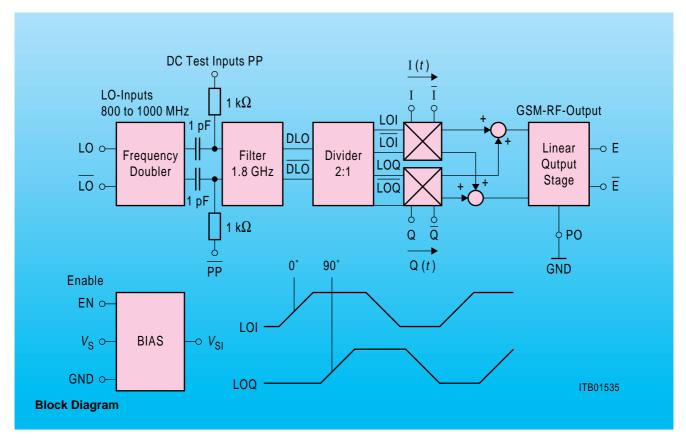

The PMB 2200 is a direct quadrature modulator for use in mobile communication equipment.

An external LO signal  $f_0$  is fed to the modulator input. This signal is first doubled and then bandpass filtered at  $2f_0$ . This frequency is the clock for a 2:1 divider. At the output of the divider orthogonal carriers are provided which are mixed with the baseband modulation signals by two multipliers. The outputs of the multipliers are added and amplified by a linear output stage.

The EN pin allows the modulator to be switched in power-down mode.

## **Applications**

- Vector modulated cellular and cordless systems: GSM, PDC, DAMPS, CDMA, WLAN, etc.

- Various modulation schemes, such as PM, PSK, FSK, QAM, QPSK, GMSK etc.

- Analog systems with FM- and AM modulation

- Space and power saving optimizations of existing discrete transmitter circuits

| Туре       | Package                   |

|------------|---------------------------|

| PMB 2200-T | P-DSO-20-1 (SMD)          |

| PMB 2200-S | P-SSOP-20-1 (Shrink, SMD) |

- · Direct modulation vector modulator

- · Linear modulating inputs

- Symmetrical circuitry

- Wide LO-frequency range 0.8 GHz to 1.0 GHz

- Generation of orthogonal carriers without external elements and without trimming

- 35 dB carrier rejection, 42 dB SSB rejection

- · 42 dB rejection of third order products

- 0 dBm linear output power

- Modulation frequency range 0 to 400 MHz

- Power-down mode

- P-DSO-20 or P-SSOP-20 package

- Temperature range 25 °C to 85 °C

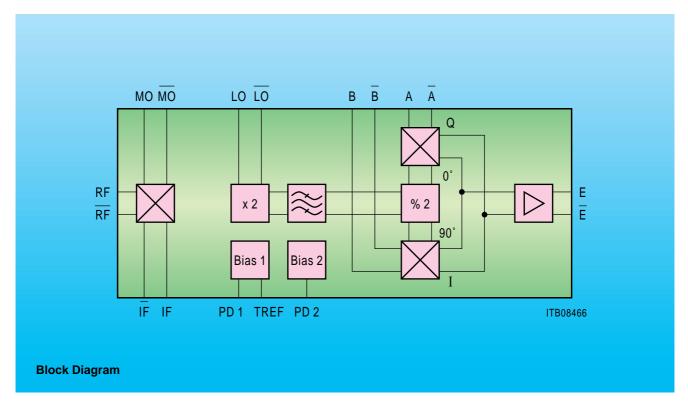

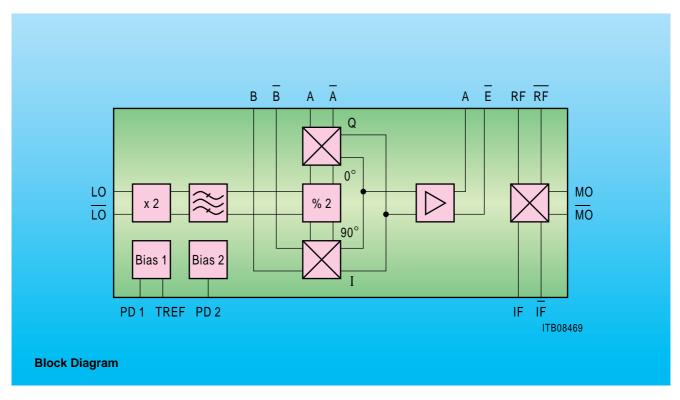

The PMB 2201, 2202 family is a direct quadrature modulator and double balanced mixer. It is fabricated using Siemens B6HF silicon bipolar process. In a typical application the wanted mixer output product is bandpass filtered and then fed to the modulator LO input. The mixer may also be used to upconvert the modulator output signal to higher frequencies up to 2.5 GHz.

The modulator generates two orthogonal carriers which are mixed with the baseband modulation signals by two multipliers. The outputs of the multipliers are added and amplified by a linear output stage. The modulator and the mixer have separate power supplies and grounds. They can be powered down independently.

#### **Applications**

- Vector modulated cellular and cordless systems: PMB 2201: GSM, PDC, DAMPS, CDMA, WLAN, PMB 2202: PCN, PCS, PDC, PHS, WCPE, WLL, WLAN, etc.

- Various modulation schemes, such as PM, PSK, FSK, QAM, QPSK, GMSK etc.

- Analog systems with FM- and AM modulation

- Space and power saving optimizations of existing discrete transmitter circuits

| Туре       | Package            |

|------------|--------------------|

| PMB 2201-R | P-TSSOP-24-1 (SMD) |

| PMB 2202-R | P-TSSOP-24-1 (SMD) |

- · Direct modulation vector modulator

- Wide LO-frequency range PMB 2201: 0.8 GHz to 1.5 GHz PMB 2201: 1.5 GHz to 2.5 GHz

- Generation of orthogonal carriers without external elements and without trimming

- 35-dB carrier rejection, 40-dB SSB rejection

- 42-dB rejection of third order products

- · 0-dBm modulator output power

- Independent double balanced Gilbert cell mixer

- RF- and IF-frequency range from DC to 2.5 GHz

- · Low noise figure, high conversion gain

- Supply voltage range from 2.7 V to 5.5 V

- Low power consumption

- Power-down mode

- P-TSSOP-24 package

- Temperature range 30 °C to 85 °C

Direct Vector Modulator PMB 2205

#### **General Description**

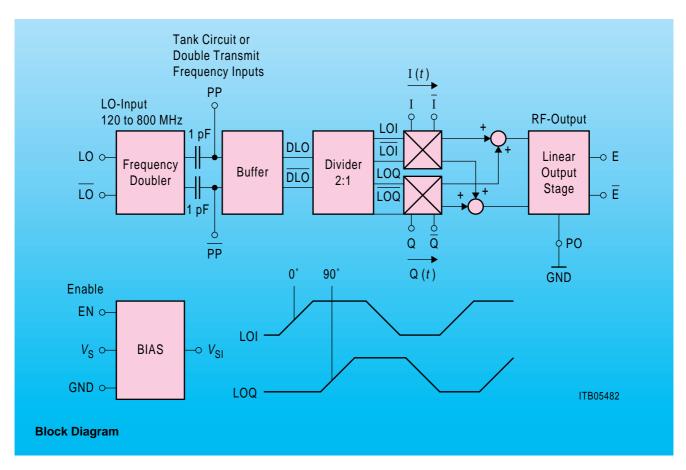

The PMB 2205 is a direct quadrature modulator for use in mobile communication equipment.

An external LO signal  $f_0$  is fed to the modulator input. This signal is first doubled and then bandpass filtered at  $2f_0$ . The filter may be realized by an external tank circuit. Alternatively, a local oscillator operating at  $2f_0$  may be connected to the divider input. This signal is the clock for a 2:1 divider. At the output of the divider orthogonal carriers are provided which are mixed with the baseband modulation signals by two multipliers. The outputs of the multipliers are added and amplified by a linear output stage.

The EN pin allows the modulator to be switched in power-down mode.

# **Applications**

- Vector modulated cellular and cordless systems: GSM, PCN, PCS, PDC, DAMPS, CDMA, WLAN, etc.

- Various modulation schemes, such as PM, PSK, FSK, QAM, QPSK, GMSK etc.

- Analog systems with FM- and AM modulation

- Space and power saving optimizations of existing discrete transmitter circuits

| Туре       | Package                  |

|------------|--------------------------|

| PMB 2205-T | P-DSO-20-1 (SMD)         |

| PMB 2205-S | P-SSOP-20-1 (Shrink SMD) |

- · Direct modulation vector modulator

- · Linear modulating inputs

- Symmetrical circuitry

- Wide LO-frequency range 120 MHz to 800 MHz

- LO operation alternatively at transmit frequency or double transmit frequency

- Generation of orthogonal carriers within a wide frequency range

- 35 dB carrier rejection, 42 dB SSB rejection

- 42 dB rejection of third order products

- 0 dBm linear output power

- Modulation frequency range 0 to 400 MHz

- Power-down mode

- P-DSO-20 or P-SSOP-20 package

- Temperature range 25 °C to 85 °C

The PMB 2207 is a direct quadrature modulator and double balanced mixer. It is fabricated using Siemens B6HF silicon bipolar process. In a typical application the modulator output signal is bandpass filtered and then fed to the mixer input for upconversion.

An external LO signal is fed to the modulator input. The modulator generates two orthogonal carriers which are mixed with the baseband modulation signals by two multipliers. The outputs of the multipliers are added and amplified by a linear output stage. The modulator and the mixer have separate power supplies and grounds. They can be powered down independently.

#### **Applications**

- Vector modulated cellular and cordless systems: GSM, PCN, PCS, PDC, DAMPS, CDMA, PHS, WCPE, WLL, WLAN, etc.

- Various modulation schemes, such as PM, PSK, FSK, QAM, QPSK, GMSK etc.

- Analog systems with FM- and AM modulation

- Space and power saving optimizations of existing discrete transmitter circuits

| Туре       | Package                    |

|------------|----------------------------|

| PMB 2207-R | P-TSSOP-24-1 (Shrink, SMD) |

- Vector modulator with upconverter mixer

- Wide LO-frequency range from 80 MHz to 800 MHz

- Mixer RF-frequency range up to 2.5 GHz

- Generation of orthogonal carriers without external elements and without trimming

- 35 dB carrier rejection, 40 dB SSB rejection

- 42 dB rejection of third order products

- 0 dBm modulator output power

- Independent double balanced Gilbert cell mixer

- IF-frequency range from DC to 2.5 GHz

- Low noise figure, high conversion gain

- Supply voltage range from 2.7 V to 5.5 V

- · Power-down mode

- P-TSSOP-24 package

- Temperature range 30 °C to 85 °C

# **Preliminary Data**

# **General Description**

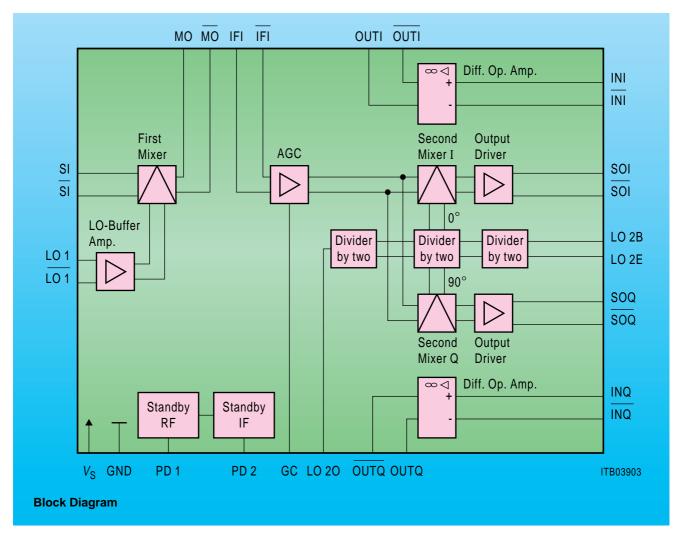

The PMB 2401 is a single-chip double-conversion heterodyne PM receiver with phase shifting circuitry for the I/Q-phase demodulation on chip. It also includes the second local oscillator, a gain controlled 2nd IF amplifier, 2 differential operational amplifiers for audio purposes and power-down circuitry.

The PMB 2401 is designed for digital mobile telephones according the GSM standard and other digital systems.

# **Application**

- · Digital mobile cellular systems as GSM, PDC, DAMPS

- Various demodulation schemes, such as PM, PSK, FSK, QAM, QPSK, GMSK

- Space and power saving optimizations of existing discrete demodulator circuits

| Туре       | Package                   |

|------------|---------------------------|

| PMB 2401-T | P-DSO-28-1 (SMD)          |

| PMB 2401-S | P-SSOP-28-1 (Shrink, SMD) |

- · Heterodyne receiver with demodulator

- Down mixing from 900-MHz receiver band to the base band

- Demodulation and generation of I/Q components

- Lower mixer noise to 10 dB (SSB)

- High intercept point + 2 dBm

- Integrated phase shifter for I/Q demodulator

- 82-dB AGC range

- · On-chip second LO oscillator with external tuning circuit

- · Two differential operational amplifiers

- Low power consumption due to highly flexible power-down capability

- Wide input frequency range up to 1 GHz

- Wide IF range from 35 MHz to 100 MHz

- P-DSO-28 package, P-SSOP-28 (Shrink)

- Temperature range 25 °C to 85 °C

The PMB 2402 is a single-chip single-conversion heterodyne receiver with phase shifting circuitry for the I/Q phase local baseband demodulation on chip. It also includes the second oscillator, a gain controlled second IF amplifier, two differential operational amplifiers for baseband fitering purposes and power-down circuitry.

The PMB 2402 is designed for digital mobile telephones according to the GSM standard and other digital systems.

#### **Applications**

- · Digital wideband systems as CATV, Satellite, DBS, WLAN

- Various demodulation schemes, such as PM PSK, FSK, QAM, QPSK, GM

- Space and power saving optimization of existing discrete demodulator circuit

| Туре       | Package          |

|------------|------------------|

| PMB 2402-S | P-DSO-28-1 (SMD) |

- · Heterodyne receiver with demodulators

- Down mixing from 900 MHz receiver band to the base band

- Demodulation and generation of I/Q-baseband components

- Low mixer noise 10 dB (SSB)

- Input high intercept point + 2 dBm

- Integrated 0° and 90° phase shifter

- 82 dB AGC range

- · On-chip second LO oscillator with external tuning circuit

- Low power consumption due to highly flexible power-down capability

- Wide input frequency range up to 1 GHz

- Wide IF range from 35 MHz to 100 MHz

- · Wide output frequency range up to 13.5 MHz

- Temperature range 25 °C to 85 °C

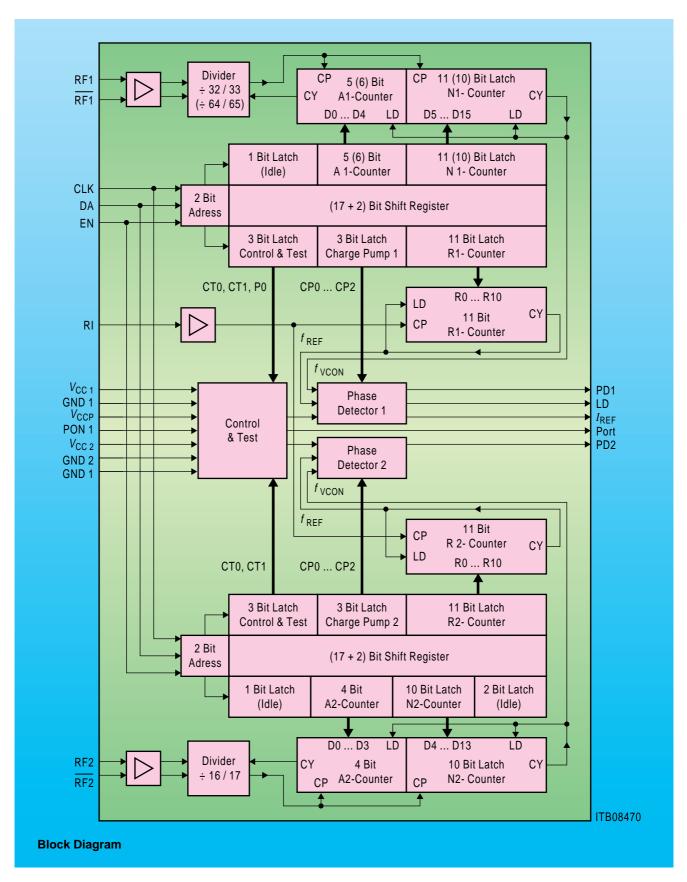

The PMB 2302, PMB 2303 are single chip dual Phase Locked Loop (PLL) synthesizers with programmable frequency dividers for use in mobile communication equipment. It is fabricated using Siemens B6HF silicon bipolar process.

The circuit consists of high speed dual modulus dividers, shift registers, programmable counters (2 A-, 2 N- and 2 R-counters), phase detectors with charge pump and a control logic block.

Since one of the high speed dual modulus dividers is able to handle frequencies of up to 1.25 GHz (2.5 GHz), there is no need to add a dedicated external prescaler. The second dual modulus divider handles frequencies up to 500 MHz. The switching signals for the dividing ratios are generated by the corresponding A-counters.

The A-counter and the N-down-counter are programmable via the 3-wire bus. They are clocked by the dual modulus divider output signals. The carry outputs of the N-counters are connected to the frequency inputs of the corresponding phase detectors and are controlling the loading of the programmed A-/N-counter start values.

The two 11 bit R-counters are also programmable and are serving as reference frequency dividers. Their carry outputs are connected to the corresponding reference frequency inputs of the phase detector and are controlling the loading of the programmed counter start values.

The phase detectors are of PFD-type (phase and frequency sensitive). They have a linear output characteristic in the  $0^{\circ}$  phase error region.

The control logic handles phase detectors output polarity, charge pump output currents and software-generated power-on (all circuit parts except the shift registers and data latches).

# **Applications**

All mobile communication analog and digital systems as RF-and IF synthesizers

| Туре       | Package                    |  |

|------------|----------------------------|--|

| PMB 2302-R | P-TSSOP-20-1 (Shrink, SMD) |  |

| PMB 2303-R | P-TSSOP-20-1 (Shrink, SMD) |  |

#### **Features**

- · Integrated prescaler

- · Low operating current

- · Different power-down modes

- High input sensitivity, high input frequency

- Two fast phase detectors without dead zone

- Linearization of the phase detector output by current sources

- · Large dividing ratios for small channel spacing

| • | PLL1       | PMB 2302   | PMB 2303   |

|---|------------|------------|------------|

|   | max. freq. | 1.25 GHz   | 2.5 GHz    |

|   | prescaler: | :32/:33    | :64/:65    |

|   | A1-counter | 0 to 31    | 0 to 63    |

|   | N1-counter | 32 to 2047 | 64 to 1023 |

|   | R1-counter | 3 to 2047  | 3 to 2047  |

| • | PLL2       | PMB 2302   | PMB 2303   |

|   | max. freq. | 500 MHz    | 500 MHz    |

|   | prescaler: | :16/:17    | :16/:17    |

|   | A2-counter | 0 to 15    | 0 to 15    |

|   | N2-counter | 16 to 1023 | 16 to 1023 |

Serial control (3-wire bus: data, clock, enable) for fast programming (f<sub>max</sub> = 10 MHz)

3 to 2047

Switchable polarity and phase detector current programmable

3 to 2047

- 1 port output (TTL push-pull)

- External current setting for phase detector outputs

- Lock detect output with gated pulse (quasi digital lock detect)

- Operating voltage 2.7 V to 5.5 V

- P-TSSOP-20 package

R2-counter

• Temperature range – 30 °C to 85 °C

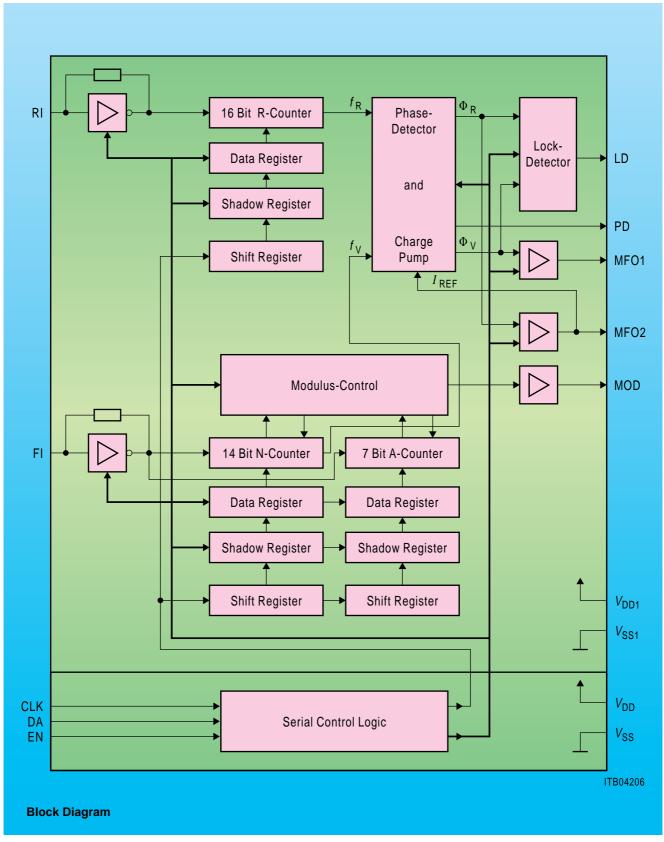

The PMB 2306, PMB 2307 PLL are high speed CMOS ICs are especially designed for use in battery-powered radio equipment and mobile telephones. The intended application will be in GSM, PCN, DECT and other digital mobile systems. The wide range of dividing ratios also allows application in analog systems.

The circuit consists of a reference-, A- and N-counter, a dual-modulus-control logic, a phase detector with charge pump and a serial control logic. The setting of the operating mode and the selection of the counter ratios is done serially at the ports CLK, DA and EN.

The operating modes allow the selection of single or dual operation, asynchronous or synchronous data acquisition, 4 different antibacklash-impulse times, 8 different PD-output current modes, polarity setting of the PD-output signal, adjustment of the trigger-edge of the MOD-output signal, 2 standby modes and the control of the multifunction outputs MFO1 and MFO2.

The reference frequency is applied at the RI input and scaled down by the R-counter. Its maximum value is 50 MHz. The VCO frequency is applied at the FI input and scaled down by the N- or N/A-counter according to single or dual-mode operation. The maximum value at FI is 220 MHz at single-, and 65 MHz at dual-mode operation.

The phase detector is frequency and phase sensitive. It produces a phase detector signal with adjustable antibacklash impulses in order to prevent a dead zone at very small phase deviations. Phase differences smaller than 100 ps can therefore be resolved.

Programming of the IC is done by a serial data control. The contents of the messages are assigned to the functional units according to the destination address. Single or dual-mode operation as well as asynchronous or synchronous data acquisition is set by status 2 and should therefore precede the programming of the counters.

The PMB 2306/PMB 2307 offer the possibility of synchronous data acquisition to avoid error signals at the phase detector due to non-corresponding dividing factors in the counters produced by asynchronous loading.

Synchronous programming guarantees control during changes of frequency or channel. That means that the state of the phase detector or the phase difference is kept maintained, and in case of "lock in", the control process starts with the phase difference "zero".

Synchronous transmission is particularly advantageous when large transfers in channel are to be made in a specific short transient recovery time. For this purpose a larger reference frequency is switched to in order to achieve rapid-"rough"-transient response, increasing the bandwidth of the loop at the time. When reaching the "quasi lock-in" state, the reference frequency is switched back to its original values.

| Туре       | Package                    |

|------------|----------------------------|

| PMB 2306-T | P-DSO-14-1 (SMD)           |

| PMB 2306-R | P-TSSOP-16-1 (Shrink, SMD) |

| PMB 2307-R | P-TSSOP-16-1 (Shrink, SMD) |

Adjustment to the "actual" value then takes place with the usual transient response as for small transfers in channel. The synchronous transmission ensures that no additional phase errors arise due to the change of reference frequencies.

The PMB 2306/2307 has two standby modes (standby1, 2) to reduce the current consumption.

- Standby1 switches off the whole circuit, the current consumption is reduced to below 1 μA.

- Standby2 switches off the counters, the charge pump and the outputs, only the preamplifiers stay active.

The standby modes do not affect the port output signal. For the influence on the other output signals see standby table.

- · Low operating current consumption

- Low operating voltage PMB 2306: 3 V to 5.5 V PMB 2307: 2.7 V to 5.5 V

- · High input sensitivity, high input frequencies (220 MHz)

- · Extremely fast phase detector without dead zone

- Linearization of the phase detector output by current sources

- Synchronous programming of the counters (N-, N/A-, R-counters) and system parameters

- Fast modulus switchover for 65-MHz operation

- Switchable modulus trigger edge

- Large dividing ratios for small channel spacing

- A-scaler 0 to 127

- N-scaler 3 to 16380

- R-scaler 3 to 65535

- Serial control (3-wire bus: data, clock, enable) for fast programming ( $f_{\rm max} \sim$  5 MHz)

- Switchable polarity and rate of trimming rise of the phase detector

- 2 multifunction outputs

- Digital phase detector output signals (e.g. for external charge pump)

- $f_{\rm rn}, f_{\rm vn}$  outputs of the R- and N-scalers

- Port 1 output (e.g. for standby of the prescaler)

- · External current setting for PD output

- Lock detect output with gated antibacklash pulse (quasi digital lock detect)

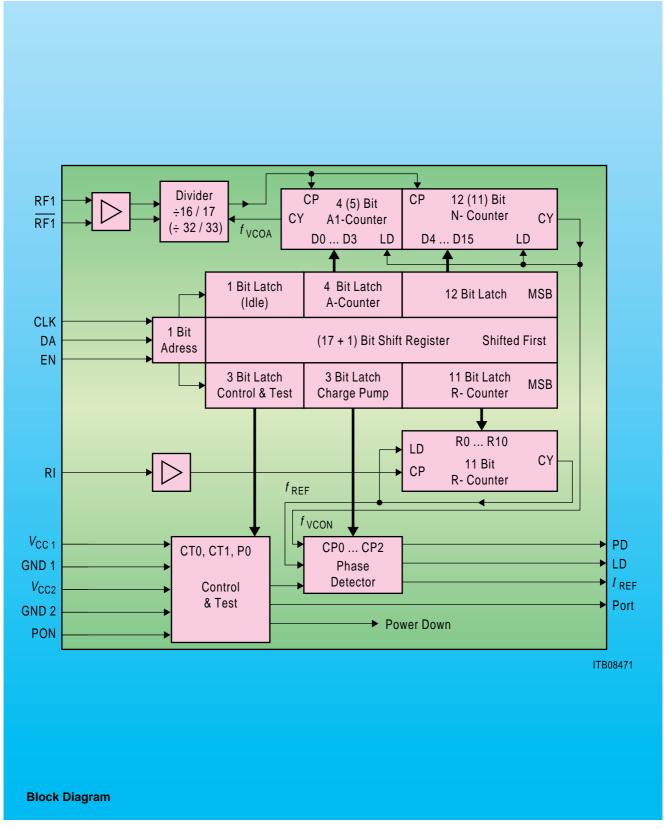

The PMB 2308, PMB 2309 are Phase Locked Loop (PLL) synthesizers with programmable frequency dividers for use in mobile communication equipment. It is fabricated using Siemens B6HF silicon bipolar process.

The circuit consists of high speed dual modulus divider, shift register, programmable counter (A-, N- and R-counter), phase detector with charge pump and a control logic block.

Since the high speed dual modulus divider is able to handle frequencies of up to 1.25 (2.5) GHz, there is no need to add a dedicated external prescaler. The switching signals for the dividing ratio 16/17 (32/33) is generated by the A-counter.

The A-counter and the N-down-counter are programmable via the 3-wire bus. They are clocked by the dual modulus divider output signal. The carry output of the N-counter is connected to the frequency input of the phase detector and is controlling the loading of the programmed A-/N-counter start values.

The 11 bit R-counter is also programmable and is serving as reference frequency divider. Its carry output is connected to the reference frequency input of the phase detector and is controlling the loading of the programmed counter start value.

The phase detector is of PFD-type (phase and frequency sensitive). It has a linear output characteristic in the  $0^{\circ}$  phase error region.

The control logic handles phase detector output polarity, charge pump output current and software-generated power-down (all circuit parts except the shift registers and data latches).

#### **Applications**

All mobile communication analog and digital systems as RFand IF synthesizers

| Туре       | Package                    |

|------------|----------------------------|

| PMB 2308-R | P-TSSOP-16-1 (Shrink, SMD) |

| PMB 2309-R | P-TSSOP-16-1 (Shrink, SMD) |

- · Integrated prescaler

- · Low operating current

- · Different power-down modes

- · High input sensitivity, high input frequency

- · Fast phase detector without dead zone

- Linearization of the phase detector output by current sources

- · Large dividing ratios for small channel spacing

| • | PLL        | PMB 2308   | PMB 2309   |

|---|------------|------------|------------|

|   | max. freq. | 1.25 GHz   | 2.5 GHz    |

|   | prescaler: | :16/:17    | :32/:33    |

|   | A-counter  | 0 to 15    | 0 to 31    |

|   | N-counter  | 16 to 4095 | 32 to 2047 |

|   | R-counter  | 3 to 2047  | 3 to 2047  |

- Serial control (3-wire bus: data, clock, enable) for fast programming (f<sub>max</sub> = 10 MHz)

- Switchable polarity and phase detector current programmable

- 1 port output (TTL push-pull)

- External current setting for phase detector output

- Lock detect output with gated pulse (quasi-digital lock detect)

- Operating voltage 2.7 V to 5.5 V

- P-TSSOP-16 package

- Temperature range 30 °C to 85 °C

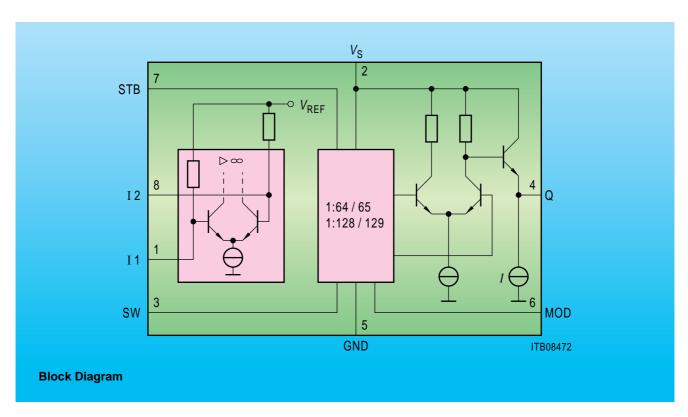

The PMB 2313, PMB 2314 prescaler family is designed for use in mobile radio communication devices. It is fabricated using Siemens B6HF silicon bipolar process. Due to its low power consumption, low supply voltage down to 2.7 V and low phase noise generation it is suitable for the use in various battery powered handheld systems.

The balanced differential inputs of the IC may be connected either symmetrically or asymmetrically.

Depending on the logic level at SW input the dividing ratio is fixed to 1:64/65 or 1:128/129. The MOD input determines whether modulus 1/n or 1/(n+1) (n=64 or n=128, according to SW level) is active.

The IC can be switched to a low-power standby mode (input STB). The MOD input is TTL/CMOS compatible. The emitter follower output is CMOS compatible.

#### **Applications**

All analog and digital mobile communication systems as part of RF- and IF synthesizers.

| Туре       | Package         |

|------------|-----------------|

| PMB 2313-T | P-DSO-8-1 (SMD) |

| PMB 2314-T | P-DSO-8-1 (SMD) |

- · Low operating current

- Power-down mode

- High input sensitivity

- Wide input frequency range PMB 2313: 0.1 GHz to 1.1 GHz PMB 2314: 0.1 GHz to 2.1 GHz

- · Low noise

- Operating voltage 2.7 V to 5.5 V

- P-DSO-8 package

- Temperature range 30 °C to 85 °C

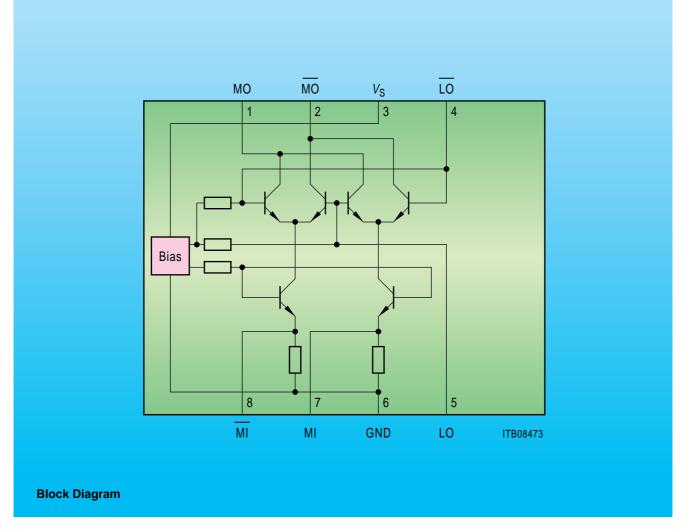

The PMB 2330, PMB 2331 are low power, double balanced up-/downconversion Gilbert cell mixers up to 2.0 GHz. The PMB 2331 is fabricated using Siemens B6HF silicon bipolar process.

Differential signals and symmetrical circuits are used throughout the mixer. The mixer input can be used in balanced or unbalanced configuration. The mixer outputs are high impedance open collector outputs. The adjustable mixer current allows to improve the mixer performance.

An internal bias driver generates supply voltage and temperature compensated reference voltages.

# **Applications**

All analog and digital mobile communication systems as up-/downconverter mixer.

| Туре       | Package         |

|------------|-----------------|

| PMB 2330-T | P-DSO-8-1 (SMD) |

| PMB 2331-T | P-DSO-8-1 (SMD) |

- · Low operating current

- Low operating voltage: PMB 2330: 3.0 V to 7.0 V PMB 2331: 2.7 V to 5.5 V

- · Power-down mode

- RF- and IF-frequency range up to 2.0 GHz

- · Mixer current adjustable

- · Low noise figure

- High conversion gain

- Excellent intercept performance

- · Good suppression of input signals at output

- · High isolation values

- Few external components

- P-DSO-8 package

- Temperature range 30 °C to 85 °C

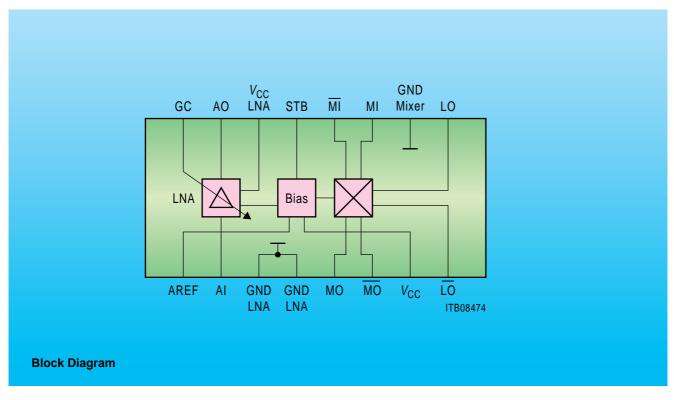

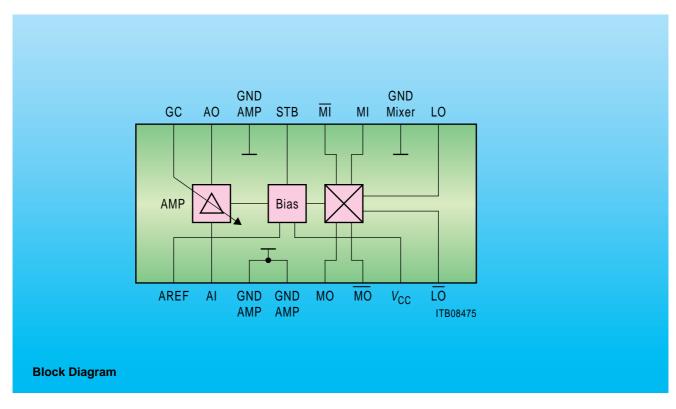

1.1-GHz LNA + Mixer PMB 2332 B6HF

#### **General Description**

The PMB 2332 is a low noise amplifier (LNA) up to 1.1 GHz and double balanced mixer up to 3 GHz for use in mobile communication equipment. It is fabricated using Siemens B6HF silicon bipolar process.

The amplified signal is external available for further use at output AO. The DC level at GC allows to switch the LNA gain (on/off: 20 dB).

The mixer is a general purpose up- and downconversion Gilbert cell mixer. Differential signals and symmetrical circuits are used throughout the mixer. The mixer input can be used in balanced or unbalanced configuration. The mixer outputs are high impedance open collector outputs. The adjustable mixer current allows to improve the mixer performance.

An internal bias driver generates supply voltage and temperature compensated reference voltages. The STB pin allows the mixer and bandgap part of the IC to be switched in power-down mode.

# **Applications**

All analog and digital mobile communication systems as frontend-LNA and up-/ downconverter mixer.

| Туре       | Package                    |

|------------|----------------------------|

| PMB 2332-R | P-TSSOP-16-1 (Shrink, SMD) |

- · Low operating current

- · Power-down mode

- LNA frequency range up to 1.1 GHz

- Switchable LNA gain

- High LNA gain (typ. 20 dB at 900 MHz)

- Low LNA noise figure (typ. 1.5 dB at 900 MHz)

- · Double balanced mixer up to 3 GHz with high gain

- Excellent intercept performance

- · High isolation values

- Few external components

- Operating voltage 2.7 V to 5.5 V

- P-TSSOP-16 package

- Temperature range 30 °C to 85 °C