### FEATURES

- Supports MNP2-5 and CCITT V.42bis (SC11091), CCITT V.42 (SC11091/SC11095)

- ☐ Supports SDLC, HDLC, Bisync, Monosync & Async protocols in software

- ☐ Internal Serial Synchronous Communication Circuit

- ☐ Can address 64K ROM, 32K RAM

- ☐ Selectable Clock Frequency

- ☐ 16x16 multiply in 2µs☐ Low Power Power-down (Standby) Mode

- ☐ Supports asymmetric protocols

- □ Reverse compatible with SC11011, 21, 61

- Direct interface to SC11006, SC11024, SC11026, SC11044, SC11046, SC11054 Modems

- ☐ 384 Byte internal RAM

- ☐ 256 byte Internal ROM

- ☐ Power Down mode indicator on PD pin

- ☐ Built-in UART with 80ns data access time in parallel mode

- □ Direct IBM PC bus interface□ Selectable IORDY Interface

- □ CMOS technology

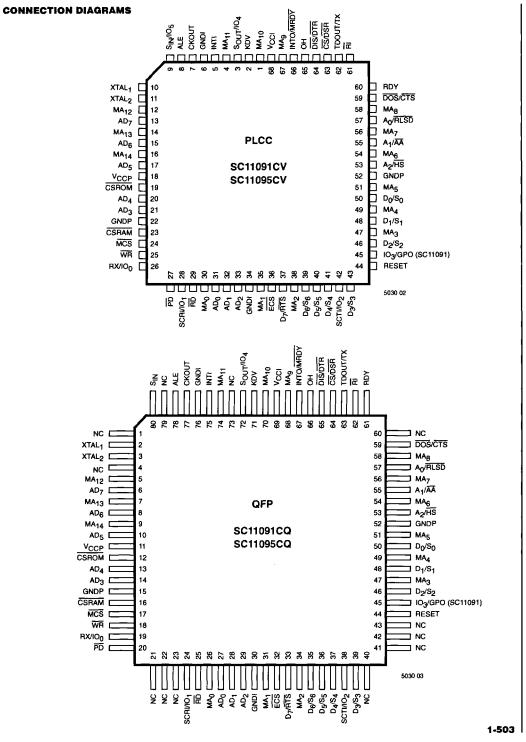

SC11091CV

SC11095CV

**68-PIN PLCC PACKAGE**

SC11091CQ SC11095CQ

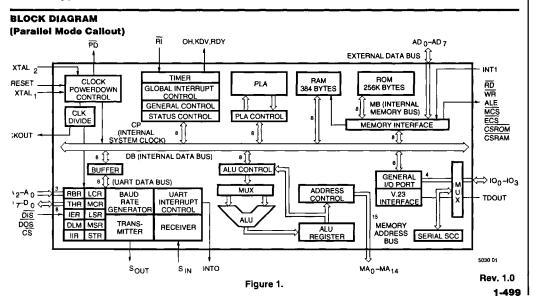

### **GENERAL DESCRIPTION**

The UMAC is a high-speed MAC designed to perform the DSP and control functions for modems operating under data compression modes. The SC11091 is capable of supporting V.42bis, V.42, MNP2–5, as well as V.22bis. The SC11095 is functionally similar to the SC11091 except that it does not support V.42bis. (Complete firmware package and licensing information are available from Sierra.) The UMAC supports all of Sierra's

V.22bis modem devices: SC11044, SC11046 and SC11054 for Sendfax™ modems; SC11006 and SC11024 for standard modems; SC11026 for Quatro modems; and SK9698 for S/R Fax modems.

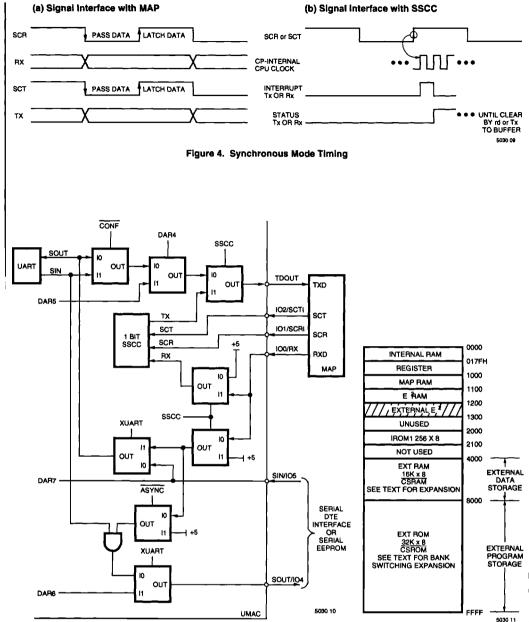

Besides preserving the MAC (Modem Advanced Controller—SC11011) and Big MAC (SC11021 series) structure, the UMAC includes a one bit Serial Synchronous Communication Circuit

(SSCC) which, with firmware support, eliminates the need for an external SSCC to support HDLC and other synchronous protocols.

### **DESCRIPTION** (continued)

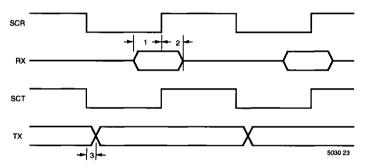

The SSCC is implemented as a 1 bit input, 1 bit output, 1 receive clock and 1 transmit clock. This SSCC can interrupt the CPU each time a bit is received or when a bit has been transmitted.

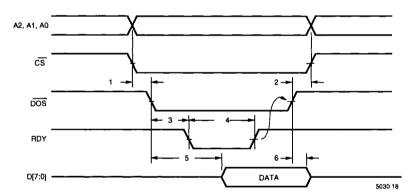

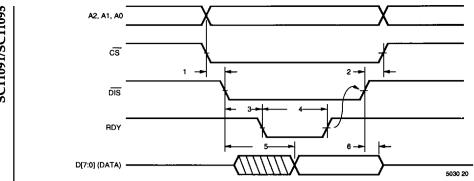

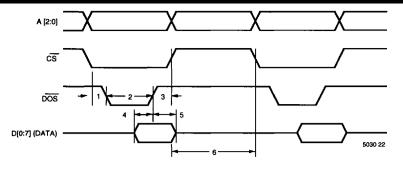

The SC11091/SC11095 contains a 16C450 compatible UART which can be configured to provide a serial or parallel DTE interface. In the RDY mode, the UMAC provides an I/O channel ready

(RDY) signal to insert wait states in the PC bus read/write cycle to allow reliable data transfer with any speed bus. This can be changed by a register setting to a no-wait-state-mode. This provides a high speed UART interface, with a minimum read time of 80 ns. On original power up reset, the default mode is active RDY mode. When RDY is deselected, the IORDY pin is tristated and the parallel interface timing is speeded up.

#### **APPLICATIONS**

- □ V.22bis modem with V.42bis compression(SC11091)

□ MNP2-5 modems

□ Class 2 Fax & Data modems

□ Feature rich International modems

- ☐ Upgrade from SC11011, 11021, 11061

- ☐ Synchronous data links

#### PIN DESCRIPTIONS

|                                  | PIN N                                | JMBER_                               |                                                                                                                                                                                                    |

|----------------------------------|--------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN NAME                         | PLCC                                 | QFP                                  | DESCRIPTION                                                                                                                                                                                        |

|                                  |                                      | 1.                                   | Parallel Systems Interface (to PC bus)                                                                                                                                                             |

| A <sub>0</sub> -A <sub>2</sub>   | 57, 55, 53                           | 57, 55, 53                           | Address lines for UART register select, input, TTL.                                                                                                                                                |

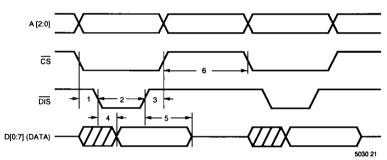

| CS                               | 63                                   | 64                                   | Chip select, active low, input, TTL.                                                                                                                                                               |

| D <sub>0</sub> -D <sub>7</sub>   | 50, 48, 46,<br>43, 41, 40,<br>39, 37 | 50, 48, 46,<br>39, 37, 36,<br>35, 33 | 8-bit data port, input-output, TTL.                                                                                                                                                                |

| DIS                              | 64                                   | 65                                   | Data in strobe (PC reads from UART registers), active low, input, TTL.                                                                                                                             |

| DOS                              | 59                                   | 59                                   | Data out strobe (PC writes into UART registers), active low, input, TTL.                                                                                                                           |

| INTO                             | 66                                   | 67                                   | Interrupt, output, CMOS/TTL. Tristate™                                                                                                                                                             |

| RDY                              | 60 61                                |                                      | Output, ready signal for high speed PC-AT interface.                                                                                                                                               |

|                                  |                                      | II. RS-                              | 232 (Data Set Mode) and Display Interface                                                                                                                                                          |

| ĀĀ                               | 55                                   | 55                                   | Automatic answer enable indicator (low), output, TTL/CMOS.                                                                                                                                         |

| CTS                              | 59                                   | 59                                   | Clear to send, output, TTL/CMOS.                                                                                                                                                                   |

| DSR                              | 63                                   | 64                                   | Data set ready, output, TTL/CMOS.                                                                                                                                                                  |

| DTR                              | 64                                   | 65                                   | Data terminal ready, input, TTL.                                                                                                                                                                   |

| HS                               | 53                                   | 53                                   | High speed indicator, output, TTL/CMOS. Low when operating at 2400 bps rate. High otherwise.                                                                                                       |

| MRDY                             | 66                                   | 67                                   | Modem ready.                                                                                                                                                                                       |

| RLSD                             | 57                                   | 57                                   | Carrier detect, output, TTL/CMOS.                                                                                                                                                                  |

| RTS                              | 37                                   | 33                                   | Request to send, input, TTL.                                                                                                                                                                       |

|                                  |                                      |                                      | III. MAP Interface                                                                                                                                                                                 |

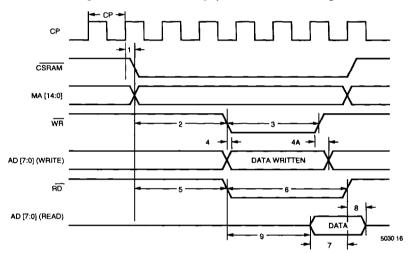

| AD <sub>0</sub> -AD <sub>7</sub> | 31–33, 21,<br>20, 17, 15, 13         | 27-29, 14,<br>13, 10, 8, 6           | 8-bit bidirectional multiplexed address/databus, CMOS.                                                                                                                                             |

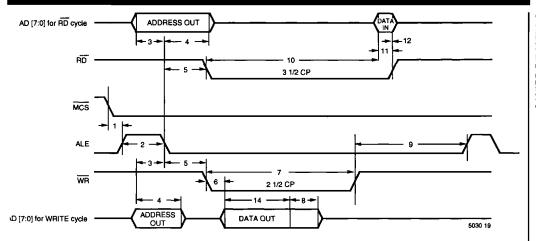

| ALE                              | 8                                    | 78                                   | Address Latch Enable, output, CMOS/TTL, the address on ECS, MCS, AD $_{7}$ -AD $_{0}$ are valid at the falling edge of this normally low pulse.                                                    |

| ECS                              | 36                                   | 32                                   | External EERAM chip select or for second MAP chip select, output, TTL/CMOS, addressing space is from 1100H to 11FFH. When used for ROM expanded mode, the ECS functions as the second chip select. |

Tristate is a trademark of National Semiconductor.

| PIN DESCRI                         | PTIONS (co                                                           | ntinued)                                                            |                                                                                                                                                                                   |  |  |

|------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                    | PIN N                                                                | UMBER                                                               |                                                                                                                                                                                   |  |  |

| PIN NAME                           | PLCC                                                                 | QFP                                                                 | DESCRIPTION                                                                                                                                                                       |  |  |

| INTI                               | 5                                                                    | 75                                                                  | Interrupt input, TTL; interrupt received from the MAP at 600 Hz. Interrupt is detected when this pin has a low to high transition. The line has to stay high for at least 200 ns. |  |  |

| MCS                                | 24                                                                   | 17                                                                  | Map chip select for MAP interface, output, TTL/CMOS, addressing space is from 1000H to 10FFH and 1200H to 12FFH                                                                   |  |  |

| RD                                 | 29                                                                   | 25                                                                  | RAM read, output, CMOS/TTL, normally high, data on $AD_7$ - $AD_0$ must be valid at the rising edge of this pulse.                                                                |  |  |

| S <sub>IN</sub>                    | 9                                                                    | 80                                                                  | Received data, input; TTL. Serial data received from the MAP.                                                                                                                     |  |  |

| S <sub>OUT</sub>                   | 3                                                                    | 72                                                                  | Transmit data, output, CMOS/TTL. Serial data to be transmitted by the modem.                                                                                                      |  |  |

| WR                                 | 25                                                                   | 18                                                                  | RAM write, output, CMOS/TTL, normally high, data on AD <sub>7</sub> -AD0 is valid at the rising edge of this pulse.                                                               |  |  |

| IV. Switch Port Pins (RS-232 Mode) |                                                                      |                                                                     |                                                                                                                                                                                   |  |  |

| KDV                                | 2                                                                    | 71                                                                  | Data/voice Relay Control, output, TTL/CMOS. When high, indicates the voice (telephone set) relay is closed and the modem is in the voice mode.                                    |  |  |

| ОН                                 | 65                                                                   | 66                                                                  | Off-hook, output, TTL/CMOS, when high, indicates the DAA should go off-hook.                                                                                                      |  |  |

| S <sub>0</sub> -S <sub>6</sub>     | 50, 48, 46,<br>43, 41–39                                             | 50, 48, 46,<br>39, 37–35                                            | 7-bit input port for sensing switch setting inputs. Weak internal pull-ups (30 k $\!\Omega\!$ ) are provided on these inputs.                                                     |  |  |

| V. DAA Interface                   |                                                                      |                                                                     |                                                                                                                                                                                   |  |  |

| RI                                 | 61                                                                   | 62                                                                  | Ring indicator, input, Schmitt, when low, indicates the modem is receiving a ringing signal.                                                                                      |  |  |

|                                    |                                                                      |                                                                     | Vi. External ROM/RAM interface                                                                                                                                                    |  |  |

| CSRAM                              | 23                                                                   | 16                                                                  | Output, TTL/CMOS, chip select for external RAM, address from 4000H to 7FFFH.                                                                                                      |  |  |

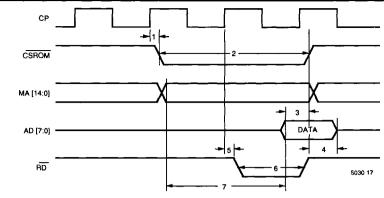

| CSROM                              | 19                                                                   | 12                                                                  | Output, TTL/CMOS, chip select for external ROM, address from 8000H to FFFFH.                                                                                                      |  |  |

| MA <sub>0</sub> -MA <sub>14</sub>  | 30, 35, 38,<br>47, 49, 51,<br>54, 56, 58,<br>67, 1, 4, 12,<br>14, 16 | 26, 31, 34,<br>47, 49, 51,<br>54, 56, 58,<br>68, 70, 74,<br>5, 7, 9 | Output, TTL/CMOS, 15 bit address bus for external program/data access.                                                                                                            |  |  |

| PD                                 | 27                                                                   | 20                                                                  | Output, CMOS open drain, indicates power down mode by active low.                                                                                                                 |  |  |

| -                                  |                                                                      |                                                                     | VII. Other Pins                                                                                                                                                                   |  |  |

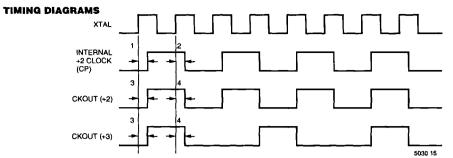

| CKOUT                              | 7                                                                    | 77                                                                  | Clock output pin, TTL/CMOS, from UMAC (9.8304 MHz).                                                                                                                               |  |  |

| RESET                              | 44                                                                   | 44                                                                  | Master reset Schmitt input, TTL, active high. When RESET is high, UMAC program counter resets to location 2000H. It resumes counting after RESET goes low.                        |  |  |

| V <sub>CCI</sub>                   | 68                                                                   | 69                                                                  | +5 V                                                                                                                                                                              |  |  |

| V <sub>CCP</sub>                   | 18                                                                   | 11                                                                  | Second V <sub>CC</sub> pin.                                                                                                                                                       |  |  |

| XTAL <sub>1</sub>                  | 10                                                                   | 2                                                                   | Together with XTAL <sub>2</sub> for crystal input (19.6608 MHz or 29.4912MHz).                                                                                                    |  |  |

| XTAL <sub>2</sub>                  | 11                                                                   | 3                                                                   | Crystal output pin (19.6608 MHz or 29.4912 MHz).                                                                                                                                  |  |  |

| GNDI                               | 6                                                                    | 76                                                                  | Ground.                                                                                                                                                                           |  |  |

| GNDI                               | 34                                                                   | 30                                                                  | Fourth Ground pin.                                                                                                                                                                |  |  |

| GNDP                               | 22                                                                   | 15                                                                  | Second Ground pin.                                                                                                                                                                |  |  |

| GNDP                               | 52                                                                   | 52                                                                  | Third Ground pin.                                                                                                                                                                 |  |  |

# PIN DESCRIPTIONS (continued)

|                                  | PIN N                                                                                                                                                                                                                                                                                                                        | UMBER             |                                                                                                                                                                    |  |  |  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIN NAME                         | PLCC                                                                                                                                                                                                                                                                                                                         | QFP               | DESCRIPTION                                                                                                                                                        |  |  |  |

|                                  | VIII. Special Pin Functions                                                                                                                                                                                                                                                                                                  |                   |                                                                                                                                                                    |  |  |  |

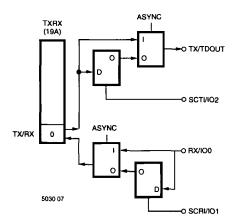

| UMAC, the fu                     | The UMAC can be configured to emulate the BigMAC (SC11021) which has four IO pins and a TDOUT pin added. For the UMAC, the functions of these 5 pins are preserved on power up or reset. When the SSCC mode is selected, the functions of these 5 pins will conform to the requirements for a firmware SSCC. (See Figure 3.) |                   |                                                                                                                                                                    |  |  |  |

| IX. In SSCC Mode                 |                                                                                                                                                                                                                                                                                                                              |                   |                                                                                                                                                                    |  |  |  |

| SCRI                             | 28                                                                                                                                                                                                                                                                                                                           | 24                | Synchronous clock receive. TTL input. Data from the MAP is valid on the rising edge of the clock.                                                                  |  |  |  |

| SCTI                             | 42                                                                                                                                                                                                                                                                                                                           | 38                | Synchronous clock transmit. TTL input. Data to the MAP is strobed in on the rising edge of this clock.                                                             |  |  |  |

| RX                               | 26                                                                                                                                                                                                                                                                                                                           | 19                | Receive data from MAP. TTL input.                                                                                                                                  |  |  |  |

| TDOUT                            | 62                                                                                                                                                                                                                                                                                                                           | 63                | Transmit data to MAP. TTL output.                                                                                                                                  |  |  |  |

| GPO                              | 45                                                                                                                                                                                                                                                                                                                           | 45                | General purpose output. TTL/CMOS compatible. RAM bank select. (SC11091 only).                                                                                      |  |  |  |

| S <sub>IN</sub>                  | 9                                                                                                                                                                                                                                                                                                                            | 80                | Input bit 7 of Data Register. Serial input to UART when XUART set low.                                                                                             |  |  |  |

| S <sub>OUT</sub>                 | 3_                                                                                                                                                                                                                                                                                                                           | 72                | UART serial output when XUART set low.                                                                                                                             |  |  |  |

| IO <sub>4</sub>                  | 3                                                                                                                                                                                                                                                                                                                            | 72                | General purpose output when XUART set high. Output follows the state of Bit 6 of Data Register.                                                                    |  |  |  |

|                                  | X. In Big MAC mode                                                                                                                                                                                                                                                                                                           |                   |                                                                                                                                                                    |  |  |  |

| IO <sub>0</sub> -IO <sub>3</sub> | 26, 28,<br>42, 45                                                                                                                                                                                                                                                                                                            | 19, 24,<br>38, 45 | General I/O Port, TTL/CMOS, tri-state. Each I/O can be configured as input or output under the control of GIO register. Not available on the SC11095. <sup>2</sup> |  |  |  |

| 105                              | 9                                                                                                                                                                                                                                                                                                                            | 80                | General purpose input when XUART is set high. Readable on bit 7 of the data register.                                                                              |  |  |  |

NOTE 1: The UMAC can be configured to emulate the BigMAC (SC11021) which has four IO pins and a TDOUT pin added. For the UMAC, the functions of these 5 pins are preserved on power up or reset. When the SSCC mode (GCRI:B0 = 1) is selected, the functions of these 5 pins will conform to the requirements for a firmware SSCC. (See Figure 3.)

NOTE 2: IO<sub>3</sub>/GPO pin is at ground on SC11095.

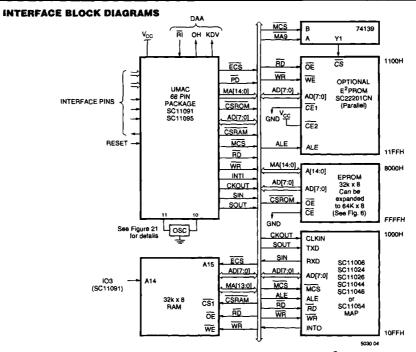

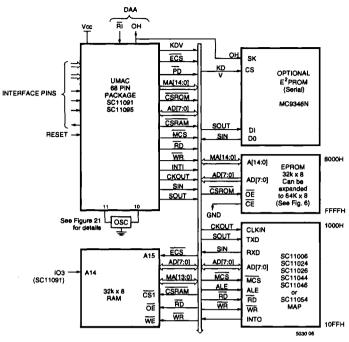

Figure 2a. UMAC 68 Pin Package Interfaces to MUX E<sup>2</sup>PROM, ROM Map

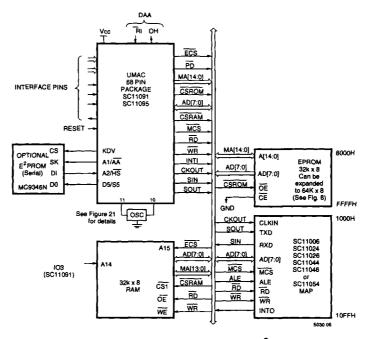

Figure 2b. UMAC 68 Pin Package Interfaces to Serial E<sup>2</sup>PROM, ROM Map for Serial Interface Configurations

1-504

#### INTERFACE BLOCK DIAGRAMS (continued)

Figure 2c. UMAC 68 Pin Package Interfaces to Serial E<sup>2</sup>PROM, ROM Map for Parallel Interface Configurations

#### **FUNCTIONAL DESCRIPTION**

The UMAC (Universal MAC) incorporates all the features of MAC (SC11011), BIGMAC (SC11021) and FastMAC (SC11061) plus other enhancements for greater capability and added value.

# New Features (compared to SC11011, SC1021, SC11061)

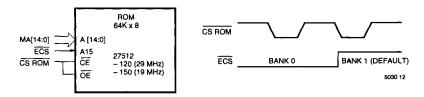

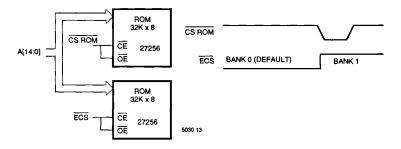

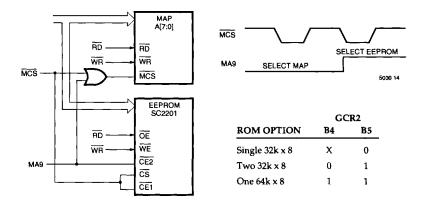

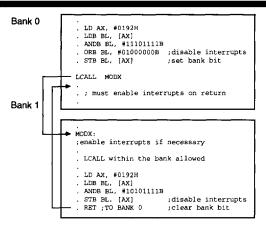

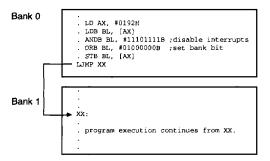

The UMAC has External ROM address space of 64K. On power up the original 32K ROM is selected. A register select is provided to witch over to the expanded 32K ROM using the ECS pin. Bank witching is simplified through the ise of instruction activated address synchronization.

Whereas the other controllers are built with 8 or 16K of internal ROM, he UMAC is designed to always use external ROM. Its internal ROM is just 256 bytes. This is for the

purpose of program execution at startup and execution during power down mode. Expanded internal RAM of 384 bytes allows for more features including buffering for Fax and asymmetrical modem protocols such as V.23.

The external RAM space of the SC11091 is doubled to 32K. The original 16K address space is allocated to RAM but provision is made for bank switching to select 32K as required for full V.42bis implementation. The SC11095 will access 16K RAM space only, due to the fact that the IO<sub>3</sub> pin (used for bank switching) is disabled. This prohibits the use of this part in V.42bis implementations.

In Power Down (or Standby) mode, the internal CPU clock is divided by 32 to reduce power while still remaining active and ready to respond to any input. The chip is placed in this mode by the external ROM firmware which will set the power-down bit when it determines there is no activity. The power-down bit is reset by hardware when DTR, CS, SIN or RI signals go true. An internal program loop monitors this bit and returns to normal modem operations when it is reset. By using the internal ROM for this loop, the external ROM may be de-selected so its power dissipation is minimized. A power-down mode indication is available from the PD pin to control external power switches.

In normal operation, the  $\overline{PD}$  pin behaves as a tristate pin. When power down is activated, the  $\overline{PD}$  pin becomes output active low. It can be used to drive an LED indicator.

By means of register selection, the RDY interface for the parallel PC can be de-activated. This is to cater to certain LAP TOP applications where the RDY line is not supported.

When the UMAC is first powered up or reset, it defaults to Big MAC mode, which is also the mode for MAC (11011). All programs written for ROMless Big MAC (11021) and MAC (11011) or the FastMAC (11061) should run with no or minimal modifications.

Weak pullups are provided on switch inputs so that external pullup resistors are not needed when option switches are employed.

Internal multiplexing for asymmetrical protocols such as V.23 (1200/75 bps) is provided to allow both answer and originate modes without additional chips.

The former EA pin of MAC and Big MAC (pin 27) is redefined on the SC11091 to indicate power down status and re-named PD. (Since the SC11091 always requires external ROM, the External Access option is

not used.) On power down activation  $\overline{PD}$  pin becomes output low. Otherwise it is tristated.

The SC11011 requires a 19.6608 MHz crystal. The SC11061 (Fast MAC) requires a 29.4912MHz crystal. The UMAC has a selectable internal clock divider so it can be used with either crystal. Start-up assumes a 19.6608 MHz crystal for compatibility with SC11011 or SC11021.

# Functions in common with SC11011

The SC11091 interfaces to a parallel system bus, such as that in the IBM PC, or by changing one bit in a register it interfaces to an RS232 port.

The UMAC receives 4-bit signal samples from the MAP and performs adaptive equalization, carrier phase recovery, data decode, and descrambling.

The UMAC is interrupted once every 1.667 msec (600 Hz). It reads two I channel samples and two Q

channel samples (T/2 sampling) within 100 µsec of receiving the interrupt.

After the samples are processed, a quad-bit (4 bits) of descrambled data is written back to the MAP. The MAP performs the synchronous to asynchronous conversion function, if operating in asynchronous mode, and outputs the received data on the RXD pin.

The UMAC uses a bit slice core processor to perform the digital signal processing (DSP) and the control functions. Its instruction set is a subset of the Intel 8096 instruction set but operates faster than the 8096. For instance, a signed (2's complement) 16bit x 16bit multiply with 32 bit result takes 3.5 µsec when operating with 19.6608 MHz crystal or 2µs with a 29.4912 MHz crystal. (Intel 8096 takes 6.5 µsec with a 12 MHz clock.)

When a 29.4912 MHz crystal is used, the ROM code must select a divide by 3 internal clock divider for compatibility with SC11061.

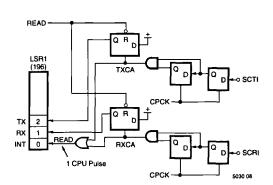

Figure 3a. Simplified Schematic of 1 bit SSCC

Figure 3b. SSCC Interrupt Circuit (Simplified)

#### FIRMWARE ARCHITECTURE

The SC11091/SC11095 uses a subset of 8096 instructions and can be compiled with an 8096 cross assembler such as AD2500. Rev 4.0x of this assembler is strongly recommended.

#### **Operand Types**

- 1. Short Integers: Short integers are 8-bit signed 2's complement variables. Results outside the range -128 and +127 will set the overflow bit in the Program Status Byte (PSB). There are no alignment restrictions on short integers.

- 2. Integers: Integers are 16-bit signed 2's complement variables. Arithmetic operations which generate results outside the range -32768 and +32767 will set the overflow bit in the PSB. The least significant byte of the integers is in the even byte address and the next most significant byte is in the next higher (odd) address. Therefore, the integers must be aligned at even byte boundaries in the address space. The address of a word is the address of its least significant byte (always an even address).

- 3. Bits: The bits within the bytes of the register file are numbered from 0 to 7 with 0 referring to the LSB. The only instructions that use bit addressing are JBC and IBS.

4. Long Integers: Long integers are 32-bit signed 2's complement variables. The result of a 16 x 16bit multiply will be stored in a long integer. Only SHRL and SHLL manipulate this data type. Long integers are addressed by the address of their least significant byte in the register file. They must be aligned such that their address is evenly divisible by 4. The most significant byte of a long integer resides on "address" +3, where "address" is the long integer's address.

#### **Operand Addressing**

Three types of addressing are allowed:

- 1. Immediate Addressing: This is a direct field within the instruction. For short integers, this is an 8-bit field, whereas, for the integers this is a 16-bit field. Only one operand within an instruction can be an immediate reference type. This operand must always be the last (right most) operand within an instruction.

- e.g. ADD AX, #340H is allowed ADD AX, #340H, BX is NOT allowed ADD AX, BX, #340H is allowed

- Register Direct Addressing: In this mode, an 8-bit field is used to access a register from the 384 byte register file. The register address must conform to the alignment rules. Only register addresses 0-255 may use direct addressing.

- e.g. ADD AX, BX :AX, BX must be "even" numbers ADDB AX, BX :AX, BX can be "odd" or "even"

- 3. Indirect Addressing: A memory location can be addressed indirectly by placing its 16-bit address in the register file. Only one operand (the right most operand) within an instruction can be indirect.

- e.g. ADDB AL, BL, [CX] is allowed ADDB AL, [CX], BL is NOT allowed

# Software Considerations for SSCC Implementation

The one bit SSCC approach saves a significant portion of hardware needed to implement the SSCC. The drawback is that the workload of the CPU is increased to emulate the SSCC. When operated at 1200 baud, the time window between data bits is 833  $\mu s$  and at 2400 baud, it is 417  $\mu S$ . The CPU must juggle between UART communication and DSP execution.

The following items should be considered:

#### SDLC:

- 1. Send flags (01111110) for start, stop or idle operation. (SC11054 Sendfax MAP included hardware flag detectors)

- For data and CRC result, a zero must be inserted after five ones has been transmitted.

- If five ones have been received and the next bit is zero, this zero bit is deleted

- 4. Detection of flag (01111110) or abort (11111111) sequence.

- Generation and checking of CRC-CCITT or the newer CRC-32 for 32 bit CRC.

- 6. Interpret, transmit and receive error conditions and make corrective actions for data integrity.

#### **BISYNC & MONOSYNC:**

- 1. Generation and detection of SYNC character.

- Selectable character length.

- 3. Parity may be included.

- 4. 6 or 8 bit (12 or 16 for bisync) sync character.

- 5. Detect escape sequence to prevent false sync detection and exclusion from CRC-16 calculation and checking.

- 6. Go into hunt mode to detect sync characters.

- 7. Interpret transmit and receive error conditions and make corrective actions for data integrity.

#### ASYNC:

- 1. Generation and detection of start and stop bits.

- 2. Selectable character length.

- 3. Parity may be included.

- 4. Selectable baud rates. Autobauding may be required. Independent baud rates for transmit and receive may be needed.

- 5. In MNP operation, CRC-16 generation and checking are required.

- 6. In MNP operation, detect escape sequence to prevent false sync detection and exclusion from CRC-16 calculation and checking.

- Intepret transmit and receive error conditions and make corrective actions for data integrity.

#### Interrupt Structure

Five interrupt sources exist in the UMAC, namely the external interrupt, timer interrupt, ring leading edge interrupt, SSCC and UART interrupt. The interupt service routine address is 2004H.

- 1. External interrupt: A low to high transition on the INTI pin initiates this interrupt.

- Timer interrupt: Timer overflow interrupt-frequency set by PSB bit 6 or GCR2 bits 2 and 3.

- 3. Ring leading edge: Interrupt generated by leading edge of ring input.

- 4. UART interrupt: Interrupt from

- a. Parallel version: From UMR register. Any one of the following can generate this interrupt:

- · RBR was read by external processor

- Data was transferred from THR to TSR

- LCR was changed

- · MCR was changed

- · DLL or DLM was changed b. Serial version: In this con-

- figuration the interrupt signal from 16C450 compatible UART is brought in as an interrupt source to the internal CPU.

#### 5. SSCC Interrupt.

## INSTRUCTION SET

The UMAC instruction set is a subset of Intel 8096 instruction set. The object codes, formats and the flags they effect are identical to those of 8096. The differences are:

- No VT or ST flags exist in the UMAC.

- Register locations in the UART section can only be accessed by using indirect addressing.

- The operands refer to one or more bytes of the register file. ROM locations can only be addressed using indirect addressing.

- If a memory location is addressed between 1000H and 12FFH, an external six clock multiplexed bus operation is initiated. The multiplexed address/data will use AD7-AD<sub>0</sub> bus.

- When using ST or STB operations, the destinations are always considered to be indirect addresses.

- e.g. ST, AX, [BX] is allowed

- ST, AX, BX is NOT allowed

| Location | Name | PC address | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0       |

|----------|------|------------|--------|--------|--------|--------|--------|--------|--------|---------|

| 180H     | RBR  | 0 (DLAB=0) | DATA.7 | DATA.6 | DATA.5 | DATA.4 | DATA.3 | DATA.2 | DATA.1 | DATA.0  |

| 181H     | IER  | 1 (DLAB=0) | 0      | 0      | 0      | 0      | EDSSI  | ELSI   | ETBEI  | ERBFI   |

| 182H     | IIR  | 2          | 0      | 0      | 0      | 0      | 0      | ID.1   | ID.0   | PENDING |

| 183H     | LCR  | 3          | DLAB   | SB     | PARITY | EPS    | PEN    | STB    | WLS1   | WLS0    |

| 184H     | MCR  | 4          | 0      | 0      | 0      | LOOP   | OUT2   | OUT1   | RTS    | DTR     |

| 185H     | LSR  | 5          | 0      | TEMT   | THRE   | BI     | FE     | PE     | OE     | DR      |

| 186H     | MSR  | 6          | DCD    | RI     | DSR    | CTS    | DDCD   | TERI   | DDSR   | DCTS    |

| 187H     | STR  | 7          | BIT7   | BIT6   | BIT5   | BIT4   | BIT3   | BIT2   | BIT1   | BIT0    |

| 188H     | DLL  | 0 (DLAB=1) | BIT7   | BIT6   | BIT5   | BIT4   | BIT3   | BIT2   | BIT1   | BIT0    |

| 189H     | DLM  | 1 (DLAB=1) | BIT15  | BIT14  | BIT13  | BIT12  | BIT11  | BIT10  | BIT9   | BIT8    |

| 18BH     | UMR  |            | RTRST  | CM     | RDI    | DLF    | LCF    | TXF    | RXF    | MCF     |

Table 2a. SC11091 UART Registers

| Location | Name  | 77       | 6         | 5        | 4        | 3        | 2          | 1          | 0          |

|----------|-------|----------|-----------|----------|----------|----------|------------|------------|------------|

| 18DH     | SWP   |          | S6        | S5       | S4       | 53       | S2         | <b>S</b> 1 | 50         |

| 18EH     | DIR   | _        |           | _        | -        | DIR3     | DIR2       | DIR1       | DIR0       |

| 18FH     | DAR   | DAR7     | DAR6      | DAR5     | DAR4     | DAR3     | DAR2       | DAR1       | DAR0       |

| 190H     | GCR   | CONF     | ОН        | KDV      | MRDY     | AA       | HS         | PAGE       | PD         |

| 191H     | TIM   | TFF7     | TFF6      | TFF5     | TFF4     | TFF3     | TFF2       | TFF1       | TFF0       |

| 192H     | PSB   | PD       | ROBK/TM   | IP       | IE       | Z        | N          | С          | V          |

| 193H     | ICR   | EXT_ENA  | TIMER_ENA | RING_ENA | UART_ENA | EXTERNAL | TIMER      | RING       | UART       |

| 194H     | GCR1  | SSCC_GPD | SSCC_SC   | SSCC_AEE | SSCC_LLB | SDLC     | USART      | USART      | SSCC       |

| 195H     | GCR2  | OSC0     | OSC1      | TIMER0   | TIMER1   | ROM64K   | BANKSW_ENA |            | NORDY      |

| 196H     | LSR1  | _        | -         | _        | -        | -        | SSCC_INT   | RX_AVA     | TX_EMPTY   |

| 199H     | ITEN  | _        |           | _        | -        | _        |            | RX_INT_ENA | TX_INT_ENA |

| 19AH     | TX/RX | _        | _         | _        | _        | _        | _          | _          | -          |

Table 2b. SC11091 Internal Registers

#### **ACCESSIBLE UART REGISTERS**

#### **UART Interrupt Enable Register (IER, location 181H)**

The 8-bit register enables the four types of interrupts of the UART to separately activate the chip interrupt (INTRPT) output signal. It is possible to totally disable the interrupt system by resetting bits 0 through 3 of the Interrupt Enable Register. Similarly, by setting the appropriate bits of this register to a logic 1, selected interrupts can be enabled. Disabling the interrupt system inhibits the Interrupt Identification Register and the active (high) INTRPT output from the chip. All other system functions operate in their normal manner, including the setting of the Line Status and MODEM Status Registers. The contents of the Interrupt Enable Register are indicated in Table 1 and are described below. NOTE: IIR and IER should be used as Read Only in Parallel Configuration.

| Bit Number | Bit Name | Description                                                                            |

|------------|----------|----------------------------------------------------------------------------------------|

| 0          | ERBFI    | This bit enables the Received Data Available Interrupt when set to logic 1.            |

| 1          | ETBEI    | This bit enables the Transmitter Holding Register Empty Interrupt when set to logic 1. |

| 2          | ELSI     | This bit enables the Receiver Line Status Interrupt when set to logic 1.               |

| 3          | EDSSI    | This bit enables the MODEM Status Interrupt when set to logic 1.                       |

| 4-7        |          | These four bits are always logic 0.                                                    |

#### Interrupt Identification Register (IIR, location 182H)

The UART has on-chip interrupt capability that allows for flexibility in interfacing popular micro-processors presently available. In order to provide minimum software overhead during data character transfers, the UART prioritizes interrupts into four levels. The four levels of interrupt conditions are as follows: Receiver Line Status (priority 1); Received Data Ready (priority 2); Transmitter Holding Register Empty (priority 3); and MODEM status (priority 4).

Information indicating that a prioritized interrupt is pending and the type of that interrupt are stored in the Interrupt Identifi-cation Register (IIR). When ad-dressed during chip-select time, the IIR freezes the highest priority interrupt pending and no other interrupts change the IIR, even though they are recorded, until the particular interrupt is serviced by the CPU. The contents of the IIR are described below.

| Bit Number Bit Name |                    | Description |                   |                                             |                                                                                |                                                                                                                                                    |

|---------------------|--------------------|-------------|-------------------|---------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                   |                    |             |                   | indicate whether an pending and the IIR     | interrupt is pending. When contents may be used as a po                        | itized or polled environment to<br>bit 0 is a logic 0, an interrupt is<br>inter to the appropriate interrupl<br>t is pending and polling (if used) |

| 1-2                 |                    | ·           |                   | Interrupt ID bits. The interrupt pending as |                                                                                | d to identify the highest priority                                                                                                                 |

| 3–7                 |                    |             |                   | These five bits of the                      | IIR are always logic 0.                                                        | <del> </del>                                                                                                                                       |

| Interrup            | t Ident<br>Registe |             | n                 | Interrupt Set and Reset F                   | unctions                                                                       |                                                                                                                                                    |

| Bit 2               | _                  |             | Priority<br>Level | Interrupt Type                              | Interrupt Source                                                               | Interrupt Reset Control                                                                                                                            |

| 0                   | 0                  | 1           |                   | None                                        | None                                                                           |                                                                                                                                                    |

| 1                   | 1                  | 0           | Highest           | Receiver Line Status                        | Overrun Error or Parity<br>Error or Framing Error<br>or Break Interrupt        | Reading the Line Status<br>Register                                                                                                                |

| 1                   | 0                  | 0           | Second            | Receiver Data Available                     | Receiver Data Available                                                        | Reading the Receiver<br>Buffer Register                                                                                                            |

| 0                   | 1                  | 0           | Third             | Transmitter Holding<br>Register Empty       | Transmitter Holding<br>Register Empty                                          | Reading the IIR Register<br>(If source of interrupt) or<br>Writing into the Transmitter<br>Holding Register                                        |

| 0                   | 0                  | 0           | Fourth            | MODEM Status                                | Clear to Send or Data Set<br>Ready or Ring Indicator<br>or Data Carrier Detect | Reading the MODEM<br>Status Register                                                                                                               |

### **ACCESSIBLE UART REGISTERS (continued)**

### Line Control Register (LCR), location 183H

The system programmer specifies the format of the asynchronous data communications exchange via the Line Control Register. In addition to controlling the format, the programmer may retrieve the contents of the Line Control Register for inspection. This feature simplifies system programming and eliminates the need for separate storage in system memory of the line characteristics. The contents of the Line Control Register are indicated in the following table.

| Bit Number | Bit Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0–1        | WLS0-WLS1 | Word Length Select Bits. These two bits specify the number of bits in each transmitted or received serial character. The encoding of bits 0 and 1 is as follows:                                                                                                                                                                                                                                                                                                          |  |

|            |           | BIT 1 BIT 0 WORD LENGTH                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|            |           | 0 0 5 Bits<br>0 1 6 Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|            |           | 1 0 7 Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|            |           | 1 1 8 Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 2          | STB       | Number of Stop Bits. This bit specifies the number of Stop bits in each transmitted character. If bit 2 is a logic 0, one Stop bit is generated in the transmitted data. If bit 2 is a logic 1 when a 5-bit word length is selected via bits 0 and 1, one and a half Stop bits are generated. If bit 2 is a logic 1 when either a 6-, 7-, or 8-bit word length is selected, two Stop bits are generated. The Receiver checks the programmed number of Stop-bits selected. |  |

| 3          | PEN       | Parity Enable. When bit 3 is a logic 1, a Parity bit is generated (transmit data) or checked (receive data) between the last data word bit and Stop bit of the serial data (The Parity bit is used to produce an even or odd number of 1s when the data word bits and the Parity bit are summed.)                                                                                                                                                                         |  |

| 4          | EPS       | Even Parity Select. This bit is the Even Parity Select bit. When bit 3 is a logic 1 and bit 4 is a logic 0, an odd number of logic 1s is transmitted or checked in the data word bits and Parity bit. When bit 3 is a logic 1 and bit 4 is a logic 1, an even number of logic 1s is transmitted or checked.                                                                                                                                                               |  |

| 5          |           | Stick Parity. When bits 3, 4 and 5 are logic 1 the Parity bit is transmitted and checked by the receiver as a logic 0. If bits 3 and 5 are 1 and bit 4 is a logic 0, then the Parity bit is transmitted as a 1.                                                                                                                                                                                                                                                           |  |

| 6          | SB        | Set Break. When it is set to a logic 1, the serial output (SOUT) is forced to the Spacing (logic 0) state. The break is disabled by setting bit 6 to a logic 0. The Break Control bit acts only on SOUT and has not effect on the transmitter logic.                                                                                                                                                                                                                      |  |

|            |           | Note: This feature enables the CPU to alert a terminal in a computer communica-<br>tions system. If the following sequence is followed, no erroneous or extraneous<br>characters will be transmitted because of the break.                                                                                                                                                                                                                                                |  |

|            |           | 1. Load an all 0s, pad character, in response to THRE.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|            |           | <ol> <li>Set break after the next THRE.</li> <li>Wait for the transmitter to be idle, (TEMT=1), and clear break when normal transmission has to be restored.</li> </ol>                                                                                                                                                                                                                                                                                                   |  |

|            |           | During the break, the Transmitter can be used as a character timer to accurately establish the break duration.                                                                                                                                                                                                                                                                                                                                                            |  |

| 7          | DLAB      | Divisor Latch Access Bit. It must be set high (logic 1) to access the Divisor Latches of the Baud Generator during a Read or Write operation. It must be set low (logic 0) to access the Receiver Buffer, the Transmitter Holding Register, or the Interrupt Enable Register.                                                                                                                                                                                             |  |

#### ACCESSIBLE UART REGISTERS (continued)

### Modem Control Register (MCR), location 184H

This 8-bit register controls the interface with the MODEM or data set (or a peripheral device emulating a MODEM). The contents of the MODEM Control Register are indicated in Table 6 and are described below.

| Bit Number | Bit Name         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0          | DTR              | This bit controls the Data Terminal Ready (DTR) output. When bit 0 is set to a logic 1, the DTR output is forced to a logic 0. When bit 0 is reset to a logic 0, the DTR output is forced to a logic 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1          | RTS              | This bit controls the Request to Send (RTS) output. Bit 1 affects the RTS output in a manner identical to that described above for bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2          | OUT1             | Auxiliary user-designated bit. It is connected to MSR[6] (RI) during local loopback.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3          | OUT2             | Auxiliary user-designated bit. It is connected to MSR[7] (DCD) during local loop-back. When Out2 = 0, INTO pin is Hi-Z.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4          | LOOP             | This bit provides a local loopback feature for diagnostic testing of the UART. When bit 4 is set to logic 1, the following occur: the transmitter Serial Output (SOUT) is set to the marking (logic 1) state; the receiver Serial Input (SIN) is disconnected; the output of the Transmitter Shift Register is "looped back" into the Receiver Shift Register input: the four MODEM Status Register bits CTS, DSR, DCD and RI are disconnected internally; and the four MODEM Control Register bits DTR, RTS, OUT1 and OUT2 are internally connected to the four MODEM Status Register inputs, and the MODEM Control output pins RLSD, CTS, DSR are forced to their inactive state (high). In the diagnostic mode, data that is transmitted is immediately received. This feature allows the processor to verify the transmit and received-data paths of the UART. |

|            | In the diagnost  | cic mode, the receiver and transmitter interrupts are fully operational. The MODEM Control Interrupts are also operational, but the interrupts' sources are now the lower four bits of the MODEM Control Register instead of the four MODEM Control inputs. The interrupts are still controlled by the Interrupt Enable Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5–7        | These bits are p | ermanently set to logic 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# Line Status Register (LSR], location 185H

This 8-bit register provides status information to the CPU concerning the data transfer. The contents of the Line Status Register are described below.

| Bit Number | Bit Name | Description                                                                                                                                                                                                                                                                                                                          |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0          | DR       | Data Ready indicator. Bit 0 is set to a logic 1 whenever a complete incoming character has been received and transferred into the Receiver Buffer Register. Bit 0 is reset to a logic 0 by reading the data in the Receiver Buffer Register.                                                                                         |

| 1          | OE       | Overrun Error indicator. Bit 1 indicates that data in the Receiver Buffer Register was not read by the CPU before the next character was transferred into the Receiver Buffer Register, thereby destroying the previous character. The OE indicator is reset whenever the CPU reads the contents of the Line Status Register.        |

| 2          | PE       | Parity Error indicator. Bit 2 indicates that the received data character does not have the correct even or odd parity, as selected by the even-parity-select bit. The PE bit is set to a logic 1 upon detection of a parity error and is reset to a logic 0 whenever the CPU reads the contents of the Line Status Register.         |

| 3          | FE       | Framing Error indicator. Bit 3 indicates that the received character did not have a valid Stop bit. Bit 3 is set to a logic 1 whenever the Stop bit following the last data bit or parity bit is detected as a zero bit (Spacing level). The FE indicator is reset whenever the CPU reads the contents of the Line Status indicator. |

| 4 | ВІ   | Break Interrupt indicator. Bit 4 is set to a logic 1 whenever the received data input is held in the Spacing (logic 0) state for longer than a full word trans-mission time (that is, the total time of Start bit + data bits + Parity + Stop bits). The BI indicator is reserved whenever the CPU reads the contents of the Line Status indicator.                                                                                                                                                                                 |

|---|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |      | Note: Bits 1 through 4 are the error conditions that produce a Receiver Line Status interrupt whenever any of the corresponding conditions are detected.                                                                                                                                                                                                                                                                                                                                                                            |

| 5 | THRE | Transmitter Holding Register Empty indicator. Bit 5 indicates that the ACE is ready to accept a new character for transmission. In addition, this bit causes the UART to issue an interrupt to the CPU when the Transmit Holding Register Empty Interrupt enable is set high. The THRE bit is set to a logic 1 when a character is transferred from the Transmitter Holding Register into the Transmitter Shift Register. The bit is reset to logic 0 concurrently with the loading of the Transmitter Holding Register by the CPU. |

| 6 | TEMT | Transmitter Empty indicator. Bit 6 is set to a logic 1 whenever the Transmitter Holding Register (THR) and the Transmitter Shift Register (TSR) are both empty. It is reset to a logic 0 whenever either the THR or TSR contains a data character.                                                                                                                                                                                                                                                                                  |

| 7 |      | This bit is permanently set to logic 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   |      | Note: The Line Status Register is intended for read operations only. Writing to this register is not recommended as this operation is used for factory testing.                                                                                                                                                                                                                                                                                                                                                                     |

#### Modern Status Register (MSR), location 186H

This 8-bit register provides the current state of the control lines from the MODEM (or peripheral device) to the CPU in addition to this current-state information, four bits of the MODEM Status Register provide change information. These bits are set to a logic 1 whenever a control input from the MODEM changes state. They are reset to logic 0 whenever the CPU reads the MODEM Status Register.

The contents of the MODEM Status Register are described below.

| Bit Number | Bit Name | Description                                                                                                                                                                                                          |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0          | DCTS     | This bit is the Delta Clear to Send indicator. Bit 0 indicates that the CTS input to the chip has changed state since the last time it was read by the CPU.                                                          |

| 1          | DDSR     | This bit is the Delta Data Set Read indicator. Bit 1 indicates that the DSR input to the chip has changed state since the last time it was read by the CPU.                                                          |