## SC11031/SC11040/SC11041/SC11042/SC11043 2400 bps Modem Advanced Controller II

## **FEATURES**

- ☐ Supports MNP2-5 and CCITT V.42bis, CCITT V.42

- ☐ Supports SDLC, HDLC, Bisync, Monosync & Async protocols in software

- ☐ Serial Transmit Bit

- ☐ Can address 128Kx8 ROM, 31.25Kx8 RAM

- ☐ Selectable Clock Frequency

- □ 16x16 multiply in 2µs

- ☐ Low Power Power-down (Stop) Mode

- ☐ Supports asymmetric protocols ☐ Sleepmode

- ☐ Pin compatible with SC11011, 21, 61, 91, 95

- ☐ Direct interface to Sierra Modems & Datapumps

## **GENERAL DESCRIPTION**

The SC11031/SC11040 series are application-specific Modem Controllers that perform DSP and control functions for a variety of modems operating up to 9600 bps. Various members of the family can perform error control and compression algorithms according

- ☐ 384 Byte internal RAM

- Power Down mode indicator on  $\overline{PD}$  pin

- CMOS technology

- 16C450 compatible UART

## APPLICATIONS

- ☐ V.22bis modem with V.42bis

- compression (11043) MNP2-5 modems

- Class 1 and 2 Fax & Data modems

- Feature rich International modems

- Upgrade from SC11011, 11021, 11061, 11091, 11095

- Synchronous data links

- Voice, Fax and Data modems

These second generation devices offer expanded addressing capability for feature-rich products.

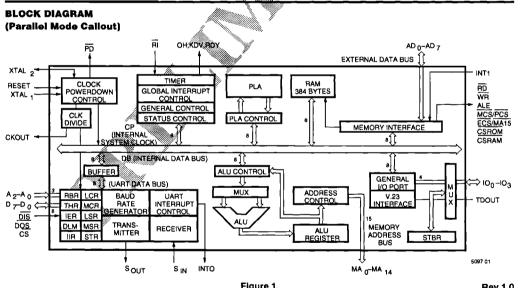

## **68-PIN PLCC PACKAGE**

SC11031CV, SC11040CV, SC11041CV, SC11042CV, SC11043CV

## 80-PIN QFP PACKAGE (14 mm)

SC11031CQ, SC11040CQ, SC11041CQ, SC11042CQ, SC11043CQ

They also consume substantially less power compared to earlier devices and offer very low power standby modes.

The SC11031 is ROMless and is used for general applications. It can be used in place of SC11011,

Figure 1.

**Rev 1.0**

## **GENERAL DESCRIPTION (continued)**

SC11021, or SC11061. SC11040 series devices have internal ROM programmed for specific applications. See Table 1 for a summary of these devices.

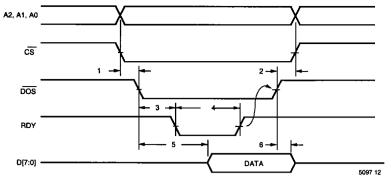

These devices contain a 16C450 compatible UART which can be configured to provide a serial or parallel DTE interface. In the RDY mode, the MAC II provides an I/O

channel ready (RDY) signal to insert wait states in the PC bus read/write cycle to allow reliable data transfer with any speed bus.

|                                       | SC11031  | SC11040  | SC11041  | SC11042  | SC11043  |

|---------------------------------------|----------|----------|----------|----------|----------|

| V.21, V.22, V.22 bis<br>Bell 212A/103 | ✓        | 1        | 1        | 1        | 1        |

| Fax Class                             | 1, 2     |          | 1, 2     | 1, 2     | 1, 2     |

| MNP2~5                                |          |          | 1        | 1        | 1        |

| V.42                                  |          |          |          | /        | 1        |

| V.42bis                               |          |          |          |          | /        |

| Caller I.D.                           | optional | optional | optional | optional | optional |

| Voice                                 |          | optional | optional | optional | optional |

Table 1. SC1104X Series Function

## PIN DESCRIPTIONS

|                                | PIN N                                | UMBER                                |                                                                                                     |  |  |  |

|--------------------------------|--------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|

| PIN NAME                       | PLCC                                 | QFP                                  | DESCRIPTION                                                                                         |  |  |  |

|                                |                                      | ı                                    | . Parallel Systems interface (to PC bus)                                                            |  |  |  |

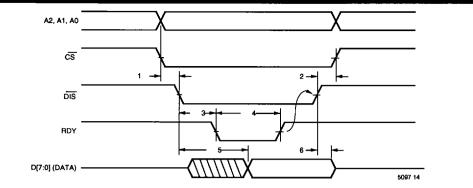

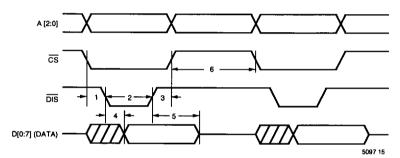

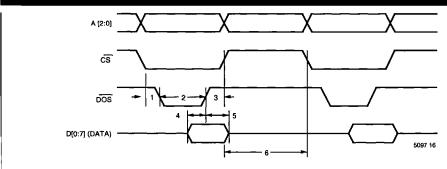

| A <sub>0</sub> -A <sub>2</sub> | 57, 55, 53                           | 57, 55, 53                           | INPUT, TTL. Address lines for UART register select.                                                 |  |  |  |

| CS                             | 63                                   | 64                                   | INPUT, TTL. Chip select, active low.                                                                |  |  |  |

| D <sub>0</sub> −D <sub>7</sub> | 50, 48, 46,<br>43, 41, 40,<br>39, 37 | 50, 48, 46,<br>39, 37, 36,<br>35, 33 | INPUT-OUTPUT, TTL. 8-bit data port.                                                                 |  |  |  |

| DIŜ                            | 64                                   | 65                                   | INPUT, TTL. Data in strobe (PC reads from UART registers), active low.                              |  |  |  |

| DOS                            | 59                                   | 59                                   | INPUT, TTL. Data out strobe (PC writes into UART registers), active low.                            |  |  |  |

| INTO                           | 66                                   | 67                                   | OUTPUT, CMOS/TTL. Tristate™. Interrupt.                                                             |  |  |  |

| RDY                            | 60                                   | 61                                   | OUTPUT. Open Drain. Ready signal for high speed PC-AT interface.                                    |  |  |  |

|                                |                                      | II. RS                               | 3-232 (Data Set Mode) and Display Interface                                                         |  |  |  |

| ĀĀ                             | 55                                   | 55                                   | OUTPUT, CMOS/TTL. Automatic answer enable indicator (low).                                          |  |  |  |

| CTS                            | 59                                   | 59                                   | OUTPUT, CMOS/TTL. Clear to send.                                                                    |  |  |  |

| DSR                            | 63                                   | 64                                   | OUTPUT, CMOS/TTL. Data set ready.                                                                   |  |  |  |

| DTR                            | 64                                   | 65                                   | INPUT, TTL. Data terminal ready.                                                                    |  |  |  |

| HS                             | 53                                   | 53                                   | <b>OUTPUT, CMOS/TTL.</b> High speed indicator. Low when operating at 2400 bps rate. High otherwise. |  |  |  |

| MRDY                           | 66                                   | 67                                   | Modem ready.                                                                                        |  |  |  |

| RLSD                           | 57                                   | 57                                   | OUTPUT, CMOS/TTL. Carrier detect.                                                                   |  |  |  |

| RTS                            | 37                                   | 33                                   | INPUT, TTL. Request to send, input, TTL.                                                            |  |  |  |

Tristate is a trademark of National Semiconductor.

|                                   | PIN N                                                                | JMBER                                                               |                                                                                                                                                                                                                                    |

|-----------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN NAME                          | PLCC                                                                 | QFP                                                                 | DESCRIPTION                                                                                                                                                                                                                        |

|                                   |                                                                      |                                                                     | III. MAP Interface                                                                                                                                                                                                                 |

| AD <sub>0</sub> -AD <sub>7</sub>  | 31–33, 21,<br>20, 17, 15, 13                                         | 27–29, 14,<br>13, 10, 8, 6                                          | <b>INPUT-OUTPUT, CMOS.</b> 8-bit bidirectional multiplexed address/databus. Weak internal pull-ups $(30k\Omega)$ are provided on these inputs.                                                                                     |

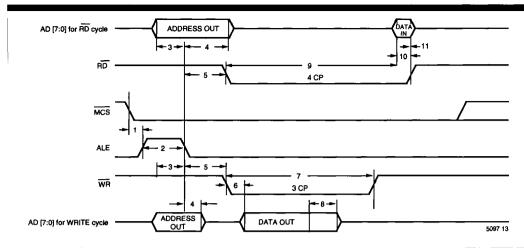

| ALE                               | 8                                                                    | 78                                                                  | <b>OUTPUT, CMOS/TTL.</b> Address Latch Enable. The address on ECS, MCS, $AD_7 - AD_0$ are valid at the falling edge of this normally low pulse.                                                                                    |

| ECS/MA15                          | 36                                                                   | 32                                                                  | OUTPUT, CMOS/TTL. External EERAM chip select. Addressing space is from 280H to 2FFH. When used for expanded ROM mode, the ECS functions as MA15.                                                                                   |

| INTI                              | 5                                                                    | 75                                                                  | INPUT, TTL. Interrupt received from the MAP. Interrupt is detected when this pin has a low to high transition. The line has to stay high for at least 200 ns.                                                                      |

| MCS/PCS                           | 24                                                                   | 17                                                                  | OUTPUT, CMOS/TTL. Map chip select for MAP interface. Addressing space is from 200H to 27FH. When used in expanded ROM mode, the Addressing space expands from 200H to 2FFH. This function is known as PCS, Peripheral Chip Select. |

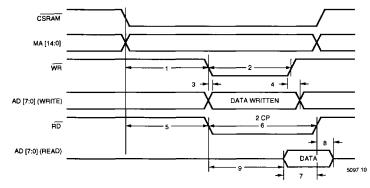

| RD                                | 29                                                                   | 25                                                                  | <b>OUTPUT, CMOS/TTL.</b> RAM read. Normally high, data on AD <sub>7</sub> – AD <sub>0</sub> must be valid at the rising edge of this pulse.                                                                                        |

| S <sub>IN</sub>                   | 9                                                                    | 80                                                                  | INPUT, TTL. Received data. Serial data received from the DTE.                                                                                                                                                                      |

| S <sub>OUT</sub>                  | 3                                                                    | 72                                                                  | OUTPUT, CMOS/TTL. Transmit data. Serial data to be transmitted to the modern.                                                                                                                                                      |

| WR                                | 25                                                                   | 18                                                                  | OUTPUT, CMOS/TTL. Peripheral write. Normally high, data on AD <sub>7</sub> - AD0 is valid at the rising edge of this pulse.                                                                                                        |

|                                   |                                                                      |                                                                     | IV. Switch Port Pins (RS-232 Mode)                                                                                                                                                                                                 |

| KDV                               | 2                                                                    | 71                                                                  | OUTPUT, CMOS/TTL. Data/voice Relay Control. When high, indicates the voice (telephone set) relay is closed and the modem is in the voice mode.                                                                                     |

| ОН                                | 65                                                                   | 66                                                                  | OUTPUT, CMOS/TTL. Off-hook. When high, indicates the DAA should go off-hook.                                                                                                                                                       |

| S <sub>0</sub> -S <sub>6</sub>    | 50, 48, 46,<br>43, 41–39                                             | 50, 48, 46,<br>39, 37–35                                            | <b>INPUT, TTL.</b> 7-bit input port for sensing switch setting inputs. Weak internal pull-ups $(30  \mathrm{k}\Omega)$ are provided on these inputs. These only work in serial mode                                                |

|                                   |                                                                      |                                                                     | V. DAA Interface                                                                                                                                                                                                                   |

| RI                                | 61                                                                   | 62                                                                  | SCHMITT INPUT. Ring indicator. When low, indicates the modem is receiving a ringing signal.                                                                                                                                        |

|                                   |                                                                      |                                                                     | VI. External ROM/RAM Interface                                                                                                                                                                                                     |

| CSRAM                             | 23                                                                   | 16                                                                  | OUTPUT, CMOS/TTL. Chip select for external RAM, address from 300H to 7FFFH.                                                                                                                                                        |

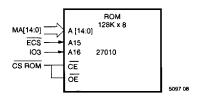

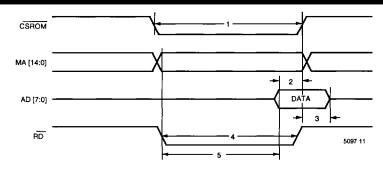

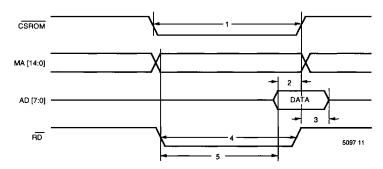

| CSROM                             | 19                                                                   | 12                                                                  | OUTPUT, CMOS/TTL. Chip select for external ROM, address from 8000H to FFFFH.                                                                                                                                                       |

| MA <sub>0</sub> -MA <sub>14</sub> | 30, 35, 38,<br>47, 49, 51,<br>54, 56, 58,<br>67, 1, 4, 12,<br>14, 16 | 26, 31, 34,<br>47, 49, 51,<br>54, 56, 58,<br>68, 70, 74,<br>5, 7, 9 | OUTPUT, CMOS/TTL. 15 bit address bus for external program/data access.                                                                                                                                                             |

| PD                                | 27                                                                   | 20                                                                  | OUTPUT, OPEN DRAIN. Indicates power down mode by active low.                                                                                                                                                                       |

| TDOUT/TX                          | 62                                                                   | 63                                                                  | <b>OUTPUT, TTL/CMOS.</b> Transmit DATA. Serial data to be transmitted by the modem.                                                                                                                                                |

| RX                                | 26                                                                   | 19                                                                  | INPUT, TTL. Serial Data received by the modem.                                                                                                                                                                                     |

#### PIN DESCRIPTIONS (continued) SC11031/SC11040/SC11041/SC11042/SC11043 PIN NUMBER PIN NAME **PLCC** DESCRIPTION QFP VII. Other Pins CKOUT 7 77 CLOCK OUTPUT PIN, TTL/CMOS. From MAC II (9.8304 MHz). INPUT, TTL, ACTIVE HIGH. Master reset schmitt. When RESET is high, MAC RESET 44 44 II program counter resets to location 2000H. It resumes counting after RESET goes low. $V_{CCI}$ 68 69 +5 V. $V_{\underline{C}\underline{CP}}$ 18 11 Second V<sub>CC</sub> pin. 10 XTAL<sub>1</sub> 2 Together with $XTAL_2$ for crystal input (19.6608 MHz or 29.4912MHz). XTAL<sub>2</sub> 11 Crystal output pin (19.6608 MHz or 29.4912 MHz). 3 GNDI 6 76 Ground. GNDI Fourth Ground pin. 34 30 GNDP 22 15 Second Ground pin. **GNDP** 52 52 Third Ground pin. VIII. Special Pin Functions The MAC II can be configured to emulate the BigMAC (SC11021) which has four IO pins and a TDOUT pin added. For the MAC II, the functions of these 5 pins are preserved on power up or reset. When the STBR (Serial Transmit Bit Register) mode is selected, IO2 becomes SCTI, IO0 becomes RX, and TDOUT becomes TX. IX. in STBR Mode SCTI INPUT, TTL. Synchronous clock transmit. TData to the MAP is strobed in on 42 38 the rising edge of this clock. OUTPUT, TTL/CMOS. TX 63 62

X. In Big MAC mode

GENERAL I/O PORT, TTL/CMOS, TRI-STATE. Each I/O can be configured as

input or output under the control of GIO register. Weak internal pull-ups are

provided on these inputs. IO4 through IO7 is only available in QFP for the

100-107

26, 28,

42, 45

19, 24,

38, 45, 23,

43, 60, 1

. SC11031.

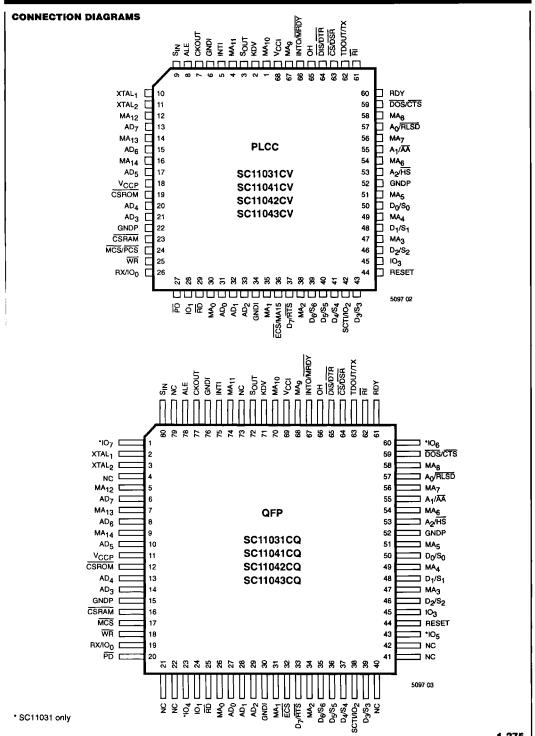

## **FUNCTIONAL DESCRIPTION**

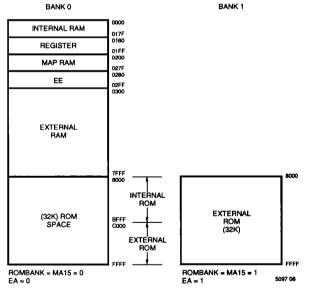

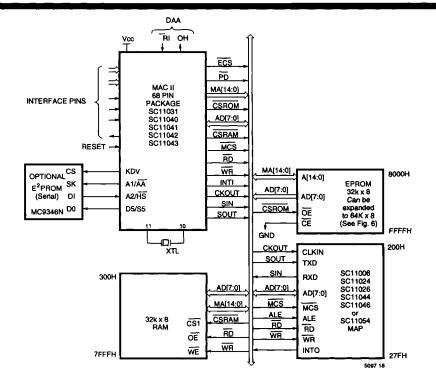

The MAC II has External ROM address space of 64K. On power up the original 32K ROM is selected. A register select is provided to switch over to the expanded 32K ROM using the ECS pin.

Expanded internal RAM of 384 bytes allows for more features including buffering for Fax and asymmetrical modem protocols such as V.23.

The original 16K RAM address is expanded to 31.25K as required for full V.42bis implementation.

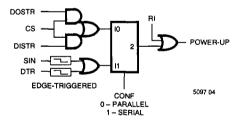

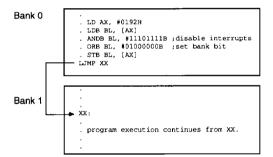

In Power Down (or Stop) mode, the internal CPU clock is turned off. The power-down circuitry is kept alive and ready to respond to any valid power up input. The power-down bit is reset by hardware when DTR or SIN becomes active on a negative edge trigger, when RI becomes level active, or a valid CS is generated by the PC Bus, (level active low).

In the RC Mode an internal oscillator is used instead of the XTAL oscillator. If one enters power-down mode while in RC mode, the XTAL oscillator is turned off, thereby reducing the powerdown current by more than 50%. When coming out of powerdown while in RC mode, the firmware must wait 20 msec before switching back to XTAL mode because the XTAL oscillator needs time to start-up and stabilize. A power-down mode indication is available from the PD pin to control external power switches.

In normal operation, the  $\overline{PD}$  pin behaves as a tristate pin. When power down is activated, the  $\overline{PD}$  pin becomes output active low. It can be used to drive an LED indicator or control power to other devices.

The active power can be reduced by using the sleep mode. The system clock can be divided down by 5 different divisors. Please refer to the GCR2 register description. CKOUT is unaffected, but the UART base clock of the baud rate generator is affected. If the UART is used in sleep mode, then the divisor numbers need to be compensated for by the same divisor.

When the MAC II is first powered up or reset, it defaults to Big MAC mode, which is also the mode for the MAC (11011). All programs written for ROMless Big MAC (11021) and MAC (11011) or the FastMAC (11061) should run with minor modifications.

Weak pullups are provided on switch inputs so that external pullup resistors are not needed when option switches are employed.

Internal multiplexing for asymmetrical protocols such as V.23 (1200/75 bps) is provided to allow both answer and originate modes without additional chips.

The former EA pin of MAC and Big MAC (pin 27) is redefined on the MAC II to indicate power down status and renamed PD. On power down activation the PD pin becomes output low. Otherwise it is tristated.

The MAC II has a selectable internal clock divider so it can be used with either a 19.6608 MHz or 29.412 MHz crystal. Start-up assumes a 19.6608 MHz crystal for compatibility with SC11011 or SC11021.

The MAC II interfaces to a parallel system bus, such as that in the IBM PC, or by changing one bit in a register it interfaces to an RS-232 port. The power on/reset default is parallel configuration.

The MAC II is interrupted once every 1.667 msec (600 Hz). It must read two I channel samples and two Q channel samples (T/2 sampling) within 100  $\mu$ sec of receiving the interrupt.

After the samples are processed a quad-bit (4 bits) of descrambled data is written back to the MAP. The MAP performs the synchronous to asynchronous conversion function, if operating in asynchronous mode, and outputs the received data on the RXD pin.

The MAC II uses a bit slice core processor to perform the digital signal processing (DSP) and the control functions. Its instruction set is a subset of the Intel 8096 instruction set but operates faster than the 8096. For instance, a signed (2's complement) 16 bit by 16 bit multiply with 32 bit result takes 3.5 µsec when operating with 19.6608 MHz crystal or 2µs with a 29.4912 MHz crystal. (Intel 8096 takes 6.5 µsec with a 12 MHz clock.)

A wait state generator has been added for applications that do not require fast ROMS. This adds one clock cycle to each ROM access.

Hardware Echo has been added to assist in high Speed Autobauds.

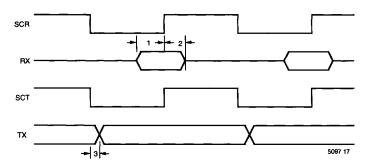

Figure 3. VALID Power-up inputs

## HARDWARE ARCHITECTURE

The MAC II device is organized with two buses that interconnect four main logic sections. The two buses are the internal data bus (DB) and address bus (Y). The four sections of the device are the internal processor, registers, memory, and dual port UART.

The two bus architecture was chosen to allow the MAC II to execute the 8096 instruction set as fast or faster than the 8096 itself. The device is intended to run at 9.8304 MHz or 14.745MHz. (The internal divider provides these clock speeds from an external 19.6608 MHz or 29.4912 MHz crystal.) A typical three operand instruction effectively executes in 10 clock cycles. The signed 16 x 16 multiply operation requires 34 clock cycles.

The internal data bus (DB) is the main bus of the device. It is an 8-bit bus that interconnects all four sections of the device. All internal data travels on DB. The Y bus is a 16-bit output only bus fromthe internal processor that provides addresses to the memory and register sections of the device. This bus allows memory control to be resident inside the internal processor without degrading performance.

The internal processor controls MAC II operations and performs all of the required computation functions. The internal processor consists of a microcontrol PLA and a 16-bit registered arithmetic/logic unit (RALU). The microcontrol PLA accepts as input 8096 instruction opcodes and generates the control sequences necessary to implement the instructions. The RALU performs instruction exe-cution, operand address calculation, jump address calculation, program sequencing, and stack control. The program counter (PC) and stack pointer (SP) are contained within the RALU. The RALU is implemented with the 2901 silicon compiler.

The register section of the MAC II includes RAM and the ports of the device. Code can't be executed

from registers; however, it can be executed from external RAM or ROM. The UART registers are functionally, but not physically, part of the register section. The UART registers are accessed via indirect addressing mode only. There are 384 bytes of internal RAM to support DSP functions and the command set. The memory section of the MAC II includes the program ROM and the external memory interface. The device contains 16K bytes (except 11031) of program ROM. The external memory interface allows the MAC II to access program storage or data storage from external

The UART section of the device implements, in hardware, the industry standard 16C450 UART. In its parallel version the MAC II appears as a 16C450 to the user. The UART contains true dual-port capability to allow the user and the internal processor access to its internal registers.

## **Datapath & Description**

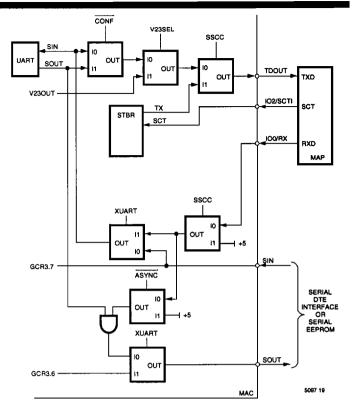

Figure 5a shows the data path portion of MAC II. The function of the

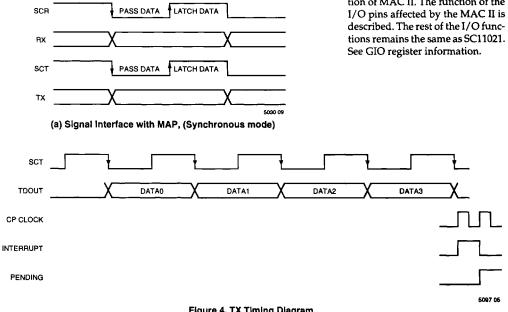

Figure 4. TX Timing Diagram

# Hardware Description of the STBR

The serial transmit bit word consists of a 4-bit shift register which is clocked by SCT. Data 0 is shifted out first, and Data 3 is the last bit shifted out. An interrupt is generated on the last shift if the enable bit is set. The pending bit remains high until it is cleared by reading the STBR register. Data 3 remains on the TX output until the next 4-bit data is loaded.

## Clock Generation and Powerdown

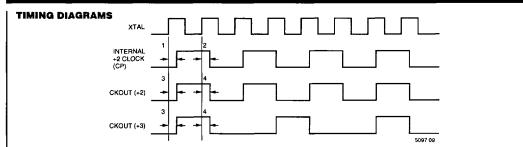

The MAC II runs on either a 19.6608 MHz or 29.4912 MHz crystal. This frequency is divided by two and the 9.8304 MHz is used for internal hardware timing and for the CKOUT clock. When the MAC II is operated at 29.4912MHz (1.5X) the internal CPU clock remains at half the crystal oscillator speed. However, the UART baud rate, the timers and the CKOUT to the MAP are kept at the normal speed to maintain compatibility. This is done by setting GCR1.80 to a 1.

CKOUT—is maintained at 9.8304 MHz. When the MAC II is running at 19.6608 MHz and GCR1.B0 is set to a zero, a divide by 2 circuit will enable CKOUT to maintain 9.8304 MHz. When it is running at 29.4912 MHz and GCR1.B1 is set to a one, a divide by 3 circuit will enable CKOUT to maintain 9.8304 MHz. The CKOUT is phase synchronized with the internal CPU clock when the divide by 2 is selected.

**UART**—Maintains the same base clock into the baud rate generator.

Power down mode is activated in the same manner as in BigMAC when bit 7 of the PSB byte is set high and inputs RI, CS, DTR and SIN are all high. In this mode, the internal CPU clock is turned off. The MAC II comes out of power down mode when any of the inputs are set low.

Figure 5a. MAC II Internal Data Path

Figure 5b. MAC II Address Map

## **RDY Interface**

The RDY pin is used to inject wait states to synchronize the MAC II with the PC's parallel access. Some Laptops do not incorporate this wait mechanism. MAC II will still be able to interface to these laptops without having to use the RDY pin.

## **MEMORY DESCRIPTION**

## Internal ROM:

The MAC II controller is built with the same basic architecture as the SC11019/20/21/22/23 so that firmware will be upward compatible.

### **External Read/Write:**

Three different types of external memory operations are defined.

A) For address from 0200H to 02FFH:

These external operations occur through the AD bus. These operations take six clock cycles, four more than internal operations. These are mainly for MAP & EEROM interfaces, however,

instructions and data can also be fetched from these memory spaces.

B) For address from 0300H to 7FFFH:

These memory spaces are reserved for external DATA storage. The MAC II can access external RAM through MA address bus and AD data bus. There are three clock cycles for each access.

C) For address from 8000H to FFFFH:

The chip fetches instructions from external program storage by  $MA_0$ – $MA_{14}$  and  $AD_0$ – $AD_7$ . These operations are exactly the same as internal ROM fetch and they take three clock cycles.

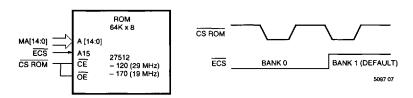

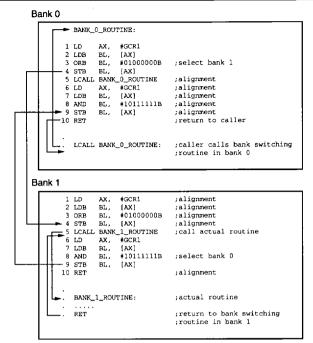

# Extended ROM bank switching and addressing

With increased code needed to service MNP and V.42bis classes of communication, the usual 32K ROM may not be sufficient to hold all the code. However, one extra gate is needed to select the MAP

when the 64k mode is used. The extended ROM is one 64Kx8 ROM (27512).

The external ROM access starts at Bank 1 as the ECS pin is high by default. To select extended ROM set GCR1:B4 mode, and GTCR1:B6. The rombank configuration bit, GCR1.B4, must be set to reconfigure ECS as MA15 and MCS as PCS. The Rombank bit, GCR1.B6, must be set to bank 1, the same as the ECS default. Switching between bank 1 and bank 0 is done by setting or resetting GCR1.B6. More than 64K can be accessed by using an additional I/O pin, such as IO3, as MA16.

# RD Indication During External ROM Access

The SC11011, 21 & 61 do not provide an indication when the ROM contents are read into the CPU. In the MAC II, the RD pin goes low for 2 clock cycle when the ROM contents are being read into the MAC II CPU. The RD function is the same for extended ROM operation.

Figure 6a. OE Could be Grounded, But Above Connection Saves Power in PD Mode.

Figure 6b. 128K ROM Connections

Figure 6. Interface Block Diagrams for Optional Modes

Code at line 1 must start at the same address in both banks. And code alignment must be maintained in the bank switching routines.

Here GCR1.6 and DAR.3 are used as A15 and A16, respectively (see Figure 6b). Thus by changing their values in a similar way, it is possible to switch from any bank to any other bank

LJMP across banks is accomplished by simply changing the bank bit in either GCR1 or DAR, such as line 1 to line 4 in Table 4a. Code execution from the other bank begins immediately after the STB instruction.

When an interrupt happens, the program pointer always points to 8004H of the current bank it is in. There is two ways to handle interrupts. One is to copy the same interrupt handling routine to all banks. The second way is to use bank switching routines to switch to bank 0 to handle the interrupt, and then return to the original bank. To save code space, the second way is recommended. The implementation is similar to Table 4a, except that a PUSHF has to precede line 1 to disable interrupts, and a POPF has to be put between line 9 and 10 to re-enable interrupts.

Table 4a, LCALL Across Bank

Table 4b. LJMP Across Bank

## FIRMWARE ARCHITECTURE

The MAC II uses a subset of 8096 instructions and can be compiled with an 8096 cross assembler such as AD2500. Rev 4.0x of this assembler is strongly recommended.

## **Operand Types**

- 1. Short Integers: Short integers are 8-bit signed 2's complement variables. Results outside the range –128 and +127 will set the overflow bit in the Program Status Byte (PSB). There are no alignment restrictions on short integers.

- 2. Integers: Integers are 16-bit signed 2's complement variables. Arithmetic operations which generate results outside the range -32768 and +32767 will set the overflow bit in the PSB. The least significant byte of the integers is in the even byte address and the next most significant byte is in the next higher (odd) address. Therefore, the integers must be aligned at even byte boundaries in the address space. The address of a word is the address of its least significant byte (always an even address).

- Bits: The bits within the bytes of the register file are numbered from 0 to 7 with 0 referring to the LSB. The only instructions that use bit addressing are JBC and JBS.

- 4. Long Integers: Long integers are 32-bit signed 2's complement variables. The result of a 16 x 16-bit multiply will be stored in a long integer. Only SHRL and SHLL manipulate this data type. Long integers are addressed by the address of their least significant byte in the register file. They must be aligned such that their address is evenly divisible by 4. The most significant byte of a long integer resides on "address" +3, where "address" is the long integer's address.

## **Operand Addressing**

Three types of addressing are allowed:

- Immediate Addressing: This is a direct field within the instruction. For short integers, this is an 8-bit field, whereas, for the integers this is a 16-bit field. Only one operand within an instruction can be an immediate reference type. This operand must always be the last (right most) operand within an instruction.

- e.g. ADD AX, #340H is allowed ADD AX, #340H, BX is NOT allowed ADD AX, BX, #340H is allowed

- Register Direct Addressing: In this mode an 8-bit field is used to access a register from the 384 byte register file. The register address must conform to the alignment rules. Registers 256-383 can use direct addressing only if the page bit, GCR bit 1, is set.

- e.g. ADD AX, BX :AX, BX must be "even" numbers ADDB AX, BX :AX, BX can be "odd" or "even"

- Indirect Addressing: A memory location can be addressed indirectly by placing its 16-bit address in the register file. Only one operand (the right most operand) within an instruction can be indirect.

- e.g. ADDB AL, BL, [CX] is allowed ADDB AL, [CX], BL is NOT allowed

- Indexed addressing is NOT allowed.

## Interrupt Structure

Five interrupt sources exist in the MAC II, namely the external interrupt, timer interrupt, ring leading edge interrupt, STBR transmit and UART interrupt. The interrupt service routine address is 8004H.

- External interrupt: A low to high transition on the INTI pin initiates this interrupt.

- 2. Timer interrupt: Timer over-

- flow interrupt—frequency set by GCR bits 0.

- Ring leading edge: Interrupt generated by leading edge of ring input.

- 4. UART interrupt: Interrupt from UART.

- Parallel version: From UMR register. Any one of the following can generate this interrupt:

- RBR was read by external processor

- Data was transferred from THR to TSR

- · LCR was changed

- MCR was changed

- SHDLL or SHDLM was changed

- b. Serial version: In this configuration the interrupt signal, IIR from the 16C450 compatible UART is brought in as an interrupt source to the internal CPU.

- TX Interrupt. Interrupt initiated when 4-bit data has finished shifting.

## INSTRUCTION SET

The MAC II instruction set is a subset of Intel 8096 instruction set. The object codes, formats and the flags they effect are identical to those of 8096. The differences are:

- No VT or ST flags exist in the MAC II.

- Register locations in the UART section can only be accessed by using indirect addressing.

- The operands refer to one or more bytes of the register file. ROM locations can only be addressed using indirect addressing.

- If a memory location is addressed between 200H and 2FFH, an external six clock multiplexed bus operation is initiated. The multiplexed address/data will use AD<sub>7</sub>-AD<sub>0</sub> bus.

- When using ST or STB operations, the destinations are always considered to be indirect addresses.

- e.g. ST, AX, [BX] is allowed ST, AX, BX is NOT allowed

|              | MNEMONIC | NO. OF OPERANDS   | OPERATION                       | BYTES1 | TIME <sup>2</sup>   |

|--------------|----------|-------------------|---------------------------------|--------|---------------------|

|              | ADD/ADDB | 2                 | $B \leftarrow A + B$            | 3      | 10                  |

|              | ADD/ADDB | 3                 | $D \leftarrow A + B$            | 4      | 10                  |

| 11           | AND/ANDB | 2                 | $B \leftarrow A \text{ AND } B$ | 3      | 10                  |

|              | AND/ANDB | 3                 | $D \leftarrow A \text{ AND } B$ | 4      | 10                  |

| 11           | CMP/CMPB | 2                 | D - A                           | 3      | 10                  |

|              | DJNŽ     | 1                 | Decrement & JNZ                 | 3      | 9/12                |

| 11           | EXTB     | 1                 | Sign Extend Byte                | 2      | 7                   |

| П            | JBC      | 0                 | Jump if bit clear               | 3      | 10/13               |

|              | JBS      | 0                 | Jump if bit set                 | 3      | 10/13               |

| 11           | JC       | 0                 | Jump if Carry Set               | 2      | 5/8                 |

|              | JNC      | 0                 | Jump if no carry                | 2      | 5/8                 |

| П            | JΕ       | 0                 | Jump if =                       | 2      | 5/8                 |

|              | JNE      | 0                 | Jump if not =                   | 2      | 5/8                 |

| Н            | JGT      | 0                 | Jump if >                       | 2      | 5/8                 |

|              | JGE      | 0                 | Jump if >=                      | 2      | 5/8                 |

| Ш            | JLE      | 0                 | Jump if < or =                  | 2      | 5/8                 |

| Ш            | JLT      | 0                 | Jump if <                       | 2      | 5/8                 |

| Ш            | JV       | 0                 | Jump if Overflow                | 2      | 5/8                 |

| H            | JNV      | 0                 | Jump if no overflow             | 2      | 5/8                 |

| H            | јн       | 0                 | Jump if higher                  | 2      | 5/8                 |

| П            | JNH      | 0                 | Jump if not higher              | 2      | 5/8                 |

| Ш            | LCALL    | 0                 | Long Call                       | 3      | 11                  |

|              | LD/LDB   | 2                 | Load                            | 3      | 10                  |

| $\mathbf{H}$ | MUL      | 3                 | $D \leftarrow A * B$            | 5      | 33                  |

| Н            | NOP      | 0                 | NO Operation                    | 1      | 2                   |

| Н            | OR/ORB   | 2                 | D ← D OR A                      | 3      | 10                  |

| Н            | XOR/XORB | 2                 | D ← D XOR A                     | 3      | 10                  |

| П            | PUSHF    | 0                 | Push PSB                        | 1      | 5                   |

| Н            | POPF     | 0                 | Pop PSB                         | 1      | 5                   |

| Ш            | RET      | 0                 | Return                          | 1      | 10                  |

| Н            | SHL/SHLB | 1                 | Shift Left                      | 3      | 11 + N <sup>3</sup> |

| H            | SHLL     | 1                 | Shift Left Long                 | 3      | 15 + N <sup>3</sup> |

|              | SHR/SHRB | 1                 | Shift Right                     | 3      | 11 + N <sup>3</sup> |

|              | SHRL     | 1                 | Shift Right Long                | 3      | $15 + N^3$          |

|              | SHRA     | 1                 | Arith. Right Shift              | 3      | $10 + N^3$          |

|              | SHRAL    | 1                 | Arith. Right Long               | 3      | 15 + N <sup>3</sup> |

|              | SJMP     | 0                 | Short Jump                      | 2      | 7                   |

|              | LJMP     | 0                 | Long Jump                       | 3      | 9                   |

|              | ST/STB   | 2                 | Store to Memory                 | 3      | 13 <sup>4</sup>     |

|              | SUB/SUBB | 2                 | B ← B – A                       | 3      | 10                  |

| Ш            | SUB/SUBB | 3                 | B ← B − A<br>D ← B − A          | 3<br>4 | 10                  |

| 1            | ·        | r immediate words | U ← D − A                       | 4      | 10                  |

NOTE 1: Add one for immediate words.

NOTE 2: Add 9 for indirect mode and 2 or 0 for immediate mode—see table. (Cycle times @ 1.02 ns) for 19.6608 MHz crystal or 68 ns for 29.4916 MHz crystal )

NOTE 3: N is number of bit shifts.

NOTE 4: Indirect Mode.

Table 4. Instruction Set

## REGISTER DESCRIPTION

This section contains a description of each of the registers in the MAC II device. All of the registers of the device are 8-bits with 16-bit addresses. The registers are made up of bits that are either inputs or outputs. Input bits are read-only (RO). Output bits are read/write (R/W). The state of an output may be read back by the processor.

## Serial Mode

In parallel mode (CONF = 0) the functions of the UART registers are exactly the same as those in 16C450 UART. However in serial mode, (CONF = 1), the UART is turned around and controlled by the internal processor and it becomes a data set UART. The DTR, RTS, and OUT1 in MCR register becomes DSR, CTS, and RLSD outputs. The CTS, DSR in MSR register become RTS, DTR input status from RTS, DTR pins.

#### Note:

In serial version to echo SIN to SOUT after RESET and then go back to normal operation.

- 1. Set SB in LCR to "1".

- Sample RDI in UART monitor register.

- 3. Set CM = RDI in the same register.

- SOUT will be the same state as CM.

- Receiver is functioning, ignoring it.

- After finishing all echoing, reset SB in LCR.

- Update DLL, DLM, and set CM = 1 for normal operation.

- Do a SET then RESET to RTRST bit to RESET RCV and TMR. Do a READ to LSR to clear LSR.

- The UART is ready for normal operation.

Echo can be hardware selected by setting GCR1 bit 2. If selected omit step 3.

| ADDRESS     | FUNCTION        | R/W | BYTES  | COMMENTS |

|-------------|-----------------|-----|--------|----------|

| 0000H-017FH | Internal RAM *  | R/W | 384    | (a)      |

| 0180H-019AH | Internal REG*   | R/W | 24     | (b)      |

| 0200H-027FH | External MAP    | R/W | 128    | (c)      |

| 0280H-02FFH | External EEPROM | R/W | 128    | (c)      |

| 0300H-7FFFH | External RAM    | R/W | 31.25K | (d)      |

| 8000H-FFFFH | External ROM    | RO  | 32K    | (e)      |

- 0000H 00FFH may be accessed using direct addressing mode. 0100 01A9H may only be accessed as memory locations (16-bit address) in an indirect mode. For direct addressing a 9th bit (GCR [1], called Page Bit) must be set to switch from the first 256 bytes to the rest of the RAM.

- (a) The SC11011,61 have 304 bytes and SC11021 has 320 bytes

- (b) The internal register is compatible with the SC11011 and SC11021.

- (c) In the normal mode of operation, the MCS and ECS chip select for MAP and EERAM remain the same as in MAC or Big MAC. A provision is made to extend the ROM capacity by another 32K bytes. If selected, the ECS pin becomes a chip select to address another 32K ROM bank from 8000H to FFFFH. MCS pin and an external memory decoder with MA7 must be used to select either the MAP or the EEPROM.

- (d) The external RAM address has a maximum addressable space of 31.25K.

- (e) The 32K bytes ROM address remains the same as in SC11011 and SC11021. With the ECS pin, the ROM address is expanded to a total of 64K bytes.

- (f) SC11011, 1102X, 11061 stack is reset to 302 on power up. MAC II stack is reset to

| Location | Name  | PC address | 7      | 6       | 5      | 4      | 3      | _ 2 _  | 1      | 0       |

|----------|-------|------------|--------|---------|--------|--------|--------|--------|--------|---------|

| 180H     | RBR   | 0 (DLAB≈0) | DATA.7 | DATA.6  | DATA.5 | DATA.4 | DATA.3 | DATA.2 | DATA.1 | DATA.0  |

| 18AH     | THR   | 0 (DLAB=0) | DATA.7 | DATA.6  | DATA.5 | DATA.4 | DATA.3 | DATA.2 | DATA.1 | DATA.0  |

| 181H     | IER   | 1 (DLAB=0) | 0      | 0       | 0      | 0      | EDSSI  | ELSI   | ETBEI  | ERBFI   |

| 182H     | IIR   | 2          | 0      | 0       | 0      | 0      | 0      | ID.1   | ID.0   | PENDING |

| 183H     | LCR   | 3          | DLAB   | SET BRK | PARITY | EPS    | PEN    | STB    | WLS1   | WLS0    |

| 184H     | MCR   | 4          | 0      | 0       | 0      | LOOP   | OUT2   | OUT1   | RTS    | DTR     |

| 185H     | LSR   | 5          | 0      | TEMT    | THRE   | BI     | FE     | PE     | OE     | DR      |

| 186H     | MSR   | 6          | DCD    | RL      | DSR    | CTS    | DDCD   | TERI   | DDSR   | DCTS    |

| 187H     | STR   | 7          | BIT7   | BIT6    | BIT5   | BIT4   | BIT3   | BIT2   | BIT1   | BITO    |

| 188H     | DLL   | _          | BIT7   | BIT6    | BIT5   | BIT4   | BIT3   | BIT2   | BIT1   | BITO    |

| 189H     | DLM   | _          | BJT15  | BIT14   | BIT13  | BIT12  | BIT11  | BIT10  | BIT9   | BIT8    |

| 18BH     | UMR   |            | RTRST  | СМ      | RDI    | DLF    | LCF    | TXF    | RXF    | MCF     |

| 1A8H     | SHDLL | 0 (DLAB=1) | BIT7   | BIT6    | BIT5   | BIT4   | BIT3   | BIT2   | BIT1   | BIT0    |

| 1A9H     | SHDLM | 1 (DLAB=1) | BIT15  | BIT14   | BIT13  | BIT12  | BIT11  | BIT10  | BIT9   | BIT8    |

Table 2a. SC11031 UART Registers

| Location | Name | 7          | 6               | 5              | 4               | 3       | 2         | 1        | 0        |

|----------|------|------------|-----------------|----------------|-----------------|---------|-----------|----------|----------|

| 18CH     | STBR | DATA.3     | DATA.2          | DATA.1         | DATA.0          | ASYNC   | SSCC      | ENABLE   | PENDING  |

| 18DH     | SWP  |            | 56              | S5             | S4              | 53      | 25        | S1       | S0       |

| 18EH     | DIR  | DIR7       | DIR6            | DIR5           | DIR4            | DIR3    | DIR2      | DIR1     | DIR0     |

| 18FH     | DAR  | DAR7       | DAR6            | DAR5           | DAR4            | DAR3    | DAR2      | DAR1     | DAR0     |

| 190H     | GCR  | CONF       | ОН              | KDV            | MRDY            | AA      | HS        | PAGE     | TIMER    |

| 191H     | TIM  | RAM 32K    | _               | _              | _               |         |           |          | TFF0     |

| 192H     | PSB  | PD         |                 | IP             | IE              | Z       | N         | С        | V        |

| 193H     | ICR  | EXT ENABLE | TIMER<br>ENABLE | RING<br>ENABLE | UART<br>ENABLE  | EXT INT | TIMER INT | RING INT | UART INT |

| 194H     | GCR1 | TEST       | ROMBANK         | EA             | ROMBANK<br>CONF | XUART   | HW ECHO   | FAST ROM | FREQ SEL |

| 195H     | GCR2 | RI         | CKOUT           | RC CAL         | RC SEL          | RC      | DIV.2     | DIV.1    | DIV.0    |

| 196H     | GCR3 | SIN        | SOUT            | V.23 OUT       | V.23 SEL        |         | -         | -        | -        |

Table 2b. SC11031 Internal Registers

| Location | Name | PC address | 7      | 6       | 5      | 4      | 3      | 2      | 1      | 0       |

|----------|------|------------|--------|---------|--------|--------|--------|--------|--------|---------|

| 180H     | RBR  | 0 (DLAB=0) | DATA.7 | DATA.6  | DATA.5 | DATA.4 | DATA.3 | DATA.2 | DATA.1 | DATA.0  |

| 18AH     | THR  | 0 (DLAB=0) | DATA.7 | DATA.6  | DATA.5 | DATA.4 | DATA.3 | DATA.2 | DATA.1 | DATA.0  |

| 181H     | IER  | 1 (DLAB=0) | 0      | 0       | 0      | 0      | EDSSI  | ELSI   | ETBEI  | ERBFI   |

| 182H     | IIR  | 2          | 0      | 0       | 0      | 0      | 0      | ID.1   | ID.0   | PENDING |

| 183H     | LCR  | 3          | DLAB   | SET BRK | PARITY | EPS    | PEN    | STB    | WLS1   | WLS0    |

| 184H     | MCR  | 4          | 0      | 0       | 0      | LOOP   | OUT2   | OUT1   | RTS    | DTR     |

| 185H     | LSR  | 5          | 0      | TEMT    | THRE   | BI     | FE     | PE     | OE     | DR      |

| 186H     | MSR  | 6          | DCD    | Ri      | DSR    | CTS    | DDCD   | TERI   | DDSR   | DCTS    |

| 187H     | STR  | 7_         | BIT7   | BIT6    | BIT5   | BIT4   | BIT3   | BIT2   | BIT1   | BITO    |

| 188H     | DLL  | 0 (DLAB=1) | BIT7   | BIT6    | BIT5   | BIT4   | BIT3   | BIT2   | BIT1   | BIT0    |

| 189H     | DLM  | 1 (DLAB=1) | BIT15  | BIT14   | BIT13  | BIT12  | BIT11  | BIT10  | BIT9   | BIT8    |

| 18BH     | UMR  | _          | RTRST  | СМ      | RDI    | DLF    | LCF    | TXF    | RXF    | MCF     |

Table 3a. SC11040 UART Registers

| Location | Name | 7          | 6               | 5              | 4               | 3       | 2         | 1        | 0        |

|----------|------|------------|-----------------|----------------|-----------------|---------|-----------|----------|----------|

| 18CH     | STBR | DATA.3     | DATA.2          | DATA.1         | DATA.0          | ASYNC   | SSCC      | ENABLE   | PENDING  |

| 18DH     | SWP  | _          | S6              | S5             | S4              | 53      | S2        | S1       | 50       |

| 18EH     | DIR  | -          | -               | RC CAL         | RC SEL          | DIR3    | DIR2      | DIR1     | DIR0     |

| 18FH     | DAR  | SIN        | SOUT            | V23 OUT        | V23 SEL         | DAR3    | DAR2      | DAR1     | DAR0     |

| 190H     | GCR  | CONF       | ОН              | KDV            | MRDY            | AA      | HS        | PAGE     | TIMER    |

| 191H     | TIM  | RAM 32K    |                 | _              | _               | _       | _         | _        | TFF0     |

| 192H     | PSB  | PD         | _               | IP             | IE              | Z       | N         | С        | v        |

| 193H     | ICR  | EXT ENABLE | TIMER<br>ENABLE | RING<br>ENABLE | UART<br>ENABLE  | EXT INT | TIMER INT | RING INT | UART INT |

| 194H     | GCR1 | TEST       | ROMBANK         | EA             | ROMBANK<br>CONF | XUART   | HW ECHO   | FAST ROM | FREQ SEL |

Table 3b. SC11040 Internal Registers

## **UART REGISTERS**

## UART Interrupt Enable Register (IER), location 181H

The 8-bit register enables the four types of interrupts of the UART to separately activate the chip interrupt (INTRPT) output signal. It is possible to totally disable the interrupt system by resetting bits 0 through 3 of the Interrupt Enable Register. Similarly, by setting the

appropriate bits of this register to a logic 1, selected interrupts can be enabled. Disabling the interrupt system inhibits the Interrupt Identification Register and the active (high) INTRPT output from the chip. All other system functions operate in their normal manner, in-

cluding the setting of the Line Status and MODEM Status Registers. The contents of the Interrupt Enable Register are indicated in Table 9 and are described below. IER and IIR should be used as Read Only in Parallel Configuration.

| Bit Number | Bit Name | Description                                                                            |

|------------|----------|----------------------------------------------------------------------------------------|

| 4-7        |          | These four bits are always logic 0.                                                    |

| 3          | EDSSI    | This bit enables the MODEM Status Interrupt when set to logic 1.                       |

| 2          | ELSI     | This bit enables the Receiver Line Status Interrupt when set to logic 1.               |

| 1          | ETBEI    | This bit enables the Transmitter Holding Register Empty Interrupt when set to logic 1. |

| 0          | ERBFI    | This bit enables the Received Data Available Interrupt when set to logic 1.            |

## Interrupt Identification Register (IIR, location 182H)

The UART has on-chip interrupt capability that allows for flexibility in interfacing popular micro-processors presently available. In order to provide minimum software overhead during data character transfers, the UART prioritizes interrupts into four levels. The four levels of interrupt conditions are as follows: Receiver Line Status (pri-

ority 1); Received Data Ready (priority 2); Transmitter Holding Register Empty (priority 3); and MODEM status (priority 4).

Information indicating that a prioritized interrupt is pending and the type of that interrupt are stored in the Interrupt Identification Register (IIR). When addressed during chip-select time, the IIR freezes the highest priority interrupt pending and no other interrupts change the IIR, even though they are recorded, until the particular interrupt is serviced by the CPU. The contents of the IIR are indicated in Table 9 and are described on the next page.

| Bit Number | Bit Name | Description                                                                                                                                                                                                                                                                                                                                              |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3–7        |          | These five bits of the IIR are always logic 0.                                                                                                                                                                                                                                                                                                           |

| 1-2        | ID0-ID1  | These two bits of the IIR are used to identify the highest priority interrupt pending as indicated in Table 9.                                                                                                                                                                                                                                           |

| 0          | PENDING  | This bit can be used in either a hardwired prioritized or polled environment to indicate whether an interrupt is pending. When bit 0 is a logic 0, an interrupt is pending and the IIR contents may be used as a pointer to the appropriate interrupt service routine. When bit 0 is a logic 1, no interrupt is pending and polling (if used) continues. |

## Line Control Register (LCR), location 183H

The system programmer specifies the format of the asynchronous data communications exchange via the Line Control Register. In addition to controlling the format, the programmer may retrieve the contents of the Line Control Register for inspection. This feature simplifies system programming and eliminates the need for separate storage in system memory of the line characteristics. The contents of the Line Control Register are indicated in Table 6 and are described in the following table.

| Bit Number | Bit Name | Description                                                                                                                                                                                                                                                                                          |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | DLAB     | This bit is the Divisor Latch Access Bit (DLAB). It must be set high (logic 1) to access the Divisor Latches of the Baud Generator during a Read or Write operation. It must be set low (logic 0) to access the Receiver Buffer, the Transmitter Holding Register, or the Interrupt Enable Register. |

| 6          | SET BRK                                        | is forced to                                                  | the Spacir                             | ng (logic 0) state. The                                                   | s set to a logic 1, the serial output (SOUT)<br>break is disabled by setting bit 6 to a logic<br>and has no effect on the transmitter logic.                                                                                      |

|------------|------------------------------------------------|---------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                                                | tions system                                                  | m. If the                              |                                                                           | ert a terminal in a computer communica-<br>is followed, no erroneous or extraneous<br>the break.                                                                                                                                  |

|            |                                                | <ol> <li>You mu</li> <li>Set SET</li> <li>Wait for</li> </ol> | BRK bit.                               | r TEMT.<br>mined time and then                                            | clear SETBRK bit.                                                                                                                                                                                                                 |

|            |                                                | During the establish th                                       |                                        |                                                                           | e used as a character timer to accurately                                                                                                                                                                                         |

| 5          | PARITY                                         | transmitted                                                   | l and chec                             |                                                                           | s 3, 4 and 5 are logic 1 the Parity bit is<br>s a logic 0. If bits 3 and 5 are 1 and bit 4 is<br>as a 1.                                                                                                                          |

| 4          | EPS                                            | odd numbe                                                     | er of logic 1<br>is a logic 1          | ls is transmitted or ch                                                   | n bit 3 is a logic 1 and bit 4 is a logic 0, an<br>ecked in the data word bits and Parity bit.<br>an even number of logic 1s is transmitted                                                                                       |

| 3          | PEN                                            | (transmit d<br>of the seria                                   | ata) or che<br>l data. (Tl             | cked (receive data) b                                                     | it 3 is a logic 1, a Parity bit is generated<br>etween the last data word bit and Stop bit<br>to produce an even or odd number of 1s<br>t are summed.)                                                                            |

| 2          | STB                                            | logic 0, one<br>5-bit word l<br>logic 1 wh                    | Stop bit i<br>length is s<br>en either | s generated in the tra<br>elected via bits 0 and<br>a 6-, 7-, or 8-bit wo | in each transmitted character. If bit 2 is a<br>unsmitted data. If bit 2 is a logic 1 when a<br>1, two Stop bits are generated. If bit 2 is a<br>ord length is selected, two Stop bits are<br>unmed number of Stop-bits selected. |

| 0 and 1    | WLS0, WLS1                                     |                                                               |                                        | fy the number of bit<br>ing of bits 0 and 1 is a                          | s in each trans-mitted or received serial as follows:                                                                                                                                                                             |

|            |                                                | Bit 1                                                         | Bit 0                                  | Word Length                                                               |                                                                                                                                                                                                                                   |

|            |                                                | 0                                                             | 0                                      | 5 Bits                                                                    |                                                                                                                                                                                                                                   |

|            |                                                | 0<br>1                                                        | 1<br>0                                 | 6 Bits<br>7 Bits                                                          |                                                                                                                                                                                                                                   |

|            |                                                | 1                                                             | 1                                      | 8 Bits                                                                    |                                                                                                                                                                                                                                   |

| Modem Con  | trol Register (MCR),                           | location 18                                                   | 34H                                    |                                                                           |                                                                                                                                                                                                                                   |

|            | ister controls the inter-<br>MODEM or data set |                                                               |                                        | evice emulating a<br>ntents of the MO-                                    | DEM Control Register are indicated in Table 6 and are described below.                                                                                                                                                            |

| Bit Number | Bit Name                                       | Descriptio                                                    | n                                      |                                                                           |                                                                                                                                                                                                                                   |

| Bit Number | Bit Name | Description                                |

|------------|----------|--------------------------------------------|

| 5–7        |          | These bits are permanently set to logic 0. |

| "          |          |                                            |

| 4                                             | LOOP                                                               | This bit provides a local loopback feature for diagnostic testing of the UART. When bit 4 is set to logic 1, the following occur: the transmitter Serial Output (SOUT) is set to the Marking (logic 1) state; the receiver Serial Input (SIN) is disconnected; the output of the Transmitter Shift Register is "looped back" into the Receiver Shift Register input: the four MODEM Status Register bits CTS, DSR, DCD and RI are disconnected internally; and the four MODEM Control Register bits DTR, RTS OUT1 and OUT2 are internally connected to the four MODEM Status Register inputs, and the MODEM Control output pins RLSD, CTS, DSR are forced to the inactive state (high). In the diagnostic mode, data that is transmitted is immediately received. This feature allows the processor to verify the transmit and received-dated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                               |                                                                    | paths of the UART.  In the diagnostic mode, the receiver and transmitter interrupts are fully operational. The MODEM Control Interrupts are also operational, but the interrupts' sources are now the lower four bits of the MODEM Control Register instead of the four MODEM Control inputs. The interrupts are still controlled by the Interrupt Enable Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3                                             | OUT2                                                               | Auxiliary user-designated bit. It is connect to $MSR[7]$ (DCD) during local loopback When Out2 = 0, INTO pin is Hi-Z.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2                                             | OUT1                                                               | Auxiliary user-designated bit. It is connected to MSR[6] (RI) during local loopback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1                                             | RTS                                                                | This bit controls the Request to Send (RTS) output. Bit 1 affects the RTS output in a manner identical to that described above for bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0                                             | DTR                                                                | This bit controls the Data Terminal Ready (DTR) output. When bit 0 is set to a logic 1, the DTR output is forced to a logic 0. When bit 0 is reset to a logic 0, the DTI output is forced to a logic 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |